Maximum frequency attained till date-

Multiplexers - 178.348 Mhz

Register File - 598.498 Mhz

Data Memory- 274.72 Mhz

Datapath- 112.215 Mhz

Top Module- 119.97 Mhz

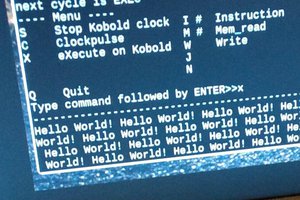

Fetching and Executing instruction each take single clock cycle.

Fetching cycles had AluOp as XXXX and result too as XXXX

The next cycle is the result of the fetched instruction and Reg-write or memory write is procesed at the fall of the clock cycle.

Register R0 always contains zero although it can be changed and overwritten by any instruction. However it isn't suggested. MIPS procesors have R0 set as zero. The Mux with input from Register and sign extend also has an input zero incase R0 is overwritten and one needs to use. Hence its select line in of 2 bits.

Shashi Suman

Shashi Suman

Stefan

Stefan

Dylan Brophy

Dylan Brophy

When I implement the RISC top Mopdule. It shows the following errors-:

[Place 30-494] The design is empty

Resolution: Check if opt_design has removed all the leaf cells of your design. Check whether you have instantiated and connected all of the top level ports.

[Common 17-69] Command failed: Placer could not place all instances

Kindly please tell me that how to rectify this error asap because this is my final year project