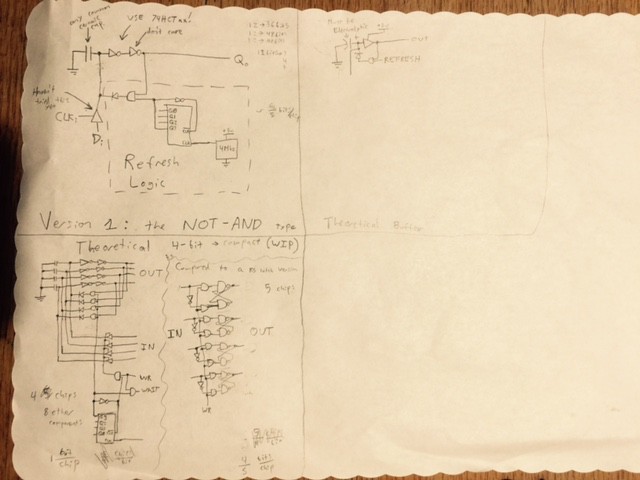

I came up with some schematics and ideas during dinner tonight. They include the design I already tried, a hypothetical design, and another design that for some reason doesn't work.

The schematic to the top left is a tested and working design, but is horribly inefficient as far as chip usage goes. Im looking for better designs (More about that in a moment). The one below it is practically guaranteed to work. The one to the right, for some weird reason, does not work. I used 4Mhz because it was easy just lying around.

So basically I need mass capacitor storage. Like what Yann Guidon / YGDES suggested. He suggested that I use capacitors + 2 diodes to - what it looks to me like - "address" the capacitors and write/read to the ones that are selected. I have been messing around with this but haven't had any success. Bummer because it would actually be cool to use this kind of DRAM in my #SBP-CPU (Slice Based Processor) project. I'm going to keep trying though so hopefully I can solve it and mass store data in capacitors. Sweet!

Dylan Brophy

Dylan Brophy

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.

I'd recommend you to use ICs if you process with ICs :-D

you'll get a lot of troubles for a ridiculously low density and terrible speed...

Are you sure? yes | no