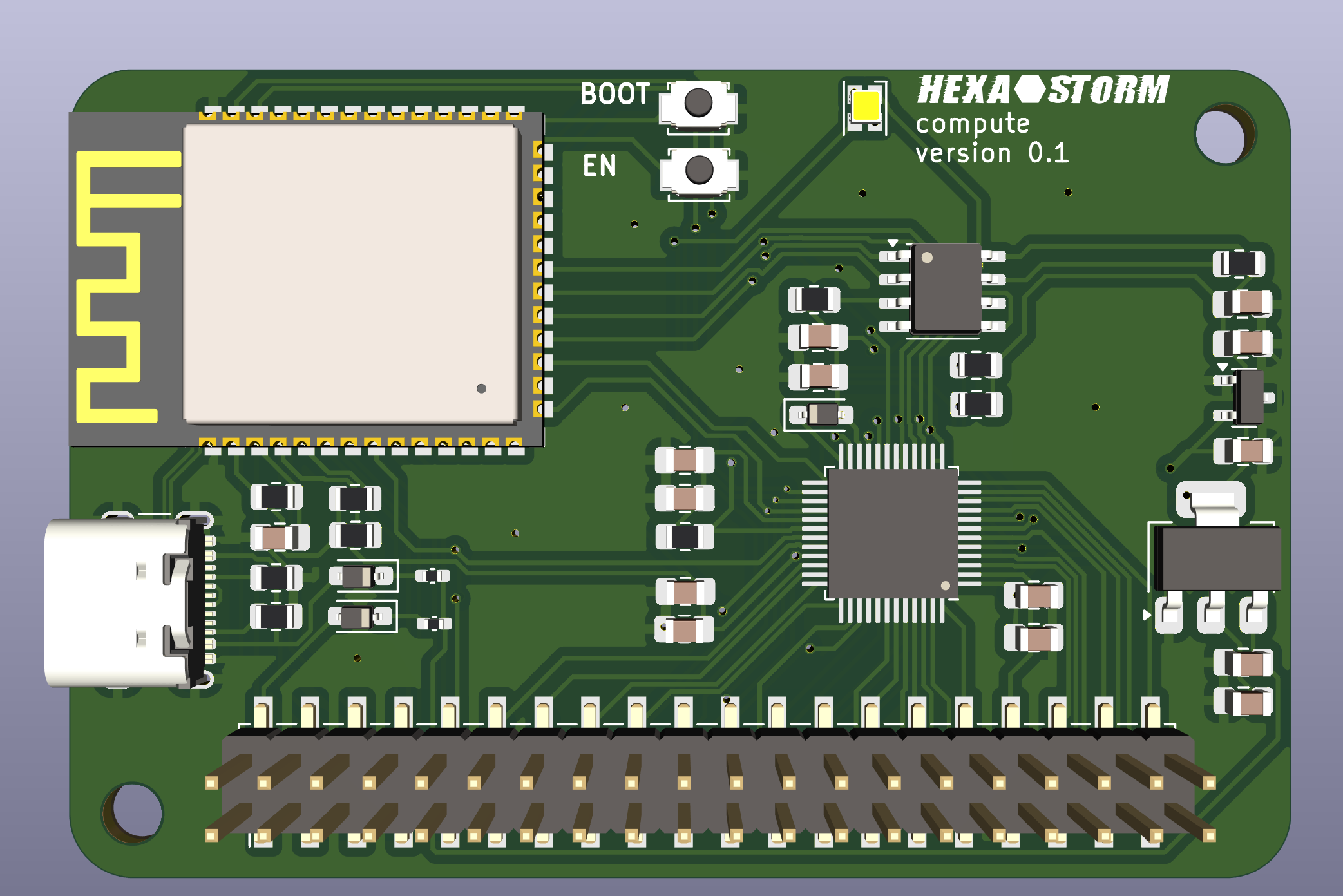

I have initiated the next design cycle. The core component is the compute module, housing an ESP32 microcontroller and a UP5K FPGA. It's equipped with a reset/boot switch and a single control LEDs for the ESP32 and FPGA. A small memory module dedicated to storing the FPGA bootloader is also integrated. The ICE V module loads the FPGA directly from the ESP32. I keep it , as I might want to use this memory as a buffer for storing instructions to the laserhead. Board is 2 layer with mostly SMT components to keep costs low.

NOTE: LilyGO T-FPGA ESP32-S3 is an interesting alternative but it is not fully supported by https://github.com/YosysHQ/apicula

Hexastorm

Hexastorm

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.