CURRENT DEV STATUS:

In this development log the mixed protocol interconnect functionality is demonstrated in simulation.

First, a custom AXI SPI component was developed that enables the control of an SPI Master. The development of this component was necessary in order to simplify the overall design without the use of the Xilinx SPI IP as well as to integrate, inside the custom component, functions necessary for the correct packet communication. interface through the AXI bus protocol.

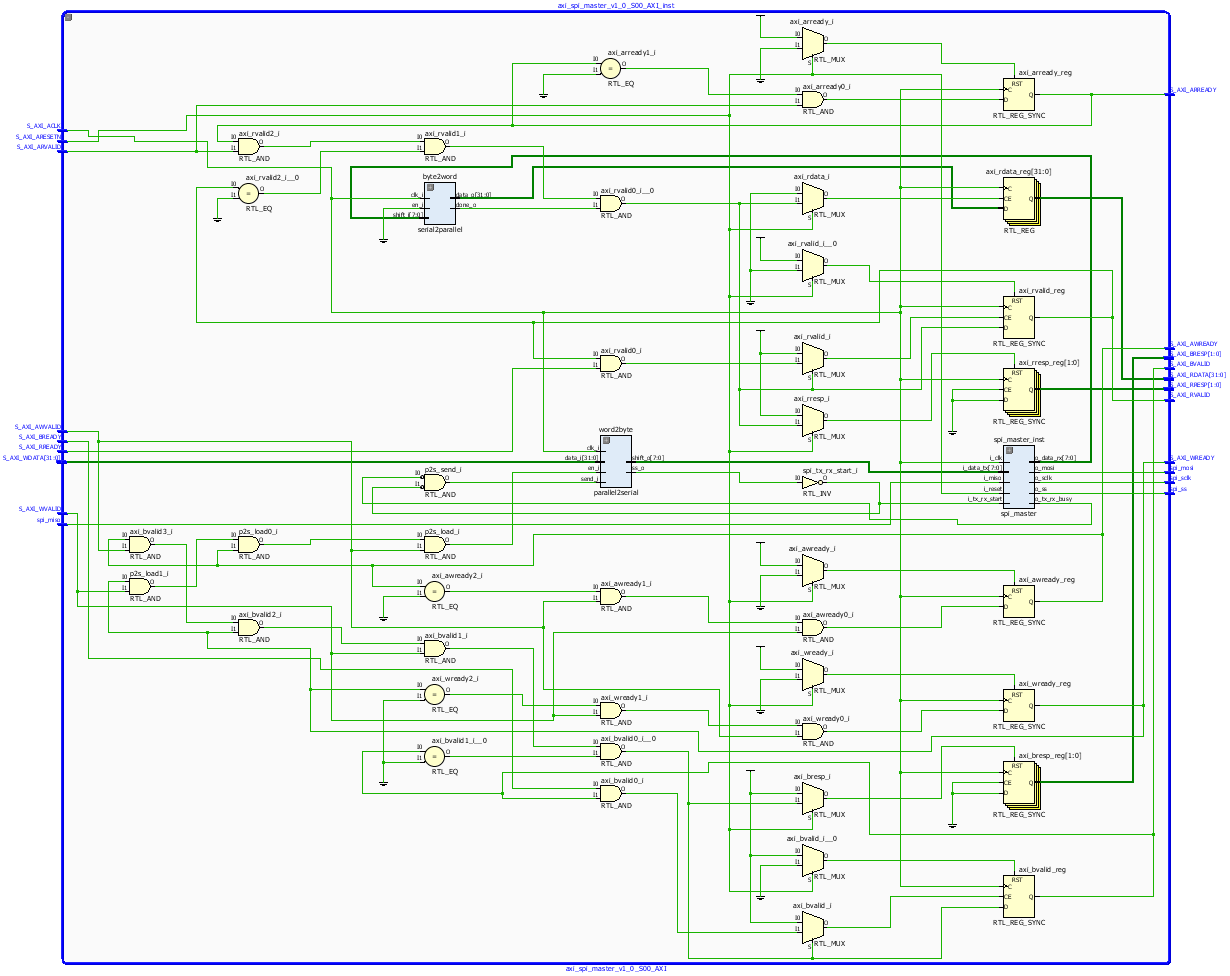

The developed component's RTL architecture is presented below:

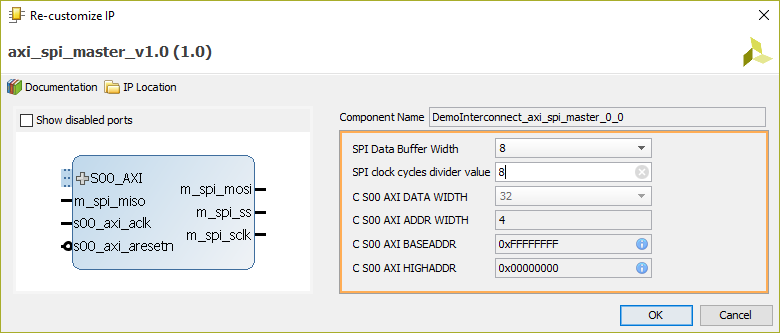

The component can be configured through the following parameters:

At the current development stage there AXI addresses are ignored. Any incoming AXI write requests are carried out as SPI Master transmissions and any AXI read requests are carried out as SPI Master receptions. In the future addresses could be used to dynamically specify the CLK divider value as well as the CPOL / CPHA configuration of the SPI.

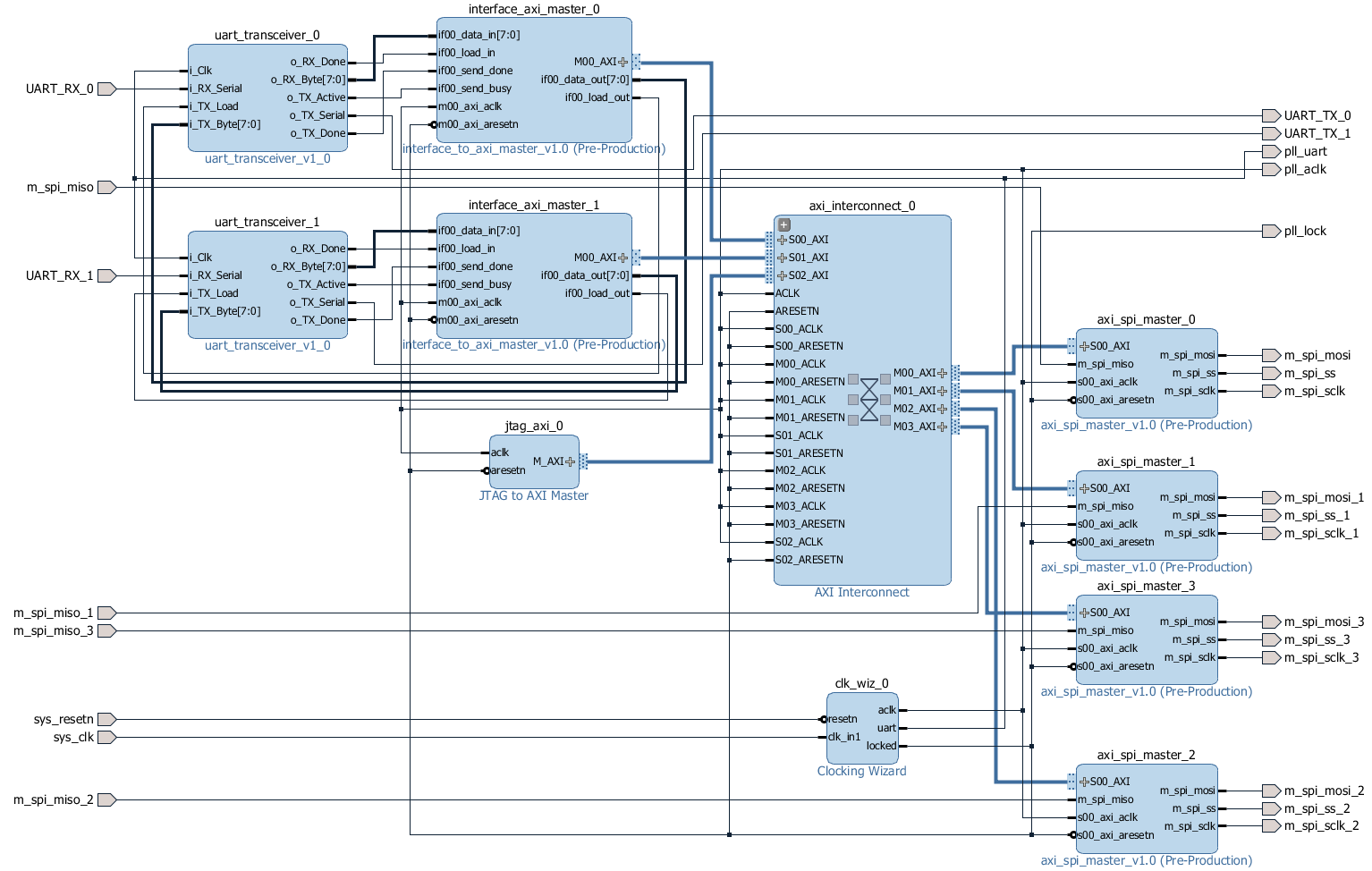

The replacement of the Xilinx SPI component changed the overall demo design into the following architecture:

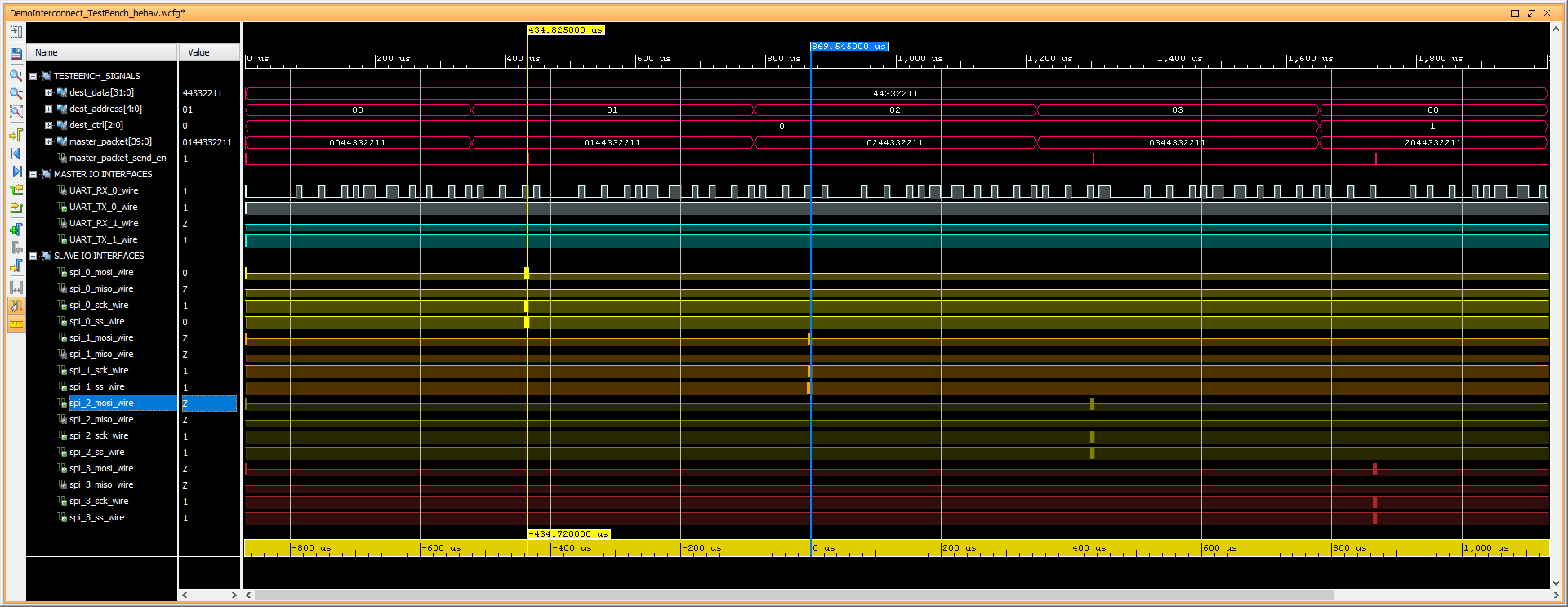

Finally the full functionality of the developed design was demonstrated in a developed test-bench. The test-bench drives the UART_RX_0 port as if a master device (i.e. Arduino) was connected to the interface UART_RX_0/UART_TX_0 and was transmitting a 40-bit mockup packet with 32-bit data ("0x44332211") at a constant rate with destination, a slave device connected to each of the axi_spi_master_x SPI interfaces. Each time the transmission was complete a new packet was sent to a different slave device.

The demo system achieved a peak throughput of 9.2 kBps. The interfaces where configured at:

- UART Baud-rate: 115200

- SPI sclk: 6.25 MHz

The figure below is exported from Vivado 2016.4 and presents the simulation results of the demo test-bench system.

In the figure above the time it takes for a 40-bit packet carrying 32-bit values to be successfully transmitted from a UART master device to an SPI slave device is marked between the yellow/blue markers and 434.72 us.

Furthermore, as in the figure it is clearly demonstrated the concept of the mixed protocol interconnect since a UART master device can address and transmit data successfully to each SPI slave device connected to the respective interfaces.

COMING UP NEXT....

- Develop Master - to - Master communication scheme and present simulation results.

- Develop IP component to provide JTAG access for configuring different parameters of the master/slave interfaces, i.e. baud-rate, spi clock divider etc.

Lefteris Kyriakakis

Lefteris Kyriakakis

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.