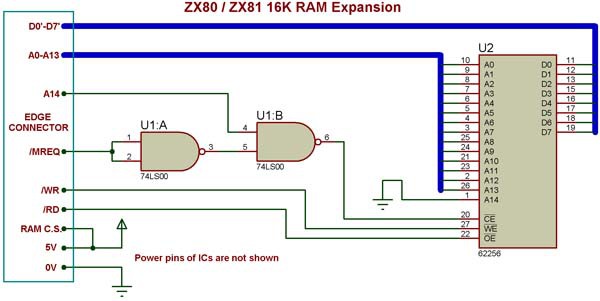

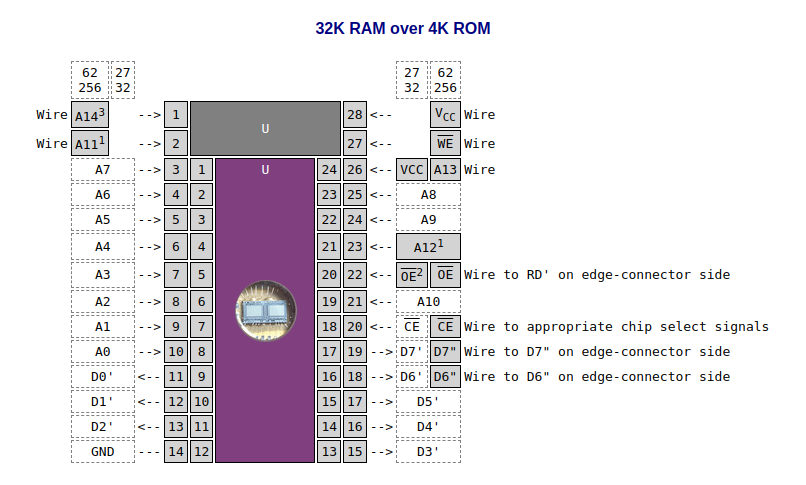

The circuit diagram is from the Maplin magazine issue.

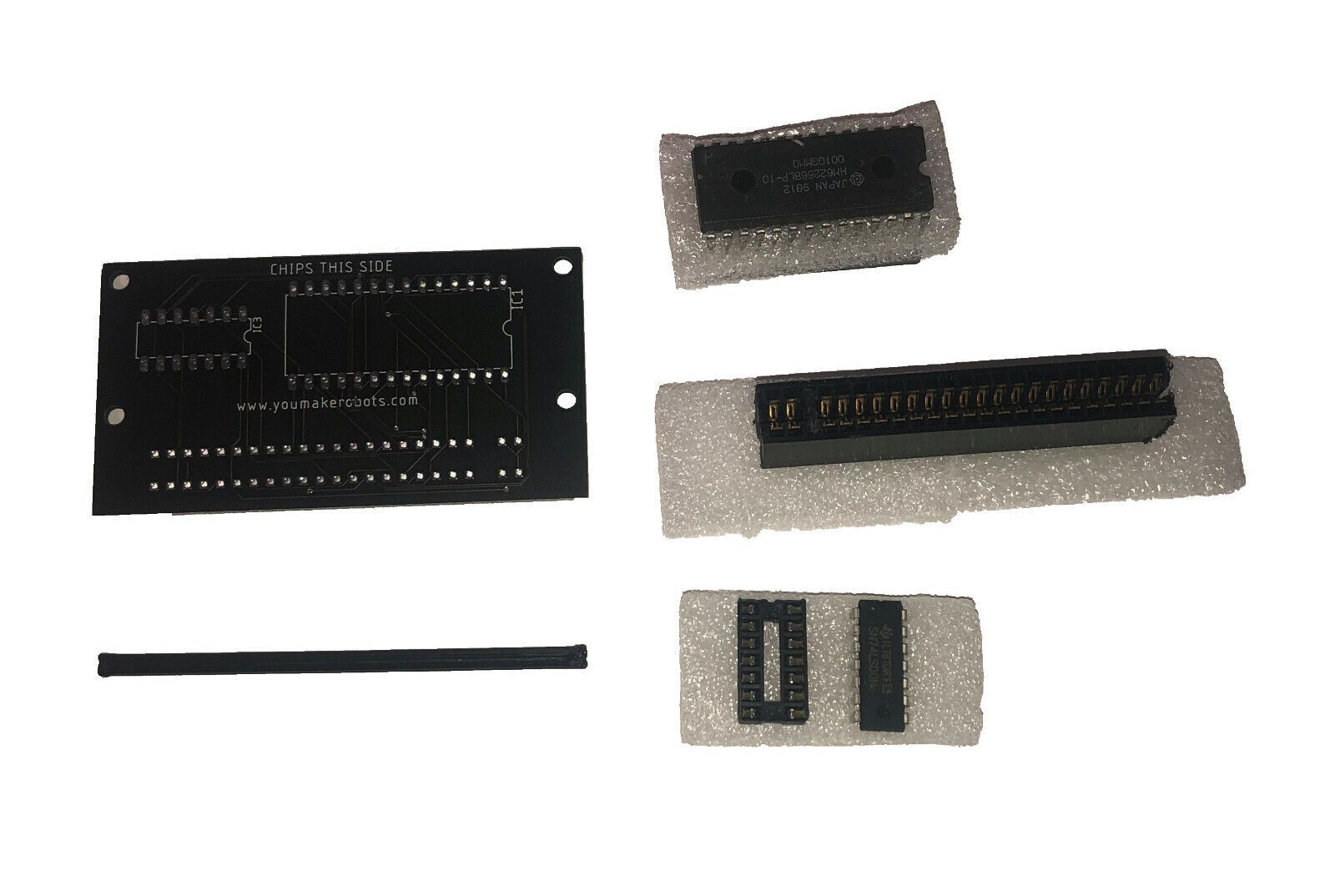

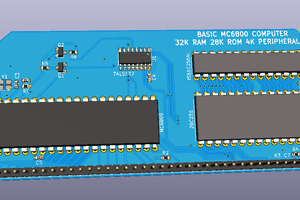

The board I have was a kind and generous gift from the designer, and differs from the Maplin circuit. It uses a 74LS125 chip instead of a 74LS03 for IC3, and a 74LS02 instead of a 74LS32 for IC6. This allows it to work with just one pull-up resistor instead of two. My board has some of the gates swapped, which is important when adding hacks to it.

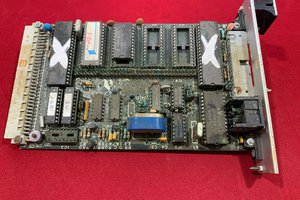

I pulled the parts off to record the PCB tracks under the chips, and to socket the chips so I could partly replace them with PAL chips. Alas, this has caused it to stop working! :-(

Removing a short circuit allowed the piggy-pack RAM to work again, but hasn't got the graphics working again. I don't know whether to bother repairing this one or getting some new boards made. We know the circuit works, and the RAM chip circuit works, so it is not risking a load of dud boards.

Keith

Keith

Gee Bartlett

Gee Bartlett

Colin Maykish

Colin Maykish