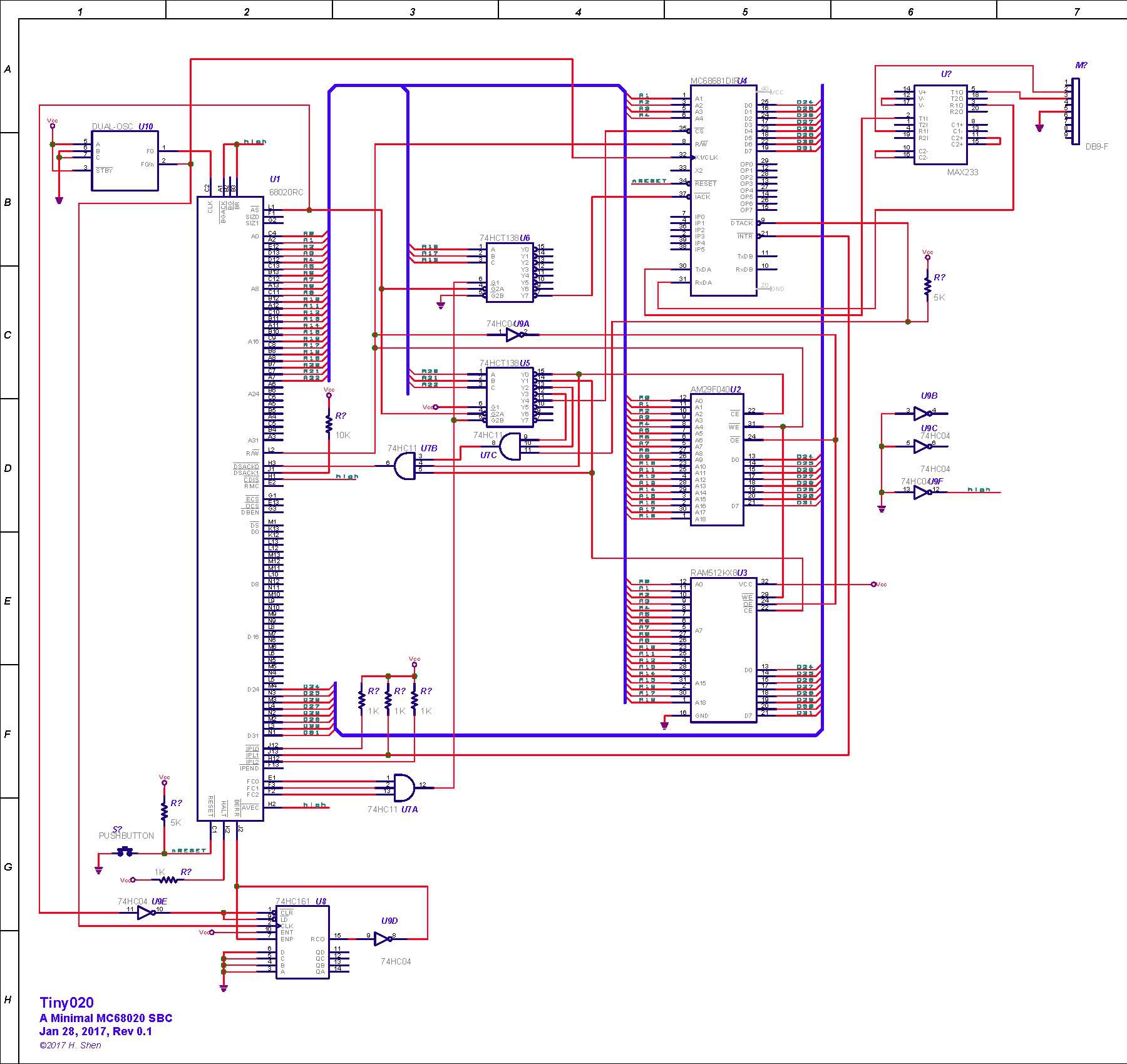

Motorola has published an apnote, AN1015, describing a minimum 68020 system. Looking at it with today's better components, the appnote called for more parts & greater complex than is really necessary. I would rather do without PLD or CPLD--it tends to muddle up the design concept, and a through-hole design is easier to build, study and revise. The first iteration is just the CPU, flash, RAM, DUART and few TTL logic, about $30 of parts plus a prototype board. The basic design has room for a floating point coprocessor, two more memories or I/O which can be added later.

68020 instruction set is a superset of the 68000 instructions, so EASy68K tool chain is more than adequate to build a working system. The coprocessor instructions, when I get there, can be dealt using macros. My goal is to make a simple 68020 SBC that uses EASy68K trap services.

The schematic is a simplified version of AN1015.

Plasmode

Plasmode

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.