This project was started over 3 years ago when I wanted to interface my Digilent Nexys 2 board with an LCD screen I saw on Sparkfun. it worked but it bothered me that starting an FPGA project was a huge undertaking. I wanted the process of adding a new device to be analogous to the Arduino ecosystem. Where trying out a new idea was as easy as downloading some code and adding small tweaks to make it fit into your design. I am so impressed with what artist and other hobbyists have done with a small MCU as the Arduino, I believe that if I could offer an FPGA development environment with similar capabilities then instead of projects consisting of LEDs and accelerometers we would see high functioning robots with vision pipelines.

Nysa was born (actually I called it Sycamore at first, then Olympus)

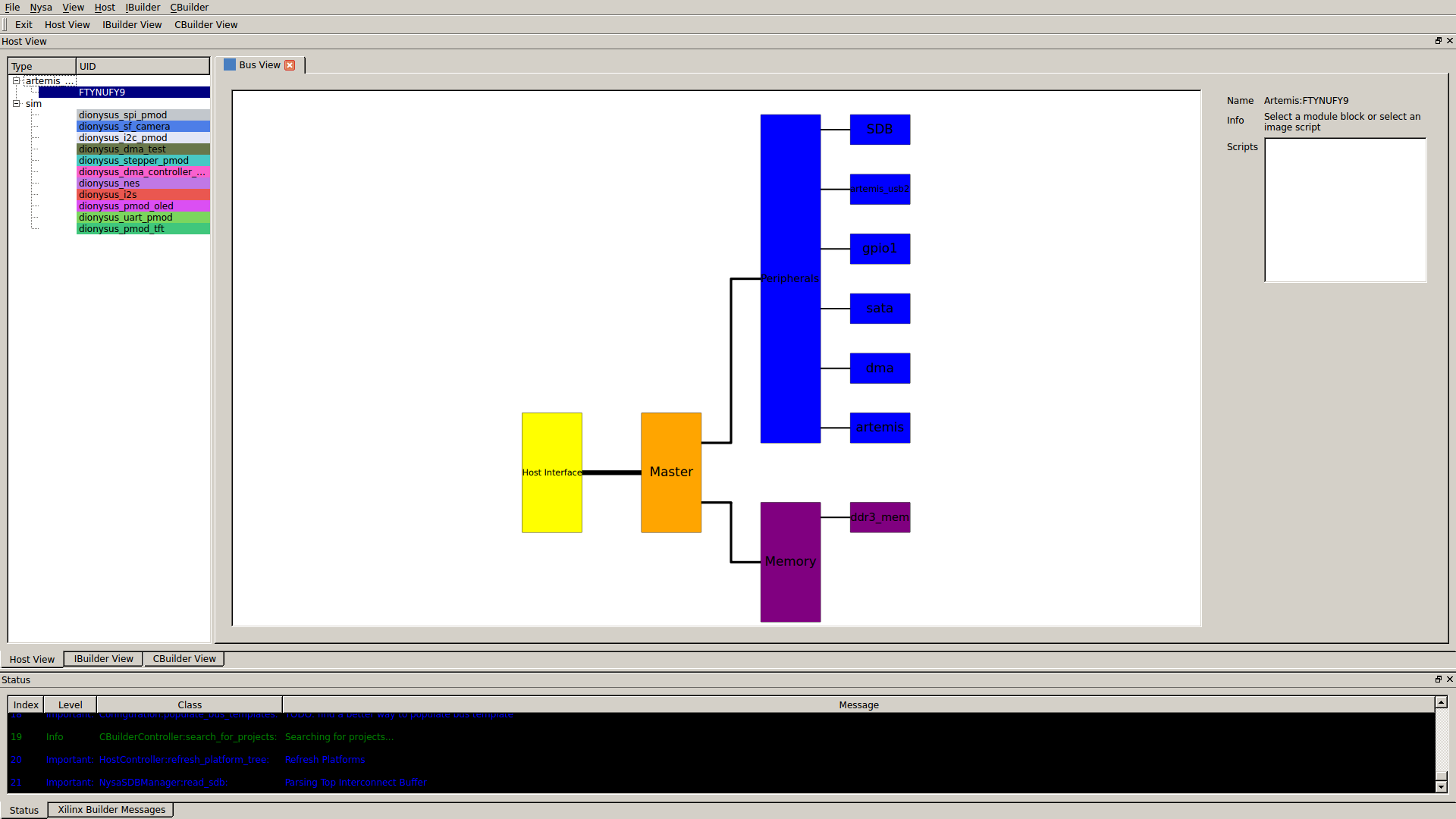

3 Years later Nysa can glue together an assortment of cores into an FPGA image graphically without writing one line of HDL.

Software:

The main repository is broken down into three parts.

- Core Builder (cbuilder): Scripts to help users generate custom cores. The tool generates verilog projects that contain not just the RTL but the build tools to verify (with iverilog) simulate and view waveforms (with gtkwave). When the user is satisfied they can use ibuilder to add their core to an FPGA image.

- Image Builder (ibuilder): Scripts to construct a custom FPGA image using the user defined core created with cbuilder and platform information to allow the host device to talk to the core. The build tool also uses the structure of the generated image to construct a ROM within the FPGA that can be used with the Host API to determine the behavior of the FPGA.

- Host: An API used to talk to the FPGA platform with an image created by ibuilder. The simple API consists of 'read' 'write' along with some helper functions.

Hardware:

There are two existing platforms I've been using Nysa with:

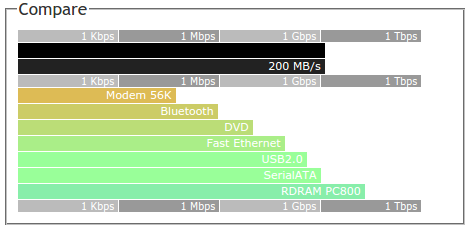

- Dionysus: a small (low cost) Spartan 6 based devboard that is in the form factor of an Arduino and can communicate with the host computer using FTDI FT2232H USB 2.0 which allows the user to both download a new FPGA image and communicate with the it at a rate of about 25MB/s. It is much faster than other UART based interfaces and streaming low resolution video to and from it is possible play video

- Prometheus: A higher end board using an Artix 7 FPGA with the intention that it will be used in high speed data acquisition, High definition video processing and SDR.

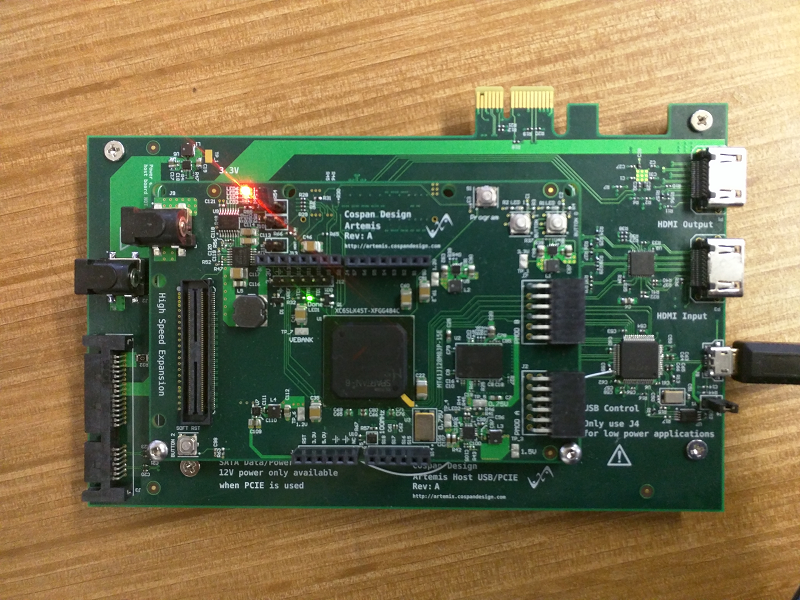

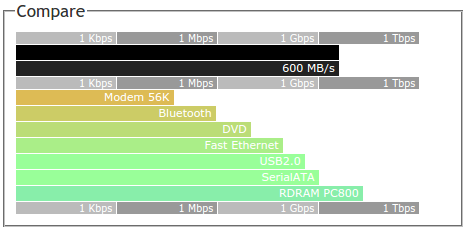

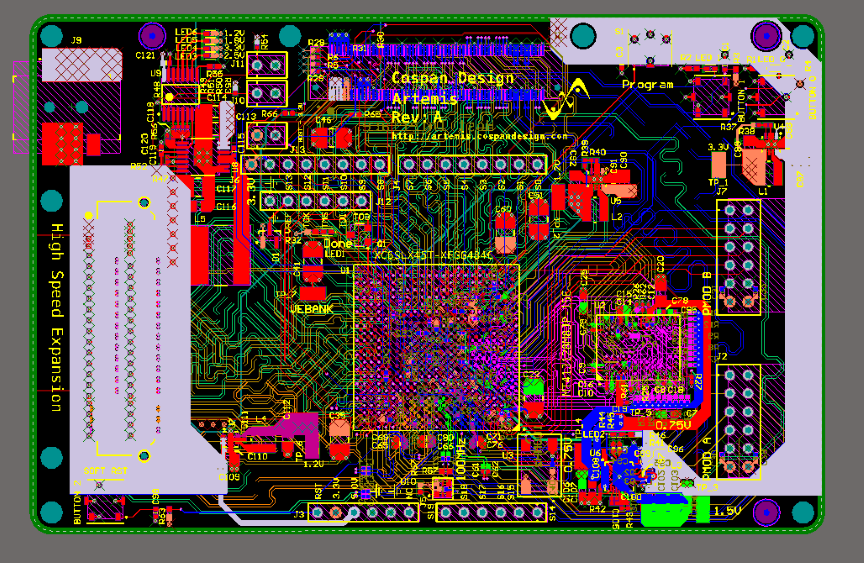

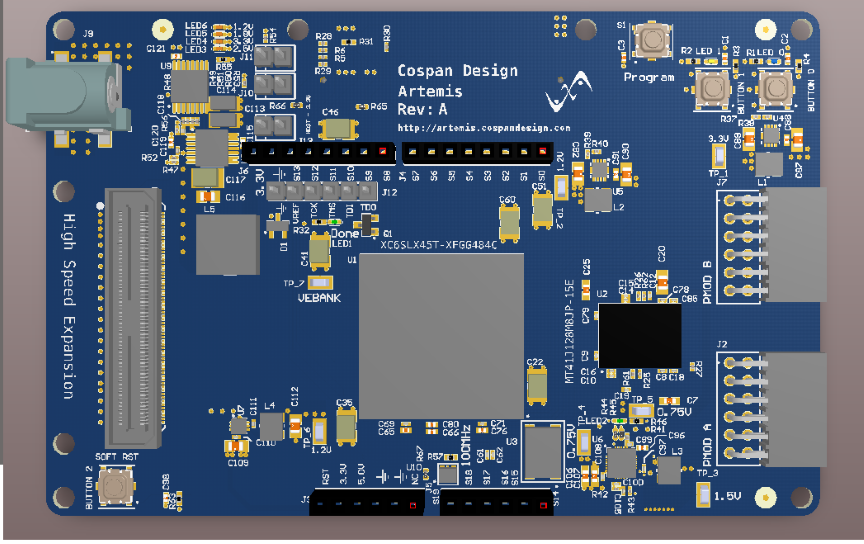

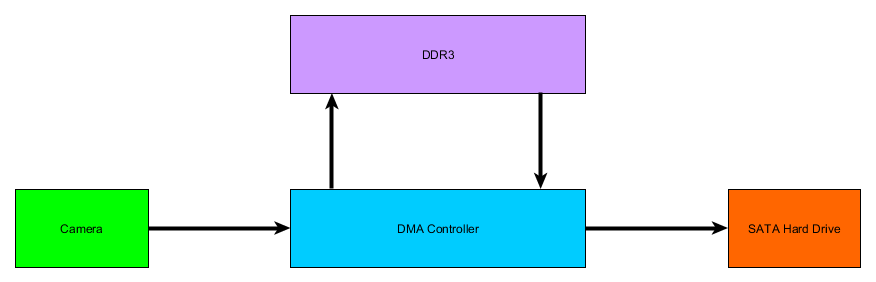

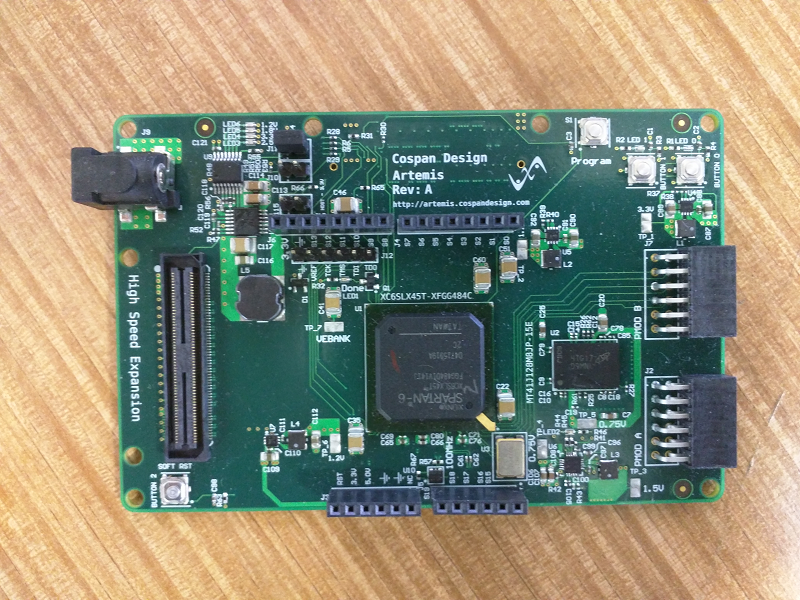

A board in the works is Artemis, first prototypes are starting fabrication in a couple of days. This is a board that has both high speed SERDES and DDR3 that will open up high video processing, SDR and, in general, more complicated projects. The board comes with two high speed connectors with the intention that the host interface can be changed from USB 2.0 to something like PCIE.

Nysa can be used with any available arbitrary FPGA devboards that supports external communication.

Dave

Dave

Artemis attached to the USB 2.0 and PCI Express Board

Artemis attached to the USB 2.0 and PCI Express Board