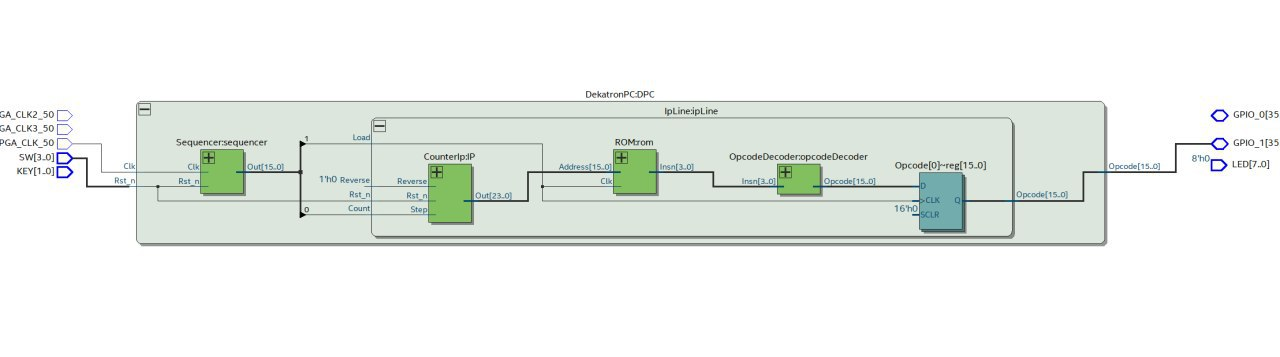

I started develop the Verilog model of DekatronPC computer in order to analyze low-level schematic of all future blocks.

This model would be very useful for:

- Understand upcoming amount of work;

- Count required number of logic elements with different types

- Implement and do debugging the circuit of logic sequencer.

- Analyze performance issues, and find ways to get maximum performance.

During the first time, while no DekatronPC blocks are exit, I will use FPGA emulator to analyze correctness.

While new computer blocks will be done, I will replace emulated parts with the physical one - So just right after the first computer block become to real life - I'll already can show how it works.

Now, I'm working on instruction fetching, and loop handling code. All the code is available on the github repository

Artem Kashkanov

Artem Kashkanov

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.