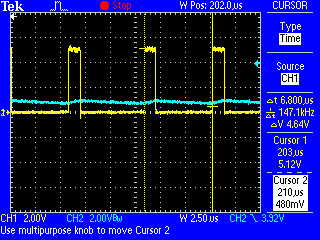

Ran some tests to determine the values of the resistor and capacitor on the temporization network that generates the P/S signal from the CLOCK signal. Also changed the delay loops in the program in order to take less time to complete all the shifting.

The resulting values are:

- Resistor: 4K7

- Capacitor: 4n7

- Delay time from CLK low to P/S low: 100us (above 50us is OK)

- Total time spent shifting the 48bits plus start and final delays: 442us. It might be necessary to synchronize the reading of the bits with the USB interrupts.

![]()

- Bit Shift timing: 6,8us (174KHz)

danjovic

danjovic

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.