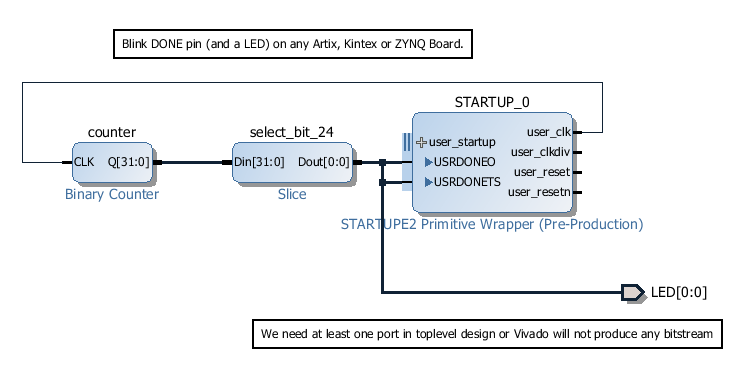

For simple LED blink, we can use internal clock and forget totally that there is a hard processor available. This design work equally well on any Artix, Kintex, Virtex or Zynq board!

If we want to write the Blinky in VHDL, then this is equally easy:

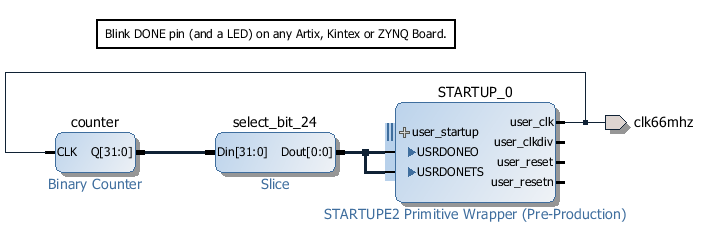

We send the clock to output port, and create wrapper that is not managed, then we can just write normal VHDL. Of course we could just instantiate the startup directly in VHDL too.

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

library UNISIM;

use UNISIM.VCOMPONENTS.ALL;

entity blink_top_wrapper is

port (

LED : out std_logic

);

end blink_top_wrapper;

architecture STRUCTURE of blink_top_wrapper is

component blink_top is

port (

clk66mhz : out STD_LOGIC

);

end component blink_top;

signal clk: std_logic;

begin

blink_top_i: component blink_top

port map (

clk66mhz => clk -- this is free running clock from BD

);

-- LED is steady on!

LED <= '1';

end STRUCTURE;This is basically the vivado generated wrapper, 3 lines changed.

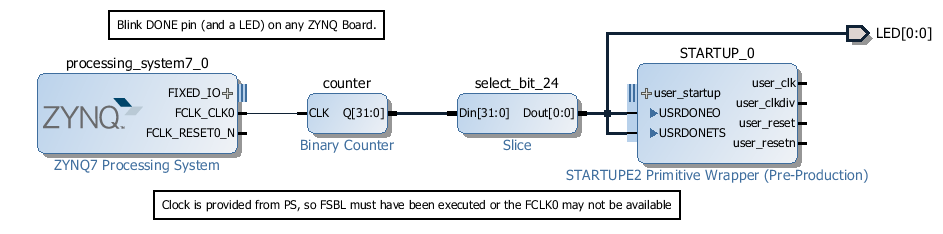

This design takes the clock from PS PLL, from FCLK0. This design only works if Zynq CPU has executed the FSBL (first stage bootloader). Again we can use this clock from the PS PLL in our plain VHDL code.

Antti Lukats

Antti Lukats

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.