There have been a few things happening since my last entry.

1. Movement of Call Return Address Register to R0.

2. An improvement of the Stack Push instruction by one clock cycle.

3. Finally hard overflowing of the area on my FPGA so that to keep two cores I had to lose the DMA block.

4. Getting 6.0 + 7.0 = 13.0 .

I've now been able to write some routines in Assembler to do Floating Point operations. Now I am sure a Professional Software Engineer might raise their eyebrows and I need to go through the routines possibly to clean up, or at least comment them, but I now have a small group of routines to do floating point support operations.

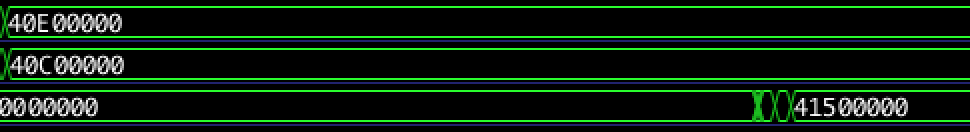

Here is a screen shot. Single Precision IEEE 754 in software adding 6.0 to 7.0 getting 13.0.

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.