Turns out that little interrupt mask was a thing...

ANDI.W #$F0FF,SR

ORI.W #$0300,SRSince I am asserting IPL2 with IPL1 and IPL0 forced to a negated state, I can only trigger interrupt level 4. By tossing those instructions into RAM, I first mask out the existing IPL bits in the status register, and then set IPL to 3 so my interrupt level 4 isn't ignored any more.

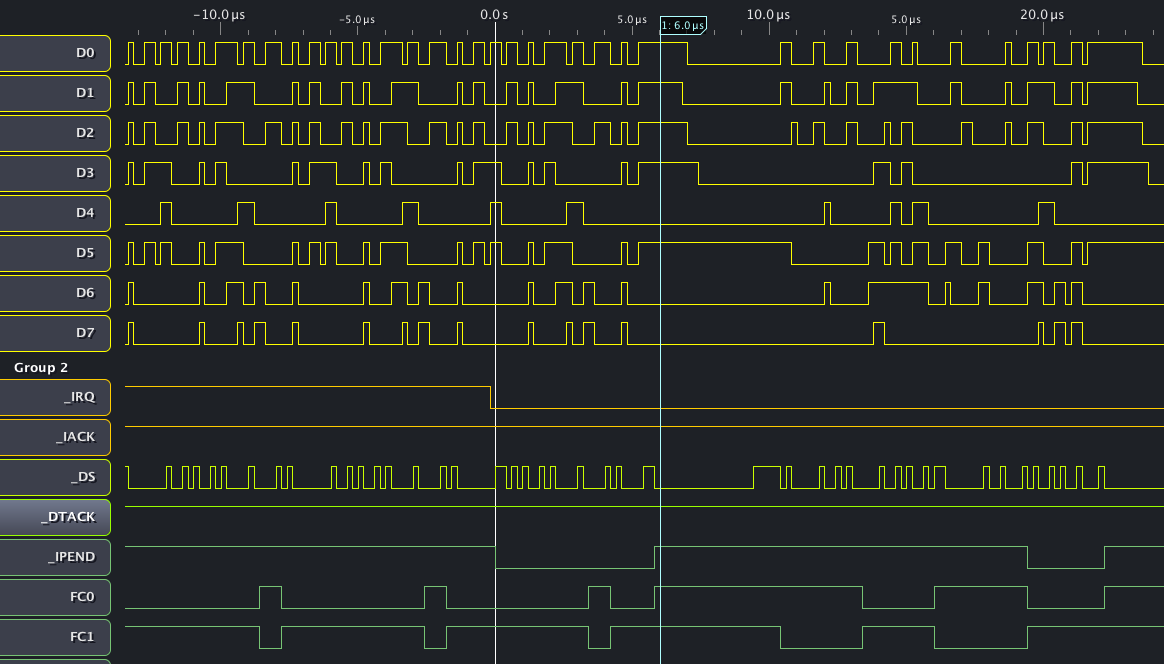

YAY... so now after _IRQ is driven low by the MC68901, the CPU responds by driving _IPEND low, and within an instruction's time, just like the document claims, the CPU sets FC0, FC1, and FC2 high to indicate CPU space (FC0 usually is the inverse of FC1).

So now what? Well, I'm not getting an _IACK on the MC68901. _DS is being asserted by the CPU, but the MC68901 won't supply the needed vector and subsequent _DTACK assertion unless _IACK and _DS are both asserted. :( Looks like a bug in my CPLD code.

Time to investigate. Bear with me folks, this stuff is all new to me. I'm one of those "learn to swim by jumping into the shark tank" types...

Jason Westervelt

Jason Westervelt

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.