-

Hack Chat Transcript, Part 3

08/28/2019 at 20:05 • 0 comments![]()

@Chip Gracey - marketing question! What's the ideal application? Do you foresee people using it as general-purpose or for a specific app? Maybe some of the forum members can share ideas.

![]() I think this interactive programming style would work best in combination with APL :-)

I think this interactive programming style would work best in combination with APL :-)Ahem... @Chip Gracey I am looking, but I don't see the P2 as a Hackaday IO project ;-)

![]() @Chip Gracey I have been following your work for perhaps 15 years - and I am so pleased that P2 is coming to fruition. I totally buy into your educational ethos, and I hope that P2 will give more power to the next generation of engineers and creatives

@Chip Gracey I have been following your work for perhaps 15 years - and I am so pleased that P2 is coming to fruition. I totally buy into your educational ethos, and I hope that P2 will give more power to the next generation of engineers and creativesMaybe you can post it and see people posting ideas about it ;-)

![]() CNC machines and 3D printers along with drone controllers

CNC machines and 3D printers along with drone controllersSocial platforms are a great way to generate product ideas IMHO ;-)

![]() Well, I just said... as a reader for our encoders which must do ATAN2. Multiple cores and A2D chanels means we could support more joints with one chip. Won't beat an FPGA, but might cost a lot less and be useful for the human input device to remote the Dexter robot arm.

Well, I just said... as a reader for our encoders which must do ATAN2. Multiple cores and A2D chanels means we could support more joints with one chip. Won't beat an FPGA, but might cost a lot less and be useful for the human input device to remote the Dexter robot arm.![]() Ideal application? Not sure. I mainly see it as an inventor's playground, and trust that it will find applications.

Ideal application? Not sure. I mainly see it as an inventor's playground, and trust that it will find applications.![]() Thanks @monsonite

Thanks @monsoniteHow it handles Multimedia ? Audio, DSP, Image Processing ?

AI is also a very good application, especially for small robots

It probably makes a very good small AI platform

![]() @james, it might not beat an FPGA in throughput potential, but it would be fast enough and code changes would take 1/500th the effort. A person might go to their grave getting Verilog code ironed out.

@james, it might not beat an FPGA in throughput potential, but it would be fast enough and code changes would take 1/500th the effort. A person might go to their grave getting Verilog code ironed out.![]() I have several Propeller projects on Hackaday.io/jac but my current project is reverse engineering a Digital Compact Cassette recorder. I think the P1 and P2 would be a good match if it would be easier to bring up the interfaces (SPI, RS-232).

I have several Propeller projects on Hackaday.io/jac but my current project is reverse engineering a Digital Compact Cassette recorder. I think the P1 and P2 would be a good match if it would be easier to bring up the interfaces (SPI, RS-232).![]() Chip : then switch to VHDL ;-)

Chip : then switch to VHDL ;-)![]() Maybe the question is better phrased as What application can the P2 excel at?

Maybe the question is better phrased as What application can the P2 excel at?![]() Yeah, robots are an ideal app.

Yeah, robots are an ideal app.![]() @Yann, yes with VHDL we could retain all the complexity, but type four times as much code.

@Yann, yes with VHDL we could retain all the complexity, but type four times as much code.![]() @Chip Gracey we don't use verilog or any text based language for our FPGA programming. totally visual language. wish I could say more, it's still fucking tied up in business shit, but will be open sourced soon.

@Chip Gracey we don't use verilog or any text based language for our FPGA programming. totally visual language. wish I could say more, it's still fucking tied up in business shit, but will be open sourced soon.![]() We're coming up on an hour, which is usually how long we go before giving the host(s) a chance to bail and get back to work. Parallax folks, you're welcome to stay on and keep fielding questions, or to bug out if you need to. Either way, I think we all want to say a huge thank you for your time today!

We're coming up on an hour, which is usually how long we go before giving the host(s) a chance to bail and get back to work. Parallax folks, you're welcome to stay on and keep fielding questions, or to bug out if you need to. Either way, I think we all want to say a huge thank you for your time today!Hack Chatters, don't forget next week's Chat is "Clean Water Technologies" with Ryan Beltran: https://hackaday.io/event/166179-clean-water-technologies-hack-chat

![]() I recently tried SpinalHDL a bit, a better alternative to Chisel, which in turn is much better than VHDL or Verilog, makes it really easy to rpogram things for FPGAs (if you know Scala)

I recently tried SpinalHDL a bit, a better alternative to Chisel, which in turn is much better than VHDL or Verilog, makes it really easy to rpogram things for FPGAs (if you know Scala)![]() Agree w/ comments re: CNC usage. Multiaxis motor control for p2, along with lots of sensor inputs, seems like a straightforward educational use. But eventually, practically speaking, you end up using a "real" motor controller in a production setting. I'd like to see how P2 compares to something like Jetson when it comes to AI / ML.

Agree w/ comments re: CNC usage. Multiaxis motor control for p2, along with lots of sensor inputs, seems like a straightforward educational use. But eventually, practically speaking, you end up using a "real" motor controller in a production setting. I'd like to see how P2 compares to something like Jetson when it comes to AI / ML.![]() I have developed the PMC-Eight system for Explore Scientific which is an astronomical robotic mount controller that excels at fine motion control for tracking the stars with the P1 chip. I am hoping to migrate to the P2 next year.

I have developed the PMC-Eight system for Explore Scientific which is an astronomical robotic mount controller that excels at fine motion control for tracking the stars with the P1 chip. I am hoping to migrate to the P2 next year.![]() The P2 will excel in places where you need to close complex feedback loops and also conduct things at a high level.

The P2 will excel in places where you need to close complex feedback loops and also conduct things at a high level.![]() We have sold over a thousand systems so far in 3 years

We have sold over a thousand systems so far in 3 years![]() As to unique applications, it seems like anything were you need to parallel process or pipeline processing. Neural Nets seems a good application.

As to unique applications, it seems like anything were you need to parallel process or pipeline processing. Neural Nets seems a good application. -

Hack Chat Transcript, Part 2

08/28/2019 at 20:04 • 0 comments![]()

![]() @IRC, no, SD boot would take longer. I'm talking about an 8-pin serial Flash.

@IRC, no, SD boot would take longer. I'm talking about an 8-pin serial Flash.![]() [Kamilion] normal old SPI NOR, winbond 4-bit style.

[Kamilion] normal old SPI NOR, winbond 4-bit style.![]() [Kamilion] Gotcha.

[Kamilion] Gotcha.![]() Hey @Joshua Donelson so good to see you here. Initial languages most likely: Spin2, MicroPython. BlocklyProp not determined. C a possibility for our development (required to get Python). This sausage is still getting made, on the Forums, within Parallax and by all of you.

Hey @Joshua Donelson so good to see you here. Initial languages most likely: Spin2, MicroPython. BlocklyProp not determined. C a possibility for our development (required to get Python). This sausage is still getting made, on the Forums, within Parallax and by all of you.![]() [Kamilion] yeah, right now micropython is running on top of a RISCV ISA simulator (and still rediculously fast)

[Kamilion] yeah, right now micropython is running on top of a RISCV ISA simulator (and still rediculously fast)![]() [Kamilion] i think someone else was working on a native port as well

[Kamilion] i think someone else was working on a native port as well![]() @Joshua - We are encouraged by all the forum interest in getting other languages implemented. MicroPython, Spin, C. We haven't decided yet when we'll implement Blockly and what language(s) it will generate.

@Joshua - We are encouraged by all the forum interest in getting other languages implemented. MicroPython, Spin, C. We haven't decided yet when we'll implement Blockly and what language(s) it will generate.![]() Yes, P1 reliably runs at -40C/-40F. I believe I had a P1 payload operating down to -50C once, but will need to check. The lipo batteries really die at these temps, so likely the P1 was not the issue when the payload stopped transmitting.

Yes, P1 reliably runs at -40C/-40F. I believe I had a P1 payload operating down to -50C once, but will need to check. The lipo batteries really die at these temps, so likely the P1 was not the issue when the payload stopped transmitting.![]() The P2 has deep debugging hooks, so I look forward to making a very fast Spin2 compiler (hit the key and your code is running 100ms later), with a really thorough and interactive debugger. The more you can quickly see and interact with your code, the better stuff you can make.

The P2 has deep debugging hooks, so I look forward to making a very fast Spin2 compiler (hit the key and your code is running 100ms later), with a really thorough and interactive debugger. The more you can quickly see and interact with your code, the better stuff you can make.![]() When start-up time is critical, it would be pretty easy to chain load from flash to an SD card, and do timing-critical initiation from flash, while the SD card code is booting in another cog.

When start-up time is critical, it would be pretty easy to chain load from flash to an SD card, and do timing-critical initiation from flash, while the SD card code is booting in another cog.![]() to solve motor driver problem while booting, use external pullup or pulldown resistors. Yes it is assitional complexy to schematics, but safety first! On any MCU. P2 can work in two stage bootloading. Boot quickly minimal code from EEPROM and set-up safety. Then boot from SD card.

to solve motor driver problem while booting, use external pullup or pulldown resistors. Yes it is assitional complexy to schematics, but safety first! On any MCU. P2 can work in two stage bootloading. Boot quickly minimal code from EEPROM and set-up safety. Then boot from SD card.![]() @Ken Gracey (Parallax) Thanks, that is a great way to do it.

@Ken Gracey (Parallax) Thanks, that is a great way to do it.![]() Like in good old P1 times.

Like in good old P1 times.![]() [Kamilion] JDat: the start up delay comment was more about FPGAs requiring time to load the bitstream before being ready to rumble; just so we're crystal

[Kamilion] JDat: the start up delay comment was more about FPGAs requiring time to load the bitstream before being ready to rumble; just so we're crystal![]() @JDat what happens is that users don't understand the need for bootup time and fail to include those pull resistors. Of course they should... but people don't always.

@JDat what happens is that users don't understand the need for bootup time and fail to include those pull resistors. Of course they should... but people don't always.![]() @Jeff Martin (Parallax) Personally I like the text programming methods over the graphics style, so Spin, C, Python are all good with me. :)

@Jeff Martin (Parallax) Personally I like the text programming methods over the graphics style, so Spin, C, Python are all good with me. :)![]() Antifuse or Flash-based FPGA (from ex-Actel) have no startup time problems :)

Antifuse or Flash-based FPGA (from ex-Actel) have no startup time problems :)![]() [Kamilion] yeah, my personal preference is using the micropython REPL to live-code

[Kamilion] yeah, my personal preference is using the micropython REPL to live-code![]() in FPGA/CPLD it can be solved with zero boot time models

in FPGA/CPLD it can be solved with zero boot time models![]() Text programming is hard to beat, once you know what you're doing. It's amazing how much can be expressed compactly with 7-bit ASCII.

Text programming is hard to beat, once you know what you're doing. It's amazing how much can be expressed compactly with 7-bit ASCII.![]() We have BLDC servo motor drive in our to-do list, so it could just be a matter of implementing our reference design and having the FET drivers connected straight to I/O pins.

We have BLDC servo motor drive in our to-do list, so it could just be a matter of implementing our reference design and having the FET drivers connected straight to I/O pins.![]() Interested to know if all of you see Python for P2 as primarily intended for an educational audience, or for commercial product development? Of course, you may ask "but what other languages could I choose from?" But I ask primarily about the role of MicroPython and P2, based on what you know, think, prefer.

Interested to know if all of you see Python for P2 as primarily intended for an educational audience, or for commercial product development? Of course, you may ask "but what other languages could I choose from?" But I ask primarily about the role of MicroPython and P2, based on what you know, think, prefer.![]()

![]()

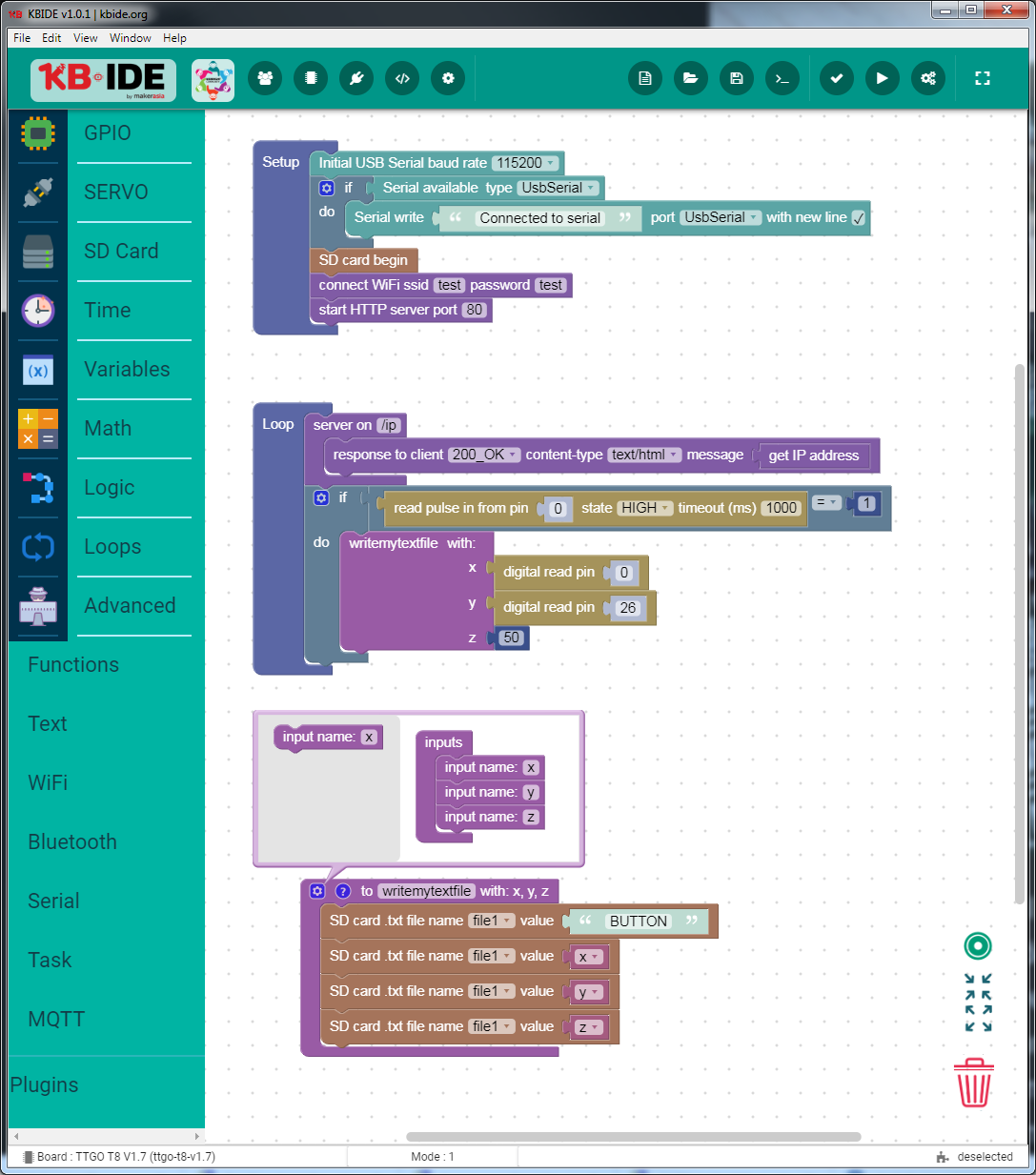

![]() [Kamilion] kbIDE's been getting a lot better recently.

[Kamilion] kbIDE's been getting a lot better recently.![]() I have lots of programs written in PropC ... will they run on P2 ?

I have lots of programs written in PropC ... will they run on P2 ?![]() [Kamilion] Generally, I'm happy with micropython as long as _thread is available. I use it heavily on the ESP32 and IMXRT1062

[Kamilion] Generally, I'm happy with micropython as long as _thread is available. I use it heavily on the ESP32 and IMXRT1062![]()

![]() [Kamilion] @hologram70: I think Catalina should be able to rebuild for P2 without much of an issue.

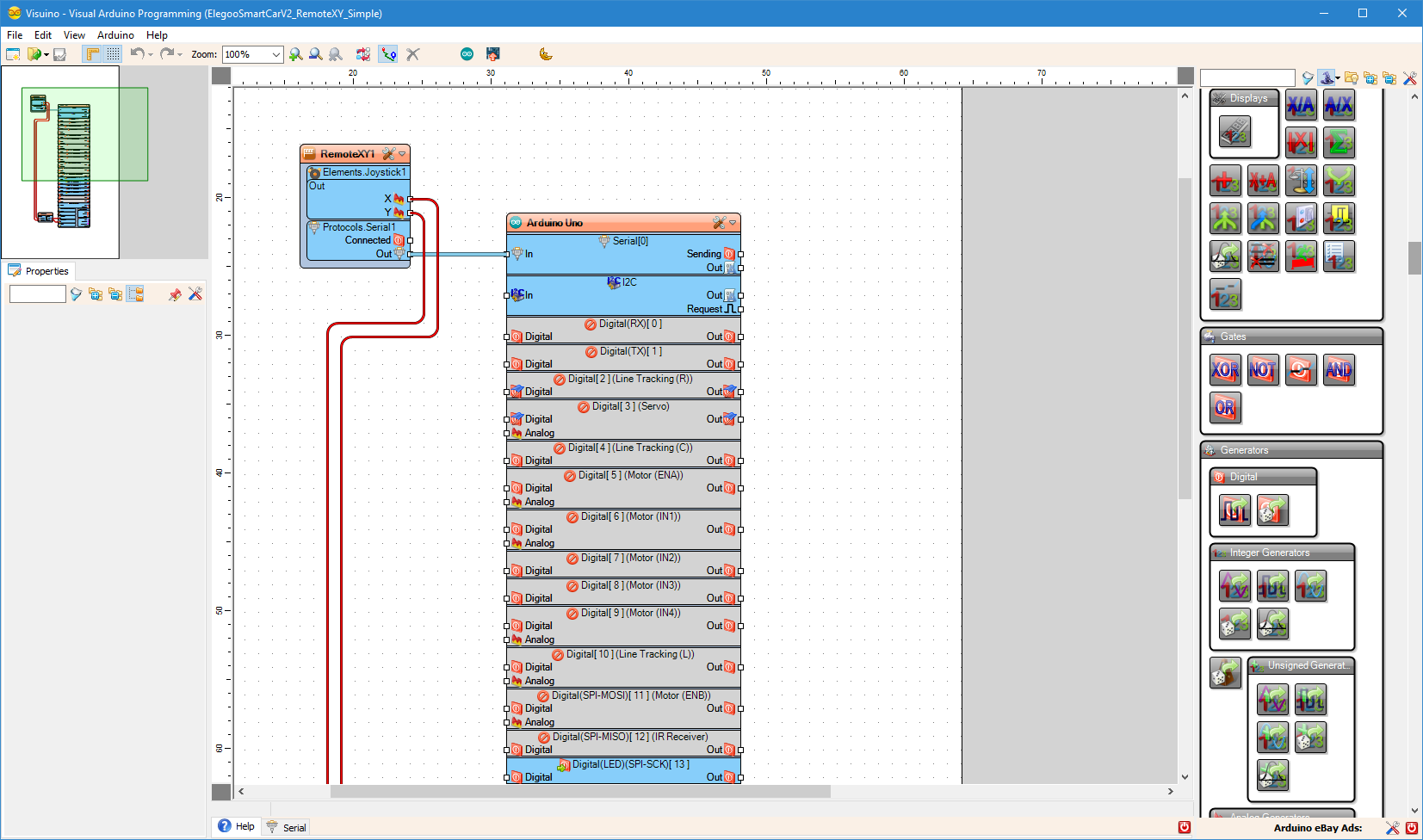

[Kamilion] @hologram70: I think Catalina should be able to rebuild for P2 without much of an issue.Would be interesting if the Propeller can be supported by Visuino ;-)

![]() [Kamilion] it *CAN* be, of course, but is anyone willing to actually go define the blocks for it?

[Kamilion] it *CAN* be, of course, but is anyone willing to actually go define the blocks for it?![]() I'm personally avoiding all thing Python. It strikes me as todays BASIC and I think it will (as BASIC did) mislead a lot of young programmers into poor practices / misunderstandings about what's actually going on inside. Y'all will laugh, but I think people who want to program for a living should learn from digital logic, to asm, to C, and then maybe JavaScript or some other commonly used language. People who will NOT be programmers and just want to dick around with code should use Python.

I'm personally avoiding all thing Python. It strikes me as todays BASIC and I think it will (as BASIC did) mislead a lot of young programmers into poor practices / misunderstandings about what's actually going on inside. Y'all will laugh, but I think people who want to program for a living should learn from digital logic, to asm, to C, and then maybe JavaScript or some other commonly used language. People who will NOT be programmers and just want to dick around with code should use Python.![]() @hologram70 - Forum user ntosme2 indicated he's working on GCC for P2.

@hologram70 - Forum user ntosme2 indicated he's working on GCC for P2.100% agree with you @James Newton

![]() I'm a fan of C programming using 7-bit ASCII. We saw a presentation from the PART team (Placer robotics) and they're doing their codng in C++. Just sayin', in case there's an argument for appealing to high school-level robotics programmer usage of P2.

I'm a fan of C programming using 7-bit ASCII. We saw a presentation from the PART team (Placer robotics) and they're doing their codng in C++. Just sayin', in case there's an argument for appealing to high school-level robotics programmer usage of P2.![]() [Kamilion] should be noted though, GCC's had huge flux since the 4.x/5.x era... It may take some time before GCC7/GCC8 patches have the bugs shaken out.

[Kamilion] should be noted though, GCC's had huge flux since the 4.x/5.x era... It may take some time before GCC7/GCC8 patches have the bugs shaken out.![]() @James Newton that's me. NOT a programmer by function, but I feel incredibly productive with blocks, Python and BASIC.

@James Newton that's me. NOT a programmer by function, but I feel incredibly productive with blocks, Python and BASIC.![]() 100 % disagree , python is useful

100 % disagree , python is useful![]() @James Newton - I think they'll always be a need for the right tool for the right job... and the right tool handler...

@James Newton - I think they'll always be a need for the right tool for the right job... and the right tool handler...@Ken Gracey (Parallax) Curious if you have tried Visuino ?

![]() Funny story with programming languages: I programmed SPIN code for barometric pressure sensor (up to 48 bit mathematic to compensate thermal error).

Funny story with programming languages: I programmed SPIN code for barometric pressure sensor (up to 48 bit mathematic to compensate thermal error).![]() Learning logic isn't as hard as it used to be, especialy with fantastic sites like:

Learning logic isn't as hard as it used to be, especialy with fantastic sites like:![]() One goy translated my spin code to python...

One goy translated my spin code to python...![]() [Kamilion] @James Newton: Only thing that's really an issue with python is that they made one mistake: Not everything is an object. Perl figured that out long ago, python3's still stuck.

[Kamilion] @James Newton: Only thing that's really an issue with python is that they made one mistake: Not everything is an object. Perl figured that out long ago, python3's still stuck.![]() next guy translated python to arduino C/C++

next guy translated python to arduino C/C++![]() As I said, if your not going to be a programmer by trade, Python is fine. Just copy paste, adjust, and you can get "somthing" working quickly.

As I said, if your not going to be a programmer by trade, Python is fine. Just copy paste, adjust, and you can get "somthing" working quickly.![]() what scripting languages do you prefer?

what scripting languages do you prefer?![]() why da hech barometer stopped to work on arduino? :D

why da hech barometer stopped to work on arduino? :D![]() @Boian Mitov no, not yet. I'm going to look at Visuino and kbIDE after reading this, though.

@Boian Mitov no, not yet. I'm going to look at Visuino and kbIDE after reading this, though.![]() Perl and javascript are excellent.

Perl and javascript are excellent.![]() why is javascript excellent

why is javascript excellentJS is probably as good as it can get for scripting

![]() "everythings an object" (or almost everything).

"everythings an object" (or almost everything).![]() Personally I really like spin but Python is a great way to go for education market. All the engineering as cs students at Smith (where I teach) are learning Python these days. I really value having access to a local (non-cloud) compiler, even if it is simplistic. Currently I use the Propeller Tool in Windows and increasingly Propeller IDE with Ubuntu..

Personally I really like spin but Python is a great way to go for education market. All the engineering as cs students at Smith (where I teach) are learning Python these days. I really value having access to a local (non-cloud) compiler, even if it is simplistic. Currently I use the Propeller Tool in Windows and increasingly Propeller IDE with Ubuntu..![]() hmm, not sure i get that, python has far more useful libraries implemented in it than JS imo

hmm, not sure i get that, python has far more useful libraries implemented in it than JS imo![]() Chip - tell us some features of the P2 you're really excited about.

Chip - tell us some features of the P2 you're really excited about.![]() Of late, I got a drum kit from a musician friend here. It's a lot of fun to play drums. It really stretches your lymbic independence and you can experience new abilities wiring up in your brain over minutes and days. This is kind of how I see programming ought to be - really allowing new things to form up. It's a lot of fun. This video (maybe watch later) demonstrates the feeling of how I want P2 programming to be:

Of late, I got a drum kit from a musician friend here. It's a lot of fun to play drums. It really stretches your lymbic independence and you can experience new abilities wiring up in your brain over minutes and days. This is kind of how I see programming ought to be - really allowing new things to form up. It's a lot of fun. This video (maybe watch later) demonstrates the feeling of how I want P2 programming to be: ![]() I'm sad people moved away from Perl. Where else can you "open file or die" or "print "hello" if ready" or embed a regexp and really confuse yourself? LOL. I wish there was a micro version of JavaScript like microPython. Then there would be "one language to rule them all". ,o)

I'm sad people moved away from Perl. Where else can you "open file or die" or "print "hello" if ready" or embed a regexp and really confuse yourself? LOL. I wish there was a micro version of JavaScript like microPython. Then there would be "one language to rule them all". ,o)![]() @jeff, new features that I'm enthused about.... All the ADC functions with SINC2 and SINC3 filtering, Goertzel input with SINC2, Scope pin modes, the CORDIC solver. All together, it's going to be a blast.

@jeff, new features that I'm enthused about.... All the ADC functions with SINC2 and SINC3 filtering, Goertzel input with SINC2, Scope pin modes, the CORDIC solver. All together, it's going to be a blast.![]() microJS ? I'd use it :-D

microJS ? I'd use it :-D![]() Agreed. I miss Perl poetry

Agreed. I miss Perl poetry![]() So @Chip Gracey do you want to comment on WHY it took so long to finish P2? Impossibly difficult? Distractions? Depressions? Abducted by Aliens?

So @Chip Gracey do you want to comment on WHY it took so long to finish P2? Impossibly difficult? Distractions? Depressions? Abducted by Aliens?![]() CORDIC ? :)

CORDIC ? :)![]() best language is APL, but only with the special APL keyboard

best language is APL, but only with the special APL keyboard![]() haha

haha![]() Has to be alien abduction, only logical option :)

Has to be alien abduction, only logical option :)![]() @james, it was a bit of everything. My dad asked me a few years ago if I'd like to just quit it. I had thought about it, but it kind of has been a force of its own. If all the work that's gone into could be made manifest in the physical, I think there'd be a spaceship.

@james, it was a bit of everything. My dad asked me a few years ago if I'd like to just quit it. I had thought about it, but it kind of has been a force of its own. If all the work that's gone into could be made manifest in the physical, I think there'd be a spaceship.![]() Sounds like the ADC stuff will allow the P2 to be a serious DSP tool?

Sounds like the ADC stuff will allow the P2 to be a serious DSP tool?![]() I think the way of the future is real-time responsive programming. I mean, the users does something and gets immediate feedback (no crazy long compilation + downloading delay). Then, you can see the results of your actions and learn from them intrinsically. REPL systems are close to this, but I mean something with more visual feedback. Many great things have been invented by accident when something unexpected was noticed... the same kind of thing can occur if users had immediate feedback, always, while programming.

I think the way of the future is real-time responsive programming. I mean, the users does something and gets immediate feedback (no crazy long compilation + downloading delay). Then, you can see the results of your actions and learn from them intrinsically. REPL systems are close to this, but I mean something with more visual feedback. Many great things have been invented by accident when something unexpected was noticed... the same kind of thing can occur if users had immediate feedback, always, while programming.![]() @Chip Gracey I understand exactly how certain ideas / projects can become their own entities. Almost freestanding from the developer. Sometimes they become the villain of the story. I've been tortured by a few and had to escape. But I'm always drawn back eventually.

@Chip Gracey I understand exactly how certain ideas / projects can become their own entities. Almost freestanding from the developer. Sometimes they become the villain of the story. I've been tortured by a few and had to escape. But I'm always drawn back eventually.![]() @Yann Guidon / YGDES - https://en.wikipedia.org/wiki/CORDIC

@Yann Guidon / YGDES - https://en.wikipedia.org/wiki/CORDICI personally believe that traditional coding will become obsolete, and replaced by dataflow based programming languages, but that's me... ;-)

![]() @james, a lot of what's in the P2 is way beyond what I could ever come up with. People on the forum have had huge effects on the direction of the project.

@james, a lot of what's in the P2 is way beyond what I could ever come up with. People on the forum have had huge effects on the direction of the project.![]() @Jeff Martin (Parallax) That's one of the things I love about digital logic: Poking it and seeing what happens instantly.

@Jeff Martin (Parallax) That's one of the things I love about digital logic: Poking it and seeing what happens instantly.![]() Jeff : yes I know, it's awesome to have it :-) I try to understand https://en.wikipedia.org/wiki/BKM_algorithm

Jeff : yes I know, it's awesome to have it :-) I try to understand https://en.wikipedia.org/wiki/BKM_algorithm![]() One of my favorite programming interfaces that I learned on was the HP graphing calculator, because each program was a file that could be opened and edited right there on the device, despite only having 32 KB of RAM.

One of my favorite programming interfaces that I learned on was the HP graphing calculator, because each program was a file that could be opened and edited right there on the device, despite only having 32 KB of RAM.Traditional programming languages are by definition not well suited for multicore, parallel processing of FPGA programming, since they tend to be sequential by nature

![]() @James Newton - Yes! We need to make programming like that; like toys are to kids, where you can see all the parts and learn how it works by touching it, manipulating it, and it some cases, pulling it apart and reconfiguring it.

@James Newton - Yes! We need to make programming like that; like toys are to kids, where you can see all the parts and learn how it works by touching it, manipulating it, and it some cases, pulling it apart and reconfiguring it.![]() Yeah, there needs to be some new way of doing things. Jeff and I have been thinking about the matter for years. It's like we would recognize it if we saw it, but we can't invent it.

Yeah, there needs to be some new way of doing things. Jeff and I have been thinking about the matter for years. It's like we would recognize it if we saw it, but we can't invent it.I mean... come on people... we still program the same way we did 200 years ago, when Ada Lovelace was coding for mechanical beats...

![]() @Chip Gracey Hey... can you do a quick ATAN2 on the P2? Might be good for reading the weird encoders on the Dexter robot.

@Chip Gracey Hey... can you do a quick ATAN2 on the P2? Might be good for reading the weird encoders on the Dexter robot.Well.. take a look at Visuino ;-)

![]() interactive graphical programming : i've been dreaming about it for more than 20 years :-D

interactive graphical programming : i've been dreaming about it for more than 20 years :-DIt is a new way of programming

@Yann Guidon / YGDES Visuino does it :-)

![]() @Boian Mitov I don't know what a dataflow language is but will research. I like visual programming languages. The use of BlocklyProp for P1 has really helped many visualize the use of multiple cores graphically, letting them do impressive stuff. I've seen how much teachers (and we've taught 10K of them) achieve results quickly. Maybe we're not close to the hardware, but we're also not making products - more like learning to think programmatically. So, I'm a blockhead.

@Boian Mitov I don't know what a dataflow language is but will research. I like visual programming languages. The use of BlocklyProp for P1 has really helped many visualize the use of multiple cores graphically, letting them do impressive stuff. I've seen how much teachers (and we've taught 10K of them) achieve results quickly. Maybe we're not close to the hardware, but we're also not making products - more like learning to think programmatically. So, I'm a blockhead.And OpenWire Studio if you are really into interactive :-)

![]() @james, yes the CORDIC can do a 32-bit quality ATAN2, converting (X,Y) into (rho,theta).

@james, yes the CORDIC can do a 32-bit quality ATAN2, converting (X,Y) into (rho,theta).Blocky is not dataflow

![]() @Jeff Martin (Parallax) I also have come to respect scratch (cough) I mean blockly, for it's ability to trigger a single block or a group and see what happens.

@Jeff Martin (Parallax) I also have come to respect scratch (cough) I mean blockly, for it's ability to trigger a single block or a group and see what happens.Blocky is traditional old school sequencial language

![]() I program digital logic visually, every time I draw up a schematic, but the overhead seems to increase geometrically, as the design complexity increases linearly. Even still, I think schematic software is the best visual programming interface available.

I program digital logic visually, every time I draw up a schematic, but the overhead seems to increase geometrically, as the design complexity increases linearly. Even still, I think schematic software is the best visual programming interface available.![]() this is better than REPL, realtime interactive programming and evaluation:

this is better than REPL, realtime interactive programming and evaluation:![]() dataflow graph programming... i'd love to have a graphical interface to the compiler's Internal Representation, without all the language specific fluff

dataflow graph programming... i'd love to have a graphical interface to the compiler's Internal Representation, without all the language specific fluff![]() @Chip Gracey We need a low(er) cost solution for a human interface device that isn't as fast as the FPGA but can still return the more than a million points per revolution on our encoders. To be used for a human input device for remote control.

@Chip Gracey We need a low(er) cost solution for a human interface device that isn't as fast as the FPGA but can still return the more than a million points per revolution on our encoders. To be used for a human input device for remote control.Visuino does exactly this

You have it @Chip Gracey :-) Already done :-)

You design the data flow... and it knows how to program it for you, and how to optimize the code to the extreme :-)

![]() @Frank Buss - Yes, Bret Victor is a great inspireror. I want to make some of his ideas a reality on the P2.

@Frank Buss - Yes, Bret Victor is a great inspireror. I want to make some of his ideas a reality on the P2.![]() I like how Atmel Start works: you select which

I like how Atmel Start works: you select which -

Hack Chat Transcript, Part 1

08/28/2019 at 20:03 • 0 comments![]() The Chip-beacon has sounded; he is on his way. . .somewhere.

The Chip-beacon has sounded; he is on his way. . .somewhere.![]() Welcome everyone, thanks for joining the Hack Chat today. We've got Ken and Chip Gracey from Parallax here today, ready to answer all your questions.

Welcome everyone, thanks for joining the Hack Chat today. We've got Ken and Chip Gracey from Parallax here today, ready to answer all your questions.Ken, Chip - welcome aboard and thanks for taking time out of your day for us. Looks like we have Jeff Martin too?

![]() Jeff Martin and I are both here, from Parallax.

Jeff Martin and I are both here, from Parallax.![]() Chip is still logging in; password update and here he comes. Yep, you have Jeff Martin and David Carrier here as well.

Chip is still logging in; password update and here he comes. Yep, you have Jeff Martin and David Carrier here as well.![]() Okay, I think I'm in.

Okay, I think I'm in.![]() Welcome to all the Parallax team then! Thanks for joining us today.

Welcome to all the Parallax team then! Thanks for joining us today.![]() Jeff has developed our software tools for 20+ yrs and participated in P1 design; David does firmware, PCB design, manufacturing support and anything else. Fozzie is here.

Jeff has developed our software tools for 20+ yrs and participated in P1 design; David does firmware, PCB design, manufacturing support and anything else. Fozzie is here.![]() Hi everyone!

Hi everyone!Hello @Chip Gracey

![]() [Kamilion] Hi guys! Guess the first question is, how are things looking with the die test at onsemi? We're all awaiting the P2 for xmas with baited breath.

[Kamilion] Hi guys! Guess the first question is, how are things looking with the die test at onsemi? We're all awaiting the P2 for xmas with baited breath.![]() Hello, Boian.

Hello, Boian.![]() Jim (Publison) here to provide bodygaurd provisions for Ken ana Chip

Jim (Publison) here to provide bodygaurd provisions for Ken ana Chip![]() [de∫hipu] bated breath

[de∫hipu] bated breath![]() Hi Ken, Chip. Wanted to say I'm a huge fan of Chips work. I ran sxlist.com back in the day and appreciated being able to translate PIC code to SX and run it 4x faster. (or nearly 4X, jumps killed the que of course)

Hi Ken, Chip. Wanted to say I'm a huge fan of Chips work. I ran sxlist.com back in the day and appreciated being able to translate PIC code to SX and run it 4x faster. (or nearly 4X, jumps killed the que of course)![]() hmmmm it smells like ASIC here :-)

hmmmm it smells like ASIC here :-)![]() Chip will answer the die-testing question; I'll address the availability of chips by ChipMas.

Chip will answer the die-testing question; I'll address the availability of chips by ChipMas.![]() Well, the chips we got back, initially, work great. However, ON Semi started running into lots of trouble testing the remaining wafers. It turns out that we have a latch-up problem in the I/O circuit that will require a slight redesign.

Well, the chips we got back, initially, work great. However, ON Semi started running into lots of trouble testing the remaining wafers. It turns out that we have a latch-up problem in the I/O circuit that will require a slight redesign.![]() James, I am glad sxlist is still running, I used it to find something last year, when working on an SX project!

James, I am glad sxlist is still running, I used it to find something last year, when working on an SX project!![]() ON Semi has about 1K die (possibly more) which are engineering samples we will soon have packaged. They plan on getting the packaging done after they unravel the current testing issues with Chip. At that time, we're looking at about 7 weeks from release to packaging.

ON Semi has about 1K die (possibly more) which are engineering samples we will soon have packaged. They plan on getting the packaging done after they unravel the current testing issues with Chip. At that time, we're looking at about 7 weeks from release to packaging.![]() chip testing can look dull but it's actually something I focus on in some of my Hackaday projects, so please elaborate and explain you workflow :-)

chip testing can look dull but it's actually something I focus on in some of my Hackaday projects, so please elaborate and explain you workflow :-)![]() Huge fan of Kens work as well, but the chip work (see what I did there?) was amazing.

Huge fan of Kens work as well, but the chip work (see what I did there?) was amazing.![]() The chips that we have here work better than anticipated, since the PLL got cleaned up and the new clock-gating cut the power consumption in half.

The chips that we have here work better than anticipated, since the PLL got cleaned up and the new clock-gating cut the power consumption in half.![]() [Kamilion] aye, I've been following along on the forum with the die tests; and watched the call go out to P2-ES gloptop owners to check the IO resistances

[Kamilion] aye, I've been following along on the forum with the die tests; and watched the call go out to P2-ES gloptop owners to check the IO resistances![]() clock gating ? swwweeeeeet :-)

clock gating ? swwweeeeeet :-)![]() [Kamilion] I'm still in awe y'all managed to blow past 300Mhz for a fMAX of 185Mhz/85C

[Kamilion] I'm still in awe y'all managed to blow past 300Mhz for a fMAX of 185Mhz/85C![]() These 1K chips could easily help us build another 250 Propeller 2 Evaluation Boards and accessories. I think it's realistic to say we'll have these boards available ChipMas (if I have to guess) so we all have something productive to do when relatives come over.

These 1K chips could easily help us build another 250 Propeller 2 Evaluation Boards and accessories. I think it's realistic to say we'll have these boards available ChipMas (if I have to guess) so we all have something productive to do when relatives come over.![]() [Kamilion] reminds me of the old Celeron 300A -> 450Mhz

[Kamilion] reminds me of the old Celeron 300A -> 450Mhz![]() Chip, were the Rev1 chips put through the same testing as rev 2?

Chip, were the Rev1 chips put through the same testing as rev 2?![]() I'm hoping we can get a few hundred chips out of the current lot, before the next fab turn. We are ready to build lots of new P2 Eval boards.

I'm hoping we can get a few hundred chips out of the current lot, before the next fab turn. We are ready to build lots of new P2 Eval boards.![]() [Kamilion] I just wanna say, I am TOTALLY fine with a "preproduction" with a disabled bank of smartpins for chipmas.

[Kamilion] I just wanna say, I am TOTALLY fine with a "preproduction" with a disabled bank of smartpins for chipmas.![]() @engineering, yes. Due to some lower substrate resistance, though, the latch-up problem reared its head.

@engineering, yes. Due to some lower substrate resistance, though, the latch-up problem reared its head.![]() @IRC, these chips will have no disabilities.

@IRC, these chips will have no disabilities.![]() @Kamilion good to know. This kind of flexibility has been appreciated. It seems that your chips would be fully functional.

@Kamilion good to know. This kind of flexibility has been appreciated. It seems that your chips would be fully functional.![]() Anyway, it feels like we got to the finish line, but tripped over it.

Anyway, it feels like we got to the finish line, but tripped over it.![]() @Chip Gracey - How will engineering sample users prevent the latch up problem?

@Chip Gracey - How will engineering sample users prevent the latch up problem?![]() Chip design is an art ;-)

Chip design is an art ;-)![]() For those looking for more detail than a chat can provide, this is a good start https://propeller.parallax.com/

For those looking for more detail than a chat can provide, this is a good start https://propeller.parallax.com/![]() In the next few days, we should have these silicon problems remedied, but then we need to wait for another fab run to get final production parts.

In the next few days, we should have these silicon problems remedied, but then we need to wait for another fab run to get final production parts.![]() Since I haven't really been following the propeller closely, can someone set the stage for this with the back story? What's been the issue?

Since I haven't really been following the propeller closely, can someone set the stage for this with the back story? What's been the issue?![]() Kamilion, none of them will be wasted; we'll use the ones with bad pins for internal development.

Kamilion, none of them will be wasted; we'll use the ones with bad pins for internal development.![]() Ah, nevermind, just saw the line.

Ah, nevermind, just saw the line.![]() link

link![]() @jeff, there is nothing to do on the user's end. Some chips just won't latch up. Others will.

@jeff, there is nothing to do on the user's end. Some chips just won't latch up. Others will.![]() [Kamilion] backstory here, James: http://forums.parallax.com/discussion/170380/new-p2-silicon/

[Kamilion] backstory here, James: http://forums.parallax.com/discussion/170380/new-p2-silicon/![]() thanks

thanks![]() [Kamilion] V2431 is the one that is most concerning to me

[Kamilion] V2431 is the one that is most concerning to me![]() In general, don't send signals to I/O pins, before powering on a semiconductor.

In general, don't send signals to I/O pins, before powering on a semiconductor.![]() Everything checks out okay on the new silicon. The HDMI works, the scope pins work, etc.

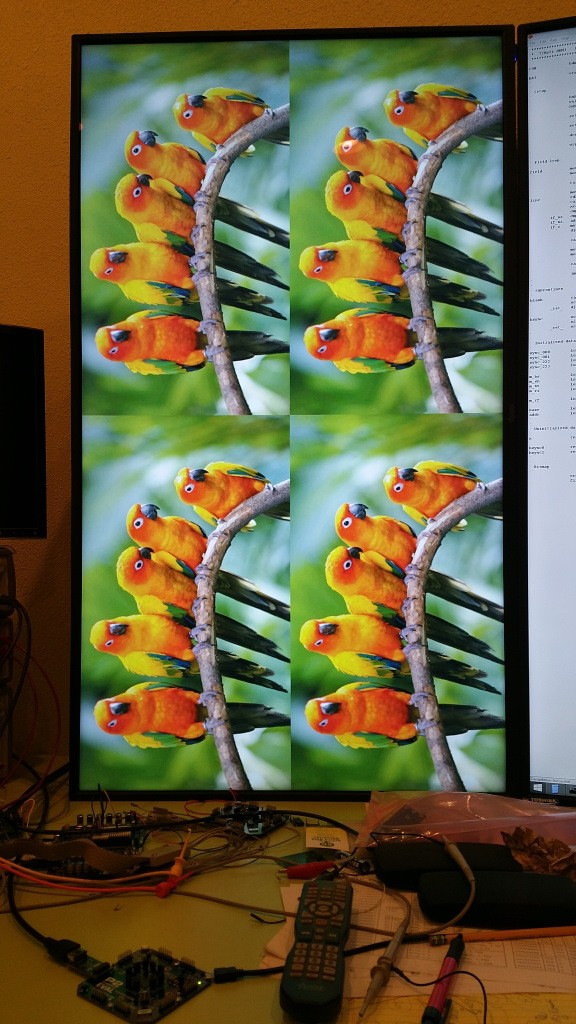

Everything checks out okay on the new silicon. The HDMI works, the scope pins work, etc.![]() [Arsenijs] HDMI? that's cool!

[Arsenijs] HDMI? that's cool!![]() So it sounds like P2 will be production ready around Christmas / Chipmas? Any chance of a P2 Expo before that?

So it sounds like P2 will be production ready around Christmas / Chipmas? Any chance of a P2 Expo before that?![]() Can HDMI out be repurposed ? :-D

Can HDMI out be repurposed ? :-D![]() @IRC, the latch-up can occur on any VIO pin. We've seen it all over on some dies at ON Semi.

@IRC, the latch-up can occur on any VIO pin. We've seen it all over on some dies at ON Semi.![]()

![]()

![]() We can't have a P2 expo without P2s, so an Expo will have to be after.

We can't have a P2 expo without P2s, so an Expo will have to be after.![]() @yann, HDMI can be repurposed if you can use the TMDS encoding in another type of application.

@yann, HDMI can be repurposed if you can use the TMDS encoding in another type of application.![]() @David Carrier - Yeah, we "tried" that once before. ;-P

@David Carrier - Yeah, we "tried" that once before. ;-P![]() @Jac Goudsmit a P2 Expo has definitely been on our minds and will be planned. When (a) we have enough chips on hand for people to build their own boards (maybe before December, if we allocate some of the 1K units for individual sale) and (b) we have six months to plan it we can schedule. I'm really hoping we can have an Expo by May.

@Jac Goudsmit a P2 Expo has definitely been on our minds and will be planned. When (a) we have enough chips on hand for people to build their own boards (maybe before December, if we allocate some of the 1K units for individual sale) and (b) we have six months to plan it we can schedule. I'm really hoping we can have an Expo by May.![]() @Chip some high-bandwidth interco maybe ? :-D

@Chip some high-bandwidth interco maybe ? :-D![]() With the new streamer and scope pins, you can capture two analog channels and 16 I/O pins in every clock. That replicates my desk scope function, but the analog bandwith is only a few MHz.

With the new streamer and scope pins, you can capture two analog channels and 16 I/O pins in every clock. That replicates my desk scope function, but the analog bandwith is only a few MHz.![]()

![]()

![]() [Kamilion] the i/q stuff works in the respin too :D

[Kamilion] the i/q stuff works in the respin too :D![]() Yes, the IQ modulators work on the new silicon. So do the rotary encoder inputs.

Yes, the IQ modulators work on the new silicon. So do the rotary encoder inputs.![]() Someone really needs to pickup and run with the SDRAM Thing idea for a low cost scope. The P2 could provide logic and IO for that pretty easily.

Someone really needs to pickup and run with the SDRAM Thing idea for a low cost scope. The P2 could provide logic and IO for that pretty easily.![]() It's frustrating - everything works, but we don't have production chips, yet.

It's frustrating - everything works, but we don't have production chips, yet.![]() Hello Chip!

Hello Chip!![]() Hi, JDat.

Hi, JDat.![]() Sorry for repetitive question: what about code protection on chip?

Sorry for repetitive question: what about code protection on chip?![]() Chip, what does it feel like to work on the same project for so many years?

Chip, what does it feel like to work on the same project for so many years?![]() [Kamilion] James, there's already a HyperRAM board rolled up using http://www.issi.com/US/product-cellular-ram.shtml (similar ISSI PSRAM chip to what's found on the ESP32-WROVER-B )

[Kamilion] James, there's already a HyperRAM board rolled up using http://www.issi.com/US/product-cellular-ram.shtml (similar ISSI PSRAM chip to what's found on the ESP32-WROVER-B )![]() Besides taco machines? :)

Besides taco machines? :)![]() Hello Ken and Chip! Glad to hear the ON believes they found the cause of the latchup problem. Can't wait to get a P2ES Rev.B :)

Hello Ken and Chip! Glad to hear the ON believes they found the cause of the latchup problem. Can't wait to get a P2ES Rev.B :)![]() @ken, it's like wandering in the desert for 40 years. It's great when it finally comes together, though, and everything is working better than hoped.

@ken, it's like wandering in the desert for 40 years. It's great when it finally comes together, though, and everything is working better than hoped.![]() [Arsenijs] me away for 3 minutes

[Arsenijs] me away for 3 minutes![]() [Arsenijs] *30

[Arsenijs] *30![]() The world changes a lot in 13 years. I hope there are still lots of inventors out there who want to build from a first-principles basis, and make things they have absolute control over.

The world changes a lot in 13 years. I hope there are still lots of inventors out there who want to build from a first-principles basis, and make things they have absolute control over.![]() Kamilion, I don't want to derail chat, but I don't see the point of those HyperRAM boards just based on the cost vs standard SDRAM. Can we chat about that separately?

Kamilion, I don't want to derail chat, but I don't see the point of those HyperRAM boards just based on the cost vs standard SDRAM. Can we chat about that separately?![]() Chip, not sure it has been asked on the fourm; wile the rev2 work on a rev1ES board?

Chip, not sure it has been asked on the fourm; wile the rev2 work on a rev1ES board?![]() I thing that P2 is coming on right time. Mainstream marked for DIYers is stabilised and you know what onchip peripherals are necessary for DIYers and can offer exactly what people need.

I thing that P2 is coming on right time. Mainstream marked for DIYers is stabilised and you know what onchip peripherals are necessary for DIYers and can offer exactly what people need.![]() @james, HyperRAM takes only 11 pins. SDRAM takes at least double, if I recall.

@james, HyperRAM takes only 11 pins. SDRAM takes at least double, if I recall.![]() C64 ISEPIC 1986

C64 ISEPIC 1986Apple 2 SoundAce 1987 (?)

PIC Programmer 1990

BASIC Stamp 1 1992

BASIC Stamp II 1995

SX Key/Chips 1997

Propeller 1 2006

A bit of Chip's development history.

![]() Chip, can you explain why you feel the P2 is still relevant in this day and age of lower cost FPGAs and other silicon?

Chip, can you explain why you feel the P2 is still relevant in this day and age of lower cost FPGAs and other silicon?![]() For those interested, we plan on making the P2 compatible with all xSPI devices, including HyperRAM. It is a new protocol, but as more companies implement it, the price is dropping quickly.

For those interested, we plan on making the P2 compatible with all xSPI devices, including HyperRAM. It is a new protocol, but as more companies implement it, the price is dropping quickly.![]() @james, I think the P2 will be relevant because it lets you control signal timing easily. FPGAs can do that, but with much complexity along the way. Microcontrollers can't do that, unless they have dedicated silicon peripherals. With the P2, you can cook up your own.

@james, I think the P2 will be relevant because it lets you control signal timing easily. FPGAs can do that, but with much complexity along the way. Microcontrollers can't do that, unless they have dedicated silicon peripherals. With the P2, you can cook up your own.![]() Chip, the SDRAM thing idea uses most of those pins to make the RAM drive itself. You don't need all of them... but yes, more than 11... If hyperram prices drop, it's worth doing.

Chip, the SDRAM thing idea uses most of those pins to make the RAM drive itself. You don't need all of them... but yes, more than 11... If hyperram prices drop, it's worth doing.![]() So, like the SX, it makes bit banging "virtual peripherals" easy?

So, like the SX, it makes bit banging "virtual peripherals" easy?![]() Chip did you count how many times Ken told you: "We need to finish P2" ?

Chip did you count how many times Ken told you: "We need to finish P2" ?![]() [Kamilion] personally, it's relevant as "another fast MCU that isn't leveraging linux", and thus inheriting all the realtime quirks of linux. I am really interested in using it for physical interfacing, and as an inexpensive alternative to stupid-expensive asics like RA8876L

[Kamilion] personally, it's relevant as "another fast MCU that isn't leveraging linux", and thus inheriting all the realtime quirks of linux. I am really interested in using it for physical interfacing, and as an inexpensive alternative to stupid-expensive asics like RA8876L![]() My push now is to get Spin2 working, which will make a very easy and fast test bed for demonstrating P2 capabilities.

My push now is to get Spin2 working, which will make a very easy and fast test bed for demonstrating P2 capabilities.![]() The P1 is excellent at implementing designs that would otherwise require an FPGA, but allowing easier sequential programming. The P2 ups those capabilities, meaning that more designs that would have required the longer design time of an FPGA are possible with easier sequential programming.

The P1 is excellent at implementing designs that would otherwise require an FPGA, but allowing easier sequential programming. The P2 ups those capabilities, meaning that more designs that would have required the longer design time of an FPGA are possible with easier sequential programming.Just because the unit price of an FPGA is dropping doesn't mean that the extra development time is worth it.

![]() @IRC - or some other RTOS. Agreed.

@IRC - or some other RTOS. Agreed.![]() Hi Chip - I have been using the P1 since 2006 on altitude-controlled balloons - flown at both poles and many places between up to 18kft. Have also been developing a 4-axis stepper driver / gcode interpreter using the P1. I am very excited about the P2 and look forward to working with it soon! I am in awe of your work.

Hi Chip - I have been using the P1 since 2006 on altitude-controlled balloons - flown at both poles and many places between up to 18kft. Have also been developing a 4-axis stepper driver / gcode interpreter using the P1. I am very excited about the P2 and look forward to working with it soon! I am in awe of your work.![]() Yes, Ken has said many times that P2 must be done. My dad was saying that everyday for years. Before the P1 was done, Ken was getting really upset with me that it was taking so long. My dad was a calming factor.

Yes, Ken has said many times that P2 must be done. My dad was saying that everyday for years. Before the P1 was done, Ken was getting really upset with me that it was taking so long. My dad was a calming factor.![]() [Kamilion] yeah, FOMU demonstrates that a cheap FPGA is nice, but having to wait for the logic to settle on powerup can be an issue for many designs.

[Kamilion] yeah, FOMU demonstrates that a cheap FPGA is nice, but having to wait for the logic to settle on powerup can be an issue for many designs.![]() @Pvoss, I think you will like it.

@Pvoss, I think you will like it.![]() David Carrier, glad to see you here.

David Carrier, glad to see you here.![]() @pvoss - do you have any temperature data to share? Extremes?

@pvoss - do you have any temperature data to share? Extremes?![]() The powerup delay can be a serious issue... especially motor drivers and servo controllers and the like. A lot of bad things can happen in uS and they don't always bias things correctly for no action until ready.

The powerup delay can be a serious issue... especially motor drivers and servo controllers and the like. A lot of bad things can happen in uS and they don't always bias things correctly for no action until ready.![]() [Kamilion] the kendryte K210's FpIO is also very nice, but it's more of a pin matrix mux, versus the p2's eggbeater. ESP32's also got internal peripheral to pin mux, but it's not very flexible.

[Kamilion] the kendryte K210's FpIO is also very nice, but it's more of a pin matrix mux, versus the p2's eggbeater. ESP32's also got internal peripheral to pin mux, but it's not very flexible.![]() Is there going to be a focus on being able to use Blocky with the P2 or is Spin2 going to be the main programming method?

Is there going to be a focus on being able to use Blocky with the P2 or is Spin2 going to be the main programming method?![]() [Kamilion] And then there's cypress. Nice hardware, but way too expensive to license IP if you ever want to go into production. ( like $11k/yr for just the USB core, ugh )

[Kamilion] And then there's cypress. Nice hardware, but way too expensive to license IP if you ever want to go into production. ( like $11k/yr for just the USB core, ugh )![]() [Kamilion] Joshua, Blockly and stuff will probably be driven by the community

[Kamilion] Joshua, Blockly and stuff will probably be driven by the community![]() Jmg, a guy on the forum, really pushed for fast boot-up on the P2. I believe the P2 can power-up and start running user code in about 30ms.

Jmg, a guy on the forum, really pushed for fast boot-up on the P2. I believe the P2 can power-up and start running user code in about 30ms.![]() [Kamilion] IIRC, that 30ms does not include SD init, does it?

[Kamilion] IIRC, that 30ms does not include SD init, does it?![]()

Lutetium

Lutetium

We're coming up on an hour, which is usually how long we go before giving the host(s) a chance to bail and get back to work. Parallax folks, you're welcome to stay on and keep fielding questions, or to bug out if you need to. Either way, I think we all want to say a huge thank you for your time today!

We're coming up on an hour, which is usually how long we go before giving the host(s) a chance to bail and get back to work. Parallax folks, you're welcome to stay on and keep fielding questions, or to bug out if you need to. Either way, I think we all want to say a huge thank you for your time today!