-

Hack Chat Transcript, Part 3

11/10/2021 at 21:08 • 0 comments![]() I'll put you in touch with my buddy in Cad/Cam and he'll tell you how to accomplish your goals affordably!

I'll put you in touch with my buddy in Cad/Cam and he'll tell you how to accomplish your goals affordably!![]() I suppose so. ;) This has been fun guys!

I suppose so. ;) This has been fun guys!![]() Thanks @Dan Maloney

Thanks @Dan Maloney![]() thank you... sorry I missed most of it, had to pick up daughter

thank you... sorry I missed most of it, had to pick up daughter![]() You bet, thanks to you both and to everyone for the great chat!

You bet, thanks to you both and to everyone for the great chat!![]() No worries man. We do free engineering services for peeps.

No worries man. We do free engineering services for peeps.![]() I'll be posting a transcript shortly. @Dave Blundell

I'll be posting a transcript shortly. @Dave Blundell![]() Feel free to reach out to me directly at gziraldo@aapcb.com with questions as well.

Feel free to reach out to me directly at gziraldo@aapcb.com with questions as well.![]() Oh -- it was epic Dan -- probably the best hack chat ever. Wanna know why?

Oh -- it was epic Dan -- probably the best hack chat ever. Wanna know why?![]() GREG-FREAKING-ZIRALDO!

GREG-FREAKING-ZIRALDO!![]() Hip-hip!

Hip-hip!![]() Hooray!

Hooray!![]() Hip-hip!

Hip-hip!![]() Hooray!

Hooray!![]() I saw that coming...

I saw that coming...![]() Hip-hip!

Hip-hip!![]() Hooray!

Hooray!![]() Good lord. :|

Good lord. :|![]() next time, we only invite Greg

next time, we only invite Greg![]() Ouch Nicolas -- that hurt me right in the feels.

Ouch Nicolas -- that hurt me right in the feels.![]() ;)

;)![]() Ha! Cheers all, let's do this again!

Ha! Cheers all, let's do this again!![]() Cool stuff, thanks so much! We'll be taking a couple of weeks off to do Remoticon and Thanksgiving, so tune in again in December when we pick it back up. Thanks all!

Cool stuff, thanks so much! We'll be taking a couple of weeks off to do Remoticon and Thanksgiving, so tune in again in December when we pick it back up. Thanks all! -

Hack Chat Transcript, Part 2

11/10/2021 at 21:07 • 0 comments![]() @Jason - stick to one weight. The minimal value-add to your design will be drastically over shadowed by the high manufacturing cost.

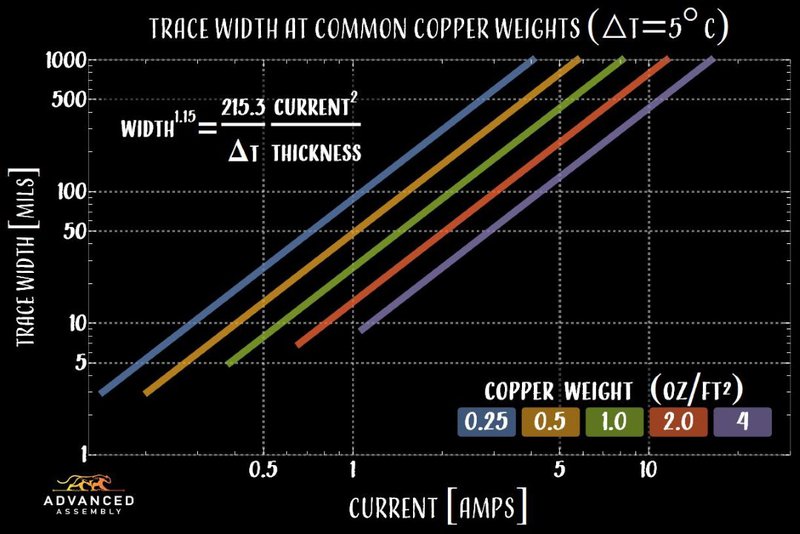

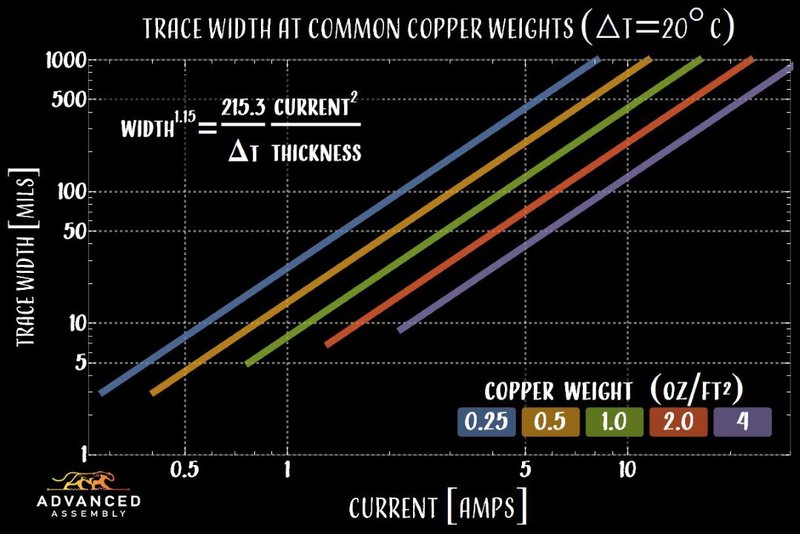

@Jason - stick to one weight. The minimal value-add to your design will be drastically over shadowed by the high manufacturing cost.![]() 3) How much current you'll put through the trace

3) How much current you'll put through the trace![]() And then you can get a great first-order estimate for your trace-width.

And then you can get a great first-order estimate for your trace-width.![]() @Greg Ziraldo but selective copper thickness is a thing and possible?

@Greg Ziraldo but selective copper thickness is a thing and possible?![]() The best part is that these equations all assume a single trace with no ground plane sucking heat away. So these are all high-end estimates.

The best part is that these equations all assume a single trace with no ground plane sucking heat away. So these are all high-end estimates.![]() @Dan Maloney What are the filesize limits on here?

@Dan Maloney What are the filesize limits on here?![]() @Greg Ziraldo - perfect thanks for the advice

@Greg Ziraldo - perfect thanks for the advice![]() Sure. Same as selective soft/hard gold plating. You would use photo resist as a mask to "build up" areas. Again...this pushes the envelope of manufacturability and more into the "arts and crafts" world.

Sure. Same as selective soft/hard gold plating. You would use photo resist as a mask to "build up" areas. Again...this pushes the envelope of manufacturability and more into the "arts and crafts" world.![]() I think this might be the same as another question but...is it easier to do select thick layers or more layers (acting in parallel). Say a 6 layer x 1 oz board using 3 layers in parallel for a particular trace or a 4 layer board with 3oz copper on top/bottom. And is there a transition point... For example, is the trade between 3x 2oz layers vs 1x 6oz layer the same?

I think this might be the same as another question but...is it easier to do select thick layers or more layers (acting in parallel). Say a 6 layer x 1 oz board using 3 layers in parallel for a particular trace or a 4 layer board with 3oz copper on top/bottom. And is there a transition point... For example, is the trade between 3x 2oz layers vs 1x 6oz layer the same?![]() I'm not sure, actually. Don't think we've ever run up against a limit before.

I'm not sure, actually. Don't think we've ever run up against a limit before.![]() See Greg -- they're all pinging you man. I stand in the shadow of your greatness once again.

See Greg -- they're all pinging you man. I stand in the shadow of your greatness once again.![]() Give it a shot and we'll see

Give it a shot and we'll see![]() Perhaps once, the winds will blow and you'll sway, and I shall grab a glimpse of the light that shines around you.

Perhaps once, the winds will blow and you'll sway, and I shall grab a glimpse of the light that shines around you.![]() Whatever Mark. ;)

Whatever Mark. ;)![]()

AdvancedAssembly_HeavyCopperCalculations_001-100C_WonB.zip

9 MB

![]() So somewhere north of 9MB, I guess ;-)

So somewhere north of 9MB, I guess ;-)![]() Okay -- I just uploaded a file Greg and I created programmatically for a variety of copper weights, temp increases and what not. Enjoy!

Okay -- I just uploaded a file Greg and I created programmatically for a variety of copper weights, temp increases and what not. Enjoy!![]() @Kearney Lackas That brings up a good point. If you don't have room to run the copper all on one layer, you can split it across multiple layers. It is very important that you keep your stackup balanced symmetrically around the mid-plane

@Kearney Lackas That brings up a good point. If you don't have room to run the copper all on one layer, you can split it across multiple layers. It is very important that you keep your stackup balanced symmetrically around the mid-plane![]() Otherwise the part will turn into a potato chip during reflow.

Otherwise the part will turn into a potato chip during reflow.![]() Here's something else to consider. Good luck doing rework on a heavy copper trace.

Here's something else to consider. Good luck doing rework on a heavy copper trace.![]() @Kearney Lackas additionally the lower your copper weight it, the easier to etch, the easier to fabricate, ultimately giving you far better yields, repeatability and of course cost.

@Kearney Lackas additionally the lower your copper weight it, the easier to etch, the easier to fabricate, ultimately giving you far better yields, repeatability and of course cost.![]() Copper absorbs heat better than any metal other than silver.

Copper absorbs heat better than any metal other than silver.![]() Nice file thanks. Do you have a good reference to available PC bus bars? Rogers (maybe) used to make some. I haven't looked in years.

Nice file thanks. Do you have a good reference to available PC bus bars? Rogers (maybe) used to make some. I haven't looked in years.![]() I tend to reference Douglas Brooke's a lot for this sort of thing.

I tend to reference Douglas Brooke's a lot for this sort of thing.![]() @Mark J Hughes - +75C max ambient and +5C temp rise (guesstimate), 25A max steady state, 75A peak for 1s.

@Mark J Hughes - +75C max ambient and +5C temp rise (guesstimate), 25A max steady state, 75A peak for 1s.![]() He's got a lot of free articles on his website -- I haven't looked to see if bus-bars are free lately.

He's got a lot of free articles on his website -- I haven't looked to see if bus-bars are free lately.![]() But I'm sure he's got them in his textbook.

But I'm sure he's got them in his textbook.![]() Great point Mark. We have been talking PCB, we have not even started talking about populating high Cu PCBAs! *custom reflow profiles have entered the chat*

Great point Mark. We have been talking PCB, we have not even started talking about populating high Cu PCBAs! *custom reflow profiles have entered the chat*![]() Here's his textbook.

Here's his textbook.![]()

PCB Design Guide to Via and Trace Currents and Temperatures

PCB Design Guide to Via and Trace Currents and Temperatures [Douglas Brooks, Johannes Adam] on Amazon.com. *FREE* shipping on qualifying offers. PCB Design Guide to Via and Trace Currents and Temperatures

![]() @Jason -- what's the duty-cycle of the 75A peak?

@Jason -- what's the duty-cycle of the 75A peak?![]() You can get a weighted average current 25A + 75A*(duty cycle) to get current requirements.

You can get a weighted average current 25A + 75A*(duty cycle) to get current requirements.![]() @Mark J Hughes, - good point, only very low duty. not enough to contribute significantly before dissipating

@Mark J Hughes, - good point, only very low duty. not enough to contribute significantly before dissipating![]() Also -- you can dump as much energy as you want through a smaller trace as long as you are able to dissipate the heat elsewhere. For example, ever heard of copper heat pipes?

Also -- you can dump as much energy as you want through a smaller trace as long as you are able to dissipate the heat elsewhere. For example, ever heard of copper heat pipes?![]()

![]()

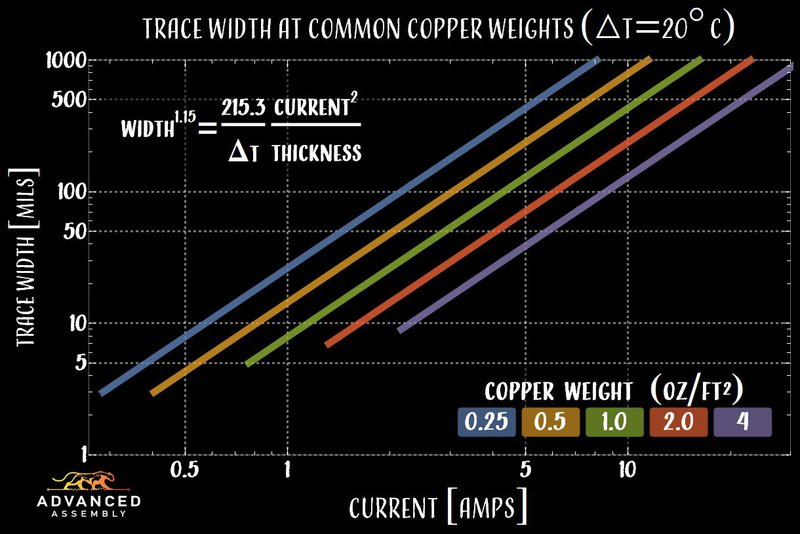

![]() A 5°C delta T isn't a lot to play with at high operating temps.

A 5°C delta T isn't a lot to play with at high operating temps.![]() As you can see, on 4 oz copper, you'd only want to run 10 Amps through a trace that's 500 mil wide. That's a lot of board area, and we're not every to 25 yet.

As you can see, on 4 oz copper, you'd only want to run 10 Amps through a trace that's 500 mil wide. That's a lot of board area, and we're not every to 25 yet.![]() So one option is to put that current through multiple layers on your PCB.

So one option is to put that current through multiple layers on your PCB.![]() Lets say you've got a 6 layer board.

Lets say you've got a 6 layer board.![]() A few different ways you could do it, but lets say you run power traces on layers 1, 3, 4, and 6 with ground returns for 2 and 6.

A few different ways you could do it, but lets say you run power traces on layers 1, 3, 4, and 6 with ground returns for 2 and 6.![]() You'll have decent power integrity and the ground planes on 2 and 5 can help to dissipate the thermal energy.

You'll have decent power integrity and the ground planes on 2 and 5 can help to dissipate the thermal energy.![]() Really though, at 75°C with a 5 °C delta T -- you need to do FEA or LEA.

Really though, at 75°C with a 5 °C delta T -- you need to do FEA or LEA.![]() Greg, I've scared them.

Greg, I've scared them.![]() They've got quiet.

They've got quiet.![]() Come back Greg.

Come back Greg.![]() Let the light that you shine be seen!

Let the light that you shine be seen!![]() are there open source options for PCB analysis? not just for thermal analysis, but also for e.g. power system impedance?

are there open source options for PCB analysis? not just for thermal analysis, but also for e.g. power system impedance?![]() @Mark J Hughes - sounds good. Looking to distribute the power to multiple locations on the board and they will alternate which location is drawing the peak power over time. Will touch base when further down the design road.

@Mark J Hughes - sounds good. Looking to distribute the power to multiple locations on the board and they will alternate which location is drawing the peak power over time. Will touch base when further down the design road.![]() Never left sir!

Never left sir!![]() @Christoph I'm sure there are, but I am not aware of any. I'll tell you who is though -- Dr. Eric Bogatin -- he's on a mission to find free tools for students.

@Christoph I'm sure there are, but I am not aware of any. I'll tell you who is though -- Dr. Eric Bogatin -- he's on a mission to find free tools for students.![]() @Christoph I've been trying to do some analysis like that with Elmer, which theoretically supports a bunch of relevant PCB physics, but isn't at all user friendly

@Christoph I've been trying to do some analysis like that with Elmer, which theoretically supports a bunch of relevant PCB physics, but isn't at all user friendly![]() @Jason Hey man -- we'd love to work with you.

@Jason Hey man -- we'd love to work with you.![]() Just wondering if it would be possible to make a DIY process based on ultra-low-cost (2$ JLCPCB or so) standard PCBs like this:

Just wondering if it would be possible to make a DIY process based on ultra-low-cost (2$ JLCPCB or so) standard PCBs like this:* Design board with no solder mask on actual (high-current) traces

* Add thin dummy traces (with solder mask) to connect all traces together

* Use electroplating to add extra copper to the traces, should only deposit copper on the traces (where there is no solder mask)

* Drill away dummy traces (might help to have a pre-drilled hole to center the drill bit, removing traces like that was pretty easy with the good old strip grid prototyping boards back in the days)

One potential problem I see with this is that the cheap PCBs will always come with some kind of plating (typically HASL), you can't opt out of this. Not sure if the electroplating process would work on top of the HASL (tin) finish.

![]() @Christoph https://www.signalintegrityjournal.com/articles/2026-low-cost-and-free-tools-fit-for-an-engineers-personal-budget

@Christoph https://www.signalintegrityjournal.com/articles/2026-low-cost-and-free-tools-fit-for-an-engineers-personal-budget![]() @Jakob are you doing this for fun? Or trying to make something to market?

@Jakob are you doing this for fun? Or trying to make something to market?![]() ooooh that looks like a good start. thank you

ooooh that looks like a good start. thank you![]() Whoa, just had a crazy reflow idea that you "could" have the SMD component sit so high like a bridge that you could have other components underneath it. Very impractical but a fun show piece. That begs the question, what reflow considerations besides warp and proper pre-heating are needed for sitting so high off the substrate, if any?

Whoa, just had a crazy reflow idea that you "could" have the SMD component sit so high like a bridge that you could have other components underneath it. Very impractical but a fun show piece. That begs the question, what reflow considerations besides warp and proper pre-heating are needed for sitting so high off the substrate, if any?![]() @Jakob Simple answer is yes, but goes straight into the custom world. From a POC standpoint, it can be done.

@Jakob Simple answer is yes, but goes straight into the custom world. From a POC standpoint, it can be done.![]() I'd do that for hobby projects only, for commercial projects it would probably be a lot more cost effective to just order a professional board.

I'd do that for hobby projects only, for commercial projects it would probably be a lot more cost effective to just order a professional board.![]() Yes, agree. But would be really cool to make!

Yes, agree. But would be really cool to make!![]() @Jakob I'd still just buy it from someone. It's not worth the aggregation and setup costs.

@Jakob I'd still just buy it from someone. It's not worth the aggregation and setup costs.![]() *aggrevation.

*aggrevation.![]() @Greg Ziraldo Would you expect any problems with electroplating copper on top of the HASL finish?

@Greg Ziraldo Would you expect any problems with electroplating copper on top of the HASL finish?![]() You mean like delamination?

You mean like delamination?![]() Yes. You can expect that....if it even manages to stick in the first place.

Yes. You can expect that....if it even manages to stick in the first place.![]() Yes. I know electroplating can be tricky depending on the combination of materials used.

Yes. I know electroplating can be tricky depending on the combination of materials used.![]() It's not just chemistry.

It's not just chemistry.![]() The crystal structure of the copper comes into play.

The crystal structure of the copper comes into play.![]() Getting copper to plate to other copper at a grain boundary is hard enough -- but with the HASL in the middle, I personally don't see it happening.

Getting copper to plate to other copper at a grain boundary is hard enough -- but with the HASL in the middle, I personally don't see it happening.![]() You would not be able to plate to HASL. There might be an electroless deposition, but not thru electroplating.

You would not be able to plate to HASL. There might be an electroless deposition, but not thru electroplating.![]() Maybe you can get some boards with OSP that you can clean before your experiment?

Maybe you can get some boards with OSP that you can clean before your experiment?![]() Alright -- what other heavy-copper questions do you have? It's not often that Greg Ziraldo is in your presence.

Alright -- what other heavy-copper questions do you have? It's not often that Greg Ziraldo is in your presence.![]() Three cheers for Greg Ziraldo.

Three cheers for Greg Ziraldo.Hip.hip.....

![]() I understand. Do you think an ENIG finish (with a few micrometers of gold on top) would work better if you want to electroplate copper on top of it? Still a lot cheaper than ordering a professional 4Oz/6Oz PCB.

I understand. Do you think an ENIG finish (with a few micrometers of gold on top) would work better if you want to electroplate copper on top of it? Still a lot cheaper than ordering a professional 4Oz/6Oz PCB.![]() @Jakob You need clean, unoxidized copper.

@Jakob You need clean, unoxidized copper.![]() I know it's not quite heavy copper, but I have a few questions on MCPCB tech

I know it's not quite heavy copper, but I have a few questions on MCPCB tech![]() fair game?

fair game?![]() Go for it.

Go for it.![]() I've seen two primary MCPCB tech available

I've seen two primary MCPCB tech available![]() First question is why do you want it?

First question is why do you want it?![]() copper - substrate - metal - substrate - copper

copper - substrate - metal - substrate - copper![]() and copper - substrate - copper - substrate - metal

and copper - substrate - copper - substrate - metal![]() metal in middle vs. multilayer PCB laminated to metal

metal in middle vs. multilayer PCB laminated to metal![]() I'm always a fan of using balanced stackups -- otherwise differential coefficients of thermal expansion during reflow can cause warpage. Can't put flat parts on a curved surface.

I'm always a fan of using balanced stackups -- otherwise differential coefficients of thermal expansion during reflow can cause warpage. Can't put flat parts on a curved surface.![]() One of the bugbears of my design existence has been a SSR for automotive use specced to handle 100-120A continuous

One of the bugbears of my design existence has been a SSR for automotive use specced to handle 100-120A continuous![]() Now -- there are simulators that can allow you to balance that out. But most people don't have access to one.

Now -- there are simulators that can allow you to balance that out. But most people don't have access to one.![]() 100-120 continuous? Sheesh.

100-120 continuous? Sheesh.![]() OTOH, with metal core, balanced implies "way more difficult via fabrication" no?

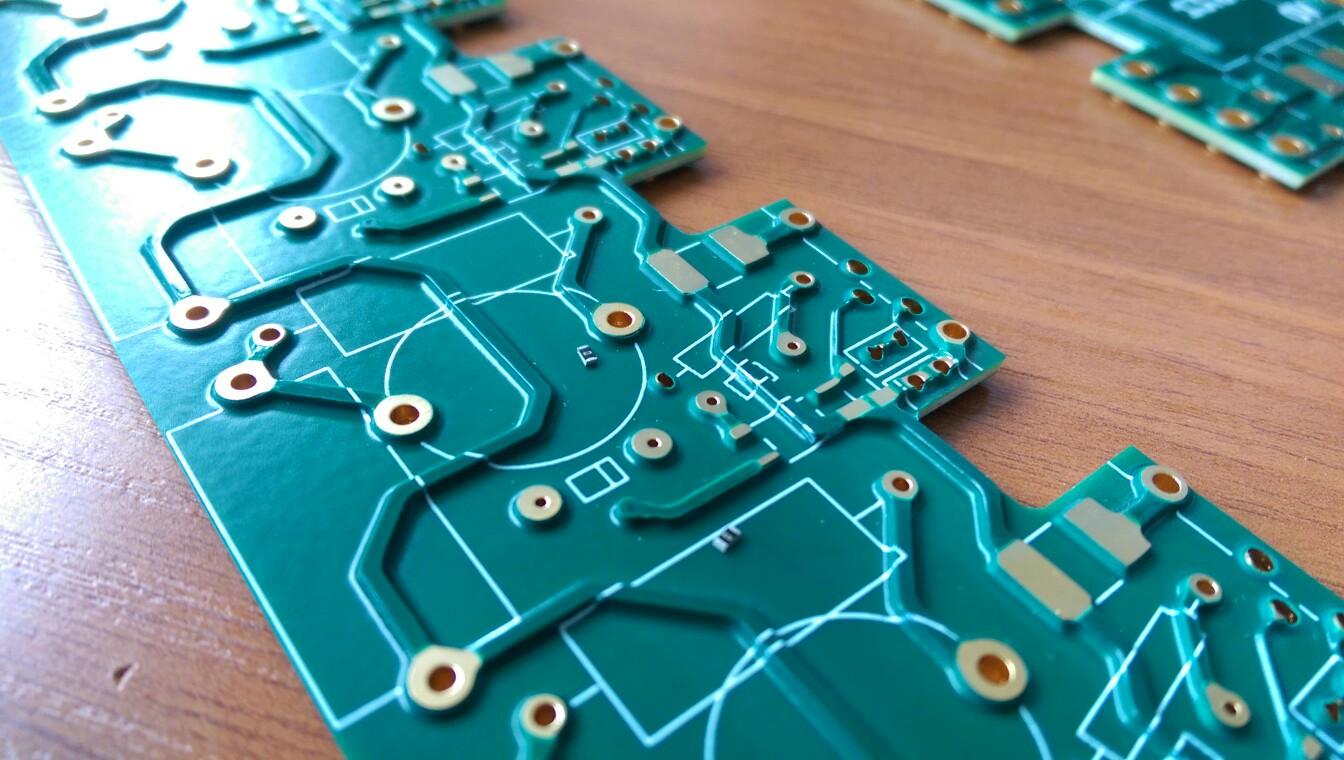

OTOH, with metal core, balanced implies "way more difficult via fabrication" no?![]() so far, the most successful PCB I've done with SMT parts had several pieces of .25" square copper placed on the board as busbar and soldered reflow style after an acid wash to improve sodlerability

so far, the most successful PCB I've done with SMT parts had several pieces of .25" square copper placed on the board as busbar and soldered reflow style after an acid wash to improve sodlerability![]() You can certainly use a solid copper core or or "bottom layer" of the stack up. This would be for heat sink/thermal dissipation?

You can certainly use a solid copper core or or "bottom layer" of the stack up. This would be for heat sink/thermal dissipation?![]() yeah, I used an osh part 2oz board with the extra busbar

yeah, I used an osh part 2oz board with the extra busbar![]() What greg said -- just use copper pours on the opposite layer--doesn't have to be continuous.

What greg said -- just use copper pours on the opposite layer--doesn't have to be continuous.![]() Guess who makes OshPark's boards?

Guess who makes OshPark's boards?![]() without the busbar, the 2oz board would get nuked in certain spots due to uneven current/thermal distribution

without the busbar, the 2oz board would get nuked in certain spots due to uneven current/thermal distribution![]() The designs that I have worked with have either defense/missile or down-hole drilling applications.

The designs that I have worked with have either defense/missile or down-hole drilling applications.![]() osh park? amitron in chicago

osh park? amitron in chicago![]() mostly

mostly![]() That's right. GREG-freaking-ZIRALDO!

That's right. GREG-freaking-ZIRALDO!![]() Out of our Royal Circuits facility in Hollister, Ca.

Out of our Royal Circuits facility in Hollister, Ca.![]() the ones I got are 95% from Amitron in chicago

the ones I got are 95% from Amitron in chicago![]() I order a lot of full panels from Osh and get drop ships from fab

I order a lot of full panels from Osh and get drop ships from fab![]() All of a sudden it's an hour later! Greg, Mark, I assume you've got to get back to work? Those PCBs aren't going to quick-turn themselves, right?

All of a sudden it's an hour later! Greg, Mark, I assume you've got to get back to work? Those PCBs aren't going to quick-turn themselves, right?![]() Ah.

Ah.![]() Well @Dave Blundell do me a favor and email me at mhughes@royalcircuits.com and we'll follow up one-on-one.

Well @Dave Blundell do me a favor and email me at mhughes@royalcircuits.com and we'll follow up one-on-one.![]() is there a compelling reason why PTH are never connected to MCPCB

is there a compelling reason why PTH are never connected to MCPCB![]() Thanks guys

Thanks guys![]() thanks @Mark J Hughes will do

thanks @Mark J Hughes will do![]()

Hack Chat Transcript, Part 1

11/10/2021 at 21:06 • 0 comments![]() OK, everyone, let's get started. I'm Dan and I'll be the moderator today along with Dusan for Mark Hughes and Greg Ziraldo. They're both from Advanced Assembly and they're here today to talk about big copper. Welcome!

OK, everyone, let's get started. I'm Dan and I'll be the moderator today along with Dusan for Mark Hughes and Greg Ziraldo. They're both from Advanced Assembly and they're here today to talk about big copper. Welcome!![]() Hi everyone! I'm Mark

Hi everyone! I'm Mark![]() Hi, Mark...

Hi, Mark...![]() I work with Greg at Advanced Assembly in beautiful Auroroa, Colorado. We are the original quick-turn industry experts, and we make boards as fast as you need them -- including in a single shift.

I work with Greg at Advanced Assembly in beautiful Auroroa, Colorado. We are the original quick-turn industry experts, and we make boards as fast as you need them -- including in a single shift.![]() So maybe we can start with a little about your backgrounds?

So maybe we can start with a little about your backgrounds?![]() I type too slow ;-)

I type too slow ;-)![]() We're so big, we have our own pick teams at the major parts distributors -- so your parts are likely going to show up the same morning that your parts are.

We're so big, we have our own pick teams at the major parts distributors -- so your parts are likely going to show up the same morning that your parts are.![]() We can stuff 'em and get 'em back on the plane back out to you.

We can stuff 'em and get 'em back on the plane back out to you.![]() We're here to answer anything you want to know about Heavy Copper (generally regarded as 1.5 oz or greater)

We're here to answer anything you want to know about Heavy Copper (generally regarded as 1.5 oz or greater)![]() And we can help you solve any other PCB and PCBA problems you might have.

And we can help you solve any other PCB and PCBA problems you might have.![]() Glad to be here Dan! Hi everyone, I'm Greg. I am over Operations (engineering, manufacturing and supply chain) at Advanced Assembly. I have been with AA for a little over 4 years and I have been in the high-reliability side of EMS for nearly 18 years.

Glad to be here Dan! Hi everyone, I'm Greg. I am over Operations (engineering, manufacturing and supply chain) at Advanced Assembly. I have been with AA for a little over 4 years and I have been in the high-reliability side of EMS for nearly 18 years.![]() So the line between heavy and regular copper is pretty slim, right? Aren't most boards 1-oz?

So the line between heavy and regular copper is pretty slim, right? Aren't most boards 1-oz?![]() I've got this Greg.

I've got this Greg.![]() Most boards are 0.5 oz to 1 oz and are plated with an additional 0.5-0.7-1.0 oz of copper (to make the vias).

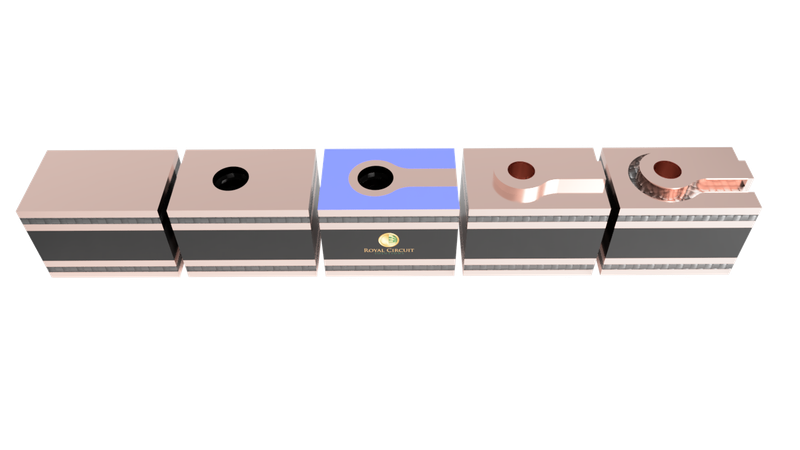

Most boards are 0.5 oz to 1 oz and are plated with an additional 0.5-0.7-1.0 oz of copper (to make the vias).![]() My main question is, that ludicrous board with 3D soldermask: is most of that copper weight plated (I think it was 12oz)?

My main question is, that ludicrous board with 3D soldermask: is most of that copper weight plated (I think it was 12oz)?![]()

![]()

![]() I'm looking for a better graphic to illustrate the point.

I'm looking for a better graphic to illustrate the point.![]() The board in the picture I used was a 20-oz board, IIRC

The board in the picture I used was a 20-oz board, IIRC![]() That is too many ounces.

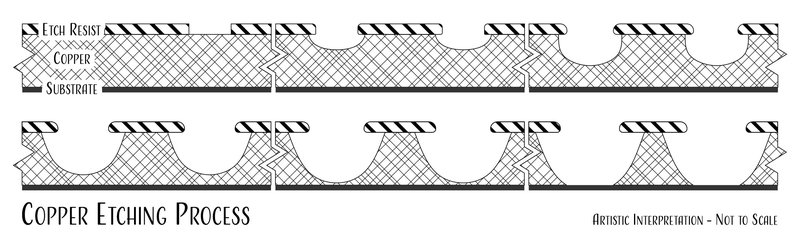

That is too many ounces.![]() But all boards start out as copper sheets, we put a photo-imagable mask on it, and project a negative image of your artwork with fancy scanning lasers. That makes the mask tough and impenetrable.

But all boards start out as copper sheets, we put a photo-imagable mask on it, and project a negative image of your artwork with fancy scanning lasers. That makes the mask tough and impenetrable.![]() Just an impossible number of ounces.

Just an impossible number of ounces.![]()

https://hackaday.com/2016/12/16/massive-20-oz-copper-pcb-enables-electric-racing/

Massive 20-oz. Copper PCB Enables Electric Racing

Is twenty times the copper twenty times as much fun to work with? Ask [limpkin] and follow along as he fabricates a DC/DC block for a Formula E race car on 20-oz copper PCBs. The typical boards you order from OSH Park and the like usually come with 1-ounce copper - that's one ounce of copper cladding per square foot of board.

![]() Then it goes in electroplating tanks where we build up the traces and vias.

Then it goes in electroplating tanks where we build up the traces and vias.![]() I my experience that would have to plated up. I have never seen a board with that high of Cu weight!

I my experience that would have to plated up. I have never seen a board with that high of Cu weight!![]() What's the heaviest y

What's the heaviest y![]() y'all do?

y'all do?![]() Finally, we put the whole thing in a tank of acid and etch away copper from everywhere. The parts we plated survive the etch.

Finally, we put the whole thing in a tank of acid and etch away copper from everywhere. The parts we plated survive the etch.![]() Plating takes time.

Plating takes time.![]() 4-6oz is the safe area

4-6oz is the safe area![]() We have 4 oz sitting on the shelf right now, usually, but not always have 6oz on hand too. Then that can be plated up.

We have 4 oz sitting on the shelf right now, usually, but not always have 6oz on hand too. Then that can be plated up.![]() But.

But.![]() 4 oz can be bought of the shelf without plating.

4 oz can be bought of the shelf without plating.![]() There's a lot of reasons you shouldn't.

There's a lot of reasons you shouldn't.![]() How long would that take? Seems like electroplating is a slow process. I'd think slow is the last thing you want in a quick-turn environment.

How long would that take? Seems like electroplating is a slow process. I'd think slow is the last thing you want in a quick-turn environment.![]() I mean, the biggest reason is that Greg will make fun of you. And you dont' want that.

I mean, the biggest reason is that Greg will make fun of you. And you dont' want that.![]() I imagine minimum trace clearances and traces widths increase with copper weight. What are general rule of thumbs for say 4 oz and 6 oz?

I imagine minimum trace clearances and traces widths increase with copper weight. What are general rule of thumbs for say 4 oz and 6 oz?![]() We've got some cool pulse-plating tech. But it'll add a couple days to your turn time.

We've got some cool pulse-plating tech. But it'll add a couple days to your turn time.![]() Assuming with very thick copper on pcbs, that it's still etched, does the etchant not try to eat into the sides of the traces, because they're so tall vertically? (hope that makes sense)

Assuming with very thick copper on pcbs, that it's still etched, does the etchant not try to eat into the sides of the traces, because they're so tall vertically? (hope that makes sense)![]() DC plating can take ~2+ hours per basket. Pulse plating cuts that in half and better plating control.

DC plating can take ~2+ hours per basket. Pulse plating cuts that in half and better plating control.![]() To the designers out there, what applications are you using heavy copper in your stack up for?

To the designers out there, what applications are you using heavy copper in your stack up for?![]()

![]()

![]() @anfractuosity yes!

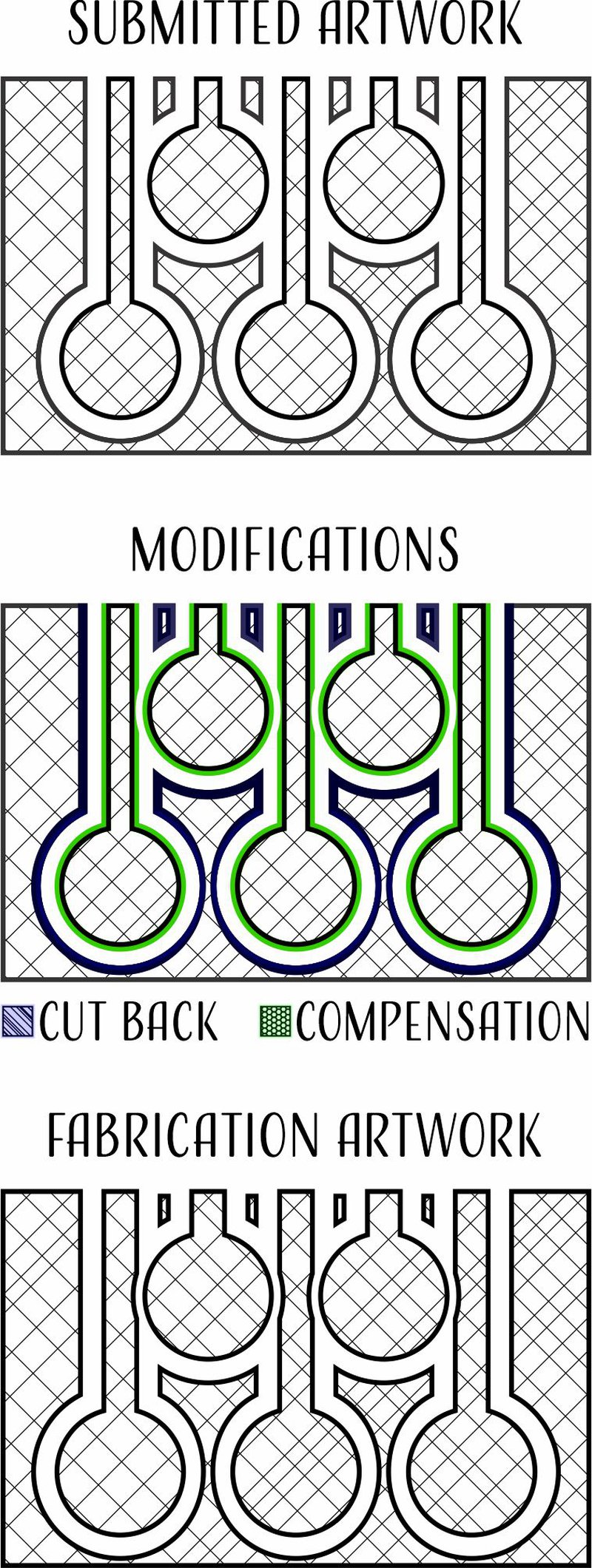

@anfractuosity yes!![]() So there is etch compensation performed on all your artwork.

So there is etch compensation performed on all your artwork.![]() The dreaded undercutting

The dreaded undercutting![]() Yes ^^^

Yes ^^^![]() That will roll the trace right off of the laminate.

That will roll the trace right off of the laminate.![]() interesting cheers, 'etch compensation' means you make the traces appear a bit larger than necessary?

interesting cheers, 'etch compensation' means you make the traces appear a bit larger than necessary?![]() Yeah -- let me find you a pic to clear it up.

Yeah -- let me find you a pic to clear it up.![]() @Greg Ziraldo : how do you handle vias for high current?

@Greg Ziraldo : how do you handle vias for high current?![]() What do you mean @echogee?

What do you mean @echogee?![]() Greg's is a Grade-A fabricator. You call 'em out, he'll make 'em.

Greg's is a Grade-A fabricator. You call 'em out, he'll make 'em.![]() A robust via design starts with drill size, aspect ratio of the hole to the material thickness and via fill if VIP is part of your design.

A robust via design starts with drill size, aspect ratio of the hole to the material thickness and via fill if VIP is part of your design.![]()

![]()

![]() Traditional vias are 0.5oz thick right? So if current is supposed to transfer between layers, you'd need thicker vias ?

Traditional vias are 0.5oz thick right? So if current is supposed to transfer between layers, you'd need thicker vias ?![]() @echogee is this high-frequency current?

@echogee is this high-frequency current?![]() nope. just HIGH current

nope. just HIGH current![]() Class 3 is 0.001" of copper in the barrel.

Class 3 is 0.001" of copper in the barrel.![]() Almost seems like there would be through-hole copper rivets for such an application.

Almost seems like there would be through-hole copper rivets for such an application.![]() You're better off using multiple vias to reduce inductance. If it's high frequency AC, then the current travels along the outer barrel walls. You can fill the vias with cat crap for all the good it'll do you.

You're better off using multiple vias to reduce inductance. If it's high frequency AC, then the current travels along the outer barrel walls. You can fill the vias with cat crap for all the good it'll do you.![]() As for temperature of the via -- it'll closely match the trace temperature above and below the via.

As for temperature of the via -- it'll closely match the trace temperature above and below the via.![]() The Via doesn't heat up hotter than the trace.

The Via doesn't heat up hotter than the trace.![]() Source (https://amzn.to/3qvZ7mV)

Source (https://amzn.to/3qvZ7mV)![]() Crap...referrer link again.

Crap...referrer link again.![]() Let me fix that.

Let me fix that.![]() True. Your dielectric thickness is going to really come in to play here as well. High current must have appropriate layer to layer insulation

True. Your dielectric thickness is going to really come in to play here as well. High current must have appropriate layer to layer insulation![]()

PCB Design Guide to Via and Trace Currents and Temperatures

PCB Design Guide to Via and Trace Currents and Temperatures [Douglas Brooks, Johannes Adam] on Amazon.com. *FREE* shipping on qualifying offers. PCB Design Guide to Via and Trace Currents and Temperatures

![]() That actually brings up a question someone posted on the announcement page:

That actually brings up a question someone posted on the announcement page:Don’t forget the effect of skin depth: Past a few hundred kHz, adding thickness to a trace doesn’t buy you any more conductivity. You need to add width (or Litz techniques) to get more conductivity.

![]() Not a question so much as an observation, I suppose

Not a question so much as an observation, I suppose![]() Litz is a wire-weaving technique. I don't know how you'd apply that to individual traces.

Litz is a wire-weaving technique. I don't know how you'd apply that to individual traces.![]() But at high frequencies, you also need smooth copper, and the surface roughness becomes a factor.

But at high frequencies, you also need smooth copper, and the surface roughness becomes a factor.![]() Have we missed any questions along the way?

Have we missed any questions along the way?![]() @Greg Ziraldo : So thicker copper pcbs mostly use 0.5oz vias and multiple of them?

@Greg Ziraldo : So thicker copper pcbs mostly use 0.5oz vias and multiple of them?![]() Seems like resistance of typical 0.2mm via is 1-2 mOhm

Seems like resistance of typical 0.2mm via is 1-2 mOhm![]() Not sure how to answer that one. @Mark J Hughes ?

Not sure how to answer that one. @Mark J Hughes ?![]() Sure -- but he keeps pinging you.

Sure -- but he keeps pinging you.![]() :)

:)![]() In the example, PCB for the Formula E DC/DC it seems like there is lots of extra space to widen several traces vs building them higher. Would you suggest a lower weight and wider trace in that case?

In the example, PCB for the Formula E DC/DC it seems like there is lots of extra space to widen several traces vs building them higher. Would you suggest a lower weight and wider trace in that case?![]() Yes -- you're better off using multiple vias than one giant one.

Yes -- you're better off using multiple vias than one giant one.![]() @Jason The example was something Greg and I laughed at. It's ridiculous.

@Jason The example was something Greg and I laughed at. It's ridiculous.![]() Yes -- there is a trade off between copper width and height.

Yes -- there is a trade off between copper width and height.![]() But it's not linear.

But it's not linear.![]() IPC-2221 used to be the designers bible for how to design trace thickness for a given weight of copper.

IPC-2221 used to be the designers bible for how to design trace thickness for a given weight of copper.![]() On this page https://hackaday.com/2016/12/16/massive-20-oz-copper-pcb-enables-electric-racing/ the board price is $2250. How much of that is the large size (it looks large anyway) and how much is the extra plating? Is there some rule of thumb for adding X oz of copper per square inch of board (even if all of that square inch is not traces of course)?

On this page https://hackaday.com/2016/12/16/massive-20-oz-copper-pcb-enables-electric-racing/ the board price is $2250. How much of that is the large size (it looks large anyway) and how much is the extra plating? Is there some rule of thumb for adding X oz of copper per square inch of board (even if all of that square inch is not traces of course)?![]() The trouble is that it was based on some data collected by two underfunded scientists in the 50's/60's who made some of the data up because they didn't have money to run the experiments.

The trouble is that it was based on some data collected by two underfunded scientists in the 50's/60's who made some of the data up because they didn't have money to run the experiments.![]() The whole "inner traces need to be twice as wide as outer traces" -- complete rubbish.

The whole "inner traces need to be twice as wide as outer traces" -- complete rubbish.![]() So about a decade ago, IPC-2152 committe did some experiments and generated new empiracle data

So about a decade ago, IPC-2152 committe did some experiments and generated new empiracle data![]() (BTW -- most online calculators still reference IPC-2221, don't use them)

(BTW -- most online calculators still reference IPC-2221, don't use them)![]() @bboyes the material cost of the copper is insignificant compared to the manufacturing processes and labor to complete that.

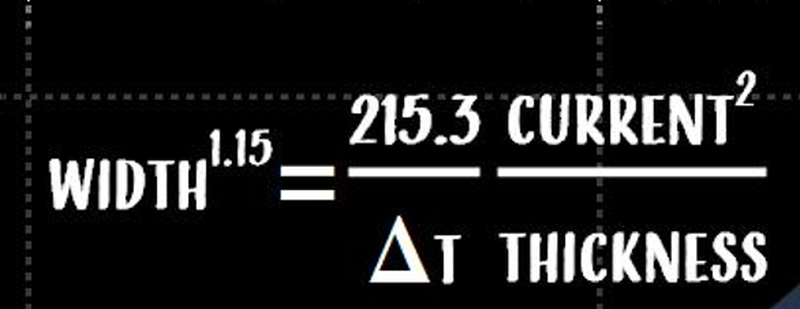

@bboyes the material cost of the copper is insignificant compared to the manufacturing processes and labor to complete that.![]() They found a relationship between trace temp rise, copper weight and trace width.

They found a relationship between trace temp rise, copper weight and trace width.![]()

![]()

![]() Greg and I rearranged the equations using two techniques.

Greg and I rearranged the equations using two techniques.![]() 1) I used math.

1) I used math.![]() 2) Greg used pure force of will.

2) Greg used pure force of will.![]()

![]()

![]() Got it. Is selective heavy copper an option worth considering or would it be better to stick with one weight? Would there be a likely quantity crossover where it is viable from a production standpoint?

Got it. Is selective heavy copper an option worth considering or would it be better to stick with one weight? Would there be a likely quantity crossover where it is viable from a production standpoint?![]() And we generated new graphics that don't appear in IPC-2152, or much of anywhere else yet.

And we generated new graphics that don't appear in IPC-2152, or much of anywhere else yet.![]() I mean the data is out there, we didn't make that.

I mean the data is out there, we didn't make that.![]()

![]()

where Tesla used a bunch of SMD bus bars to increase current handling. Didn't even realize such a thing exists but here we are.![]() There we go.

There we go.![]() Alright -- so when picking a trace width, you've got a few factors to consider.

Alright -- so when picking a trace width, you've got a few factors to consider.![]() 1) How much of a temperature rise you're willing to allow on your design

1) How much of a temperature rise you're willing to allow on your design![]() 2) What copper weight you plan to use

2) What copper weight you plan to use![]() @Jason - stick to one weight. The minimal value-add to your design will be drastically over shadowed by the high manufacturing cost.

@Jason - stick to one weight. The minimal value-add to your design will be drastically over shadowed by the high manufacturing cost.![]() 3) How much current you'll put through the trace

3) How much current you'll put through the trace![]()

Lutetium

Lutetium