The last log shows a preliminary shift register using 6 transistors per bit. For early Germanium technology this means that each complete clock would require about 100 PNP and 200 NPN.

PNP are now in stock but early "black glass" NPN are another story, a sad one : I just found that the stocks have now melted and the prices are increasing significantly ! I have just enough parts to test a few partial circuits...

If anyone can find affordable stock of OC139, OC140 or OC141 please contact me !

With the waning stock and perspective of suitable NPNs, I have to go back to the drawing board and finally design a bit cell that

- uses as few PNP as possible. Probably not 2 because the complexity is then pushed to more diodes and capacitors.

- dumps the concept of master-slave latches, to use fewer parts

I have met many problems with the classic flip-flop because of the metastabilities but I have two new insights and techniques to introduce :

- Adding a simple resistor at the middle of the cell (between both emitters and power) turns the FF into a "modified differential amplifier" and this could drastically reduce the metastabilities.

- I now understand better how a bipolar transistor could work as a "pass gate". This is a great trick to reduce the cell size because there would be only one point where data is forced into the FF, instead of 2 usually.

So there is still a chance to come up with something practical...

So let's start with a differential amplifier.

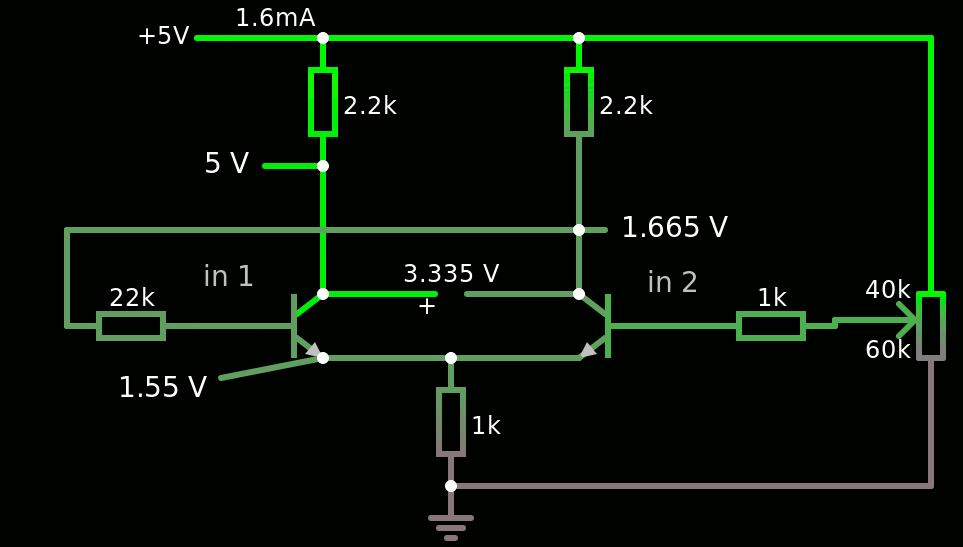

Here I have looped one branch to the other, to provide some feedback and hysteresis, this creates about 500mV of hysteresis @5V.

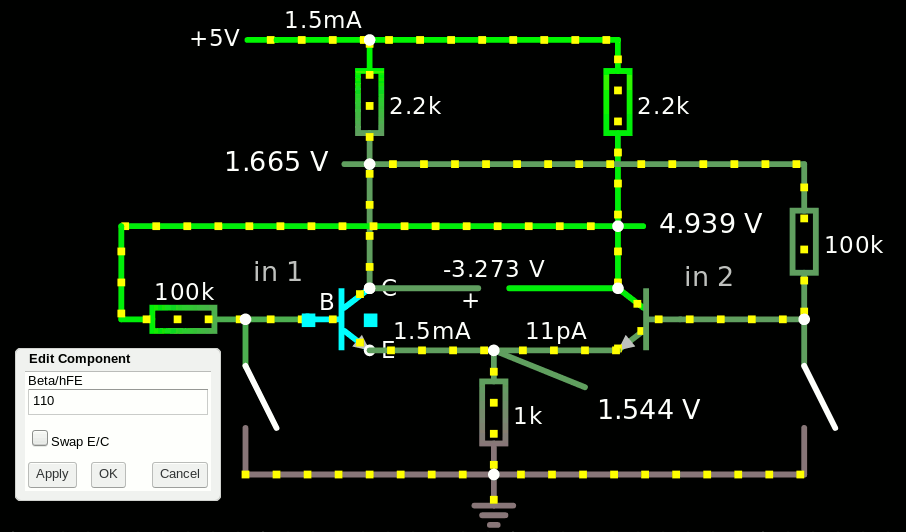

From there it is easy to loop the other "leg" back to the first and create a bistable circuit, except for the extra common resistor at the emitter. This will help in many ways, and hint Falstad at the much weaker metastability.

But it's still metastable : this sim initialises in "both conducting" state. There is some difference between the legs (360mV) but this is not enough to "flip hard".

The imbalance of the resistors should be higher then. But it doesn't solve the problem because then, the system is not bistable anymore...

I made a different change to manage the imbalance, by changing the gain :

the default value is 100 and a 10% variation is "normal". This helps the circuit become bistable again, even though it still initialises in metastable state...

Finally there is a different method to initialise the circuit with a well-defined state : the following circuit has a RC time delay on one branch so the imbalance occurs only during power-up. The transistors' gains don't matter much now.

It's still not a solution to the dynamic metastability problem but it opens another interesting prospect !

A whole block of latches can be reset directly by a complementary transistor that connects all the pull resistors. Previously I wanted to use a diode connected to the base of one of the transistors, but this diode would be connected to a common transistor. Here, I can avoid all the diodes, and the transistor can have the same rating, though it is ON all the time.

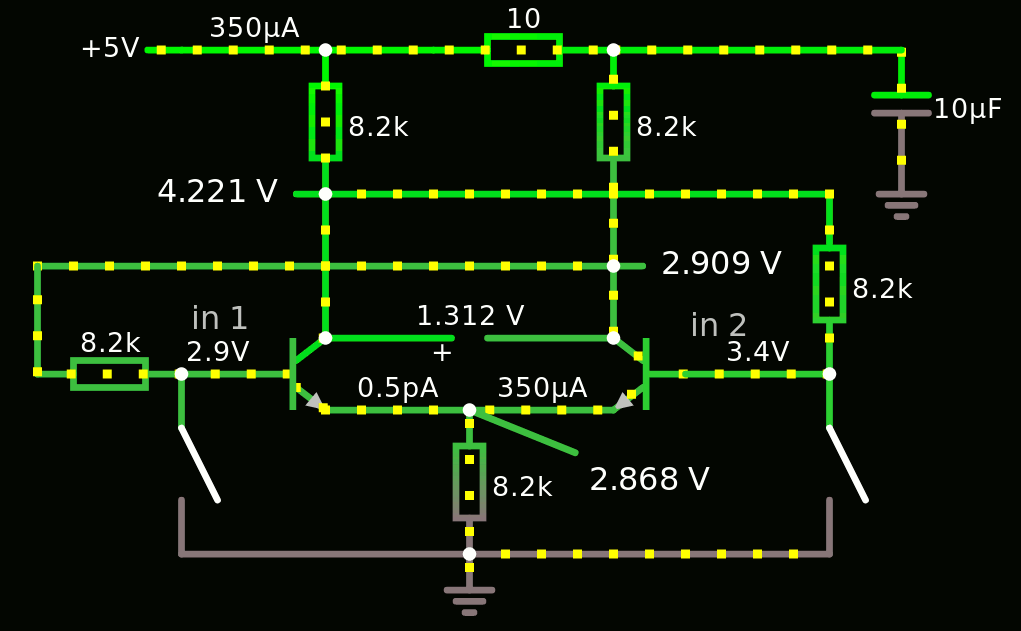

From there a more complete FF can be built :

It uses a single type/value of resistor, replicated by 6 : here I have chosen 8K2 because I just found a lot of vintage ones in my archives. It could be a bit different, depending on the power supply, speed and other details. Here the cell draws about 350µ @ 5V.

The power-on-reset cell (3 parts) is shared with all the other FF. The values will change and be tuned later.

The pass transistor is still the same here, but the trigger values vary considerably :

- The 1M resistor means that the transistor only needs one potential to polarise the component and select which way the base current will go. The whole base current is used to "upset" the base of the FlipFlop. A higher value than 8K2 on the base of the pass transistor would be possible if more current is available from the source. Though it woudn't work well for the other case :

- The 8K2 pull-down resistor is on the limit, because enough current must flow away from the FF base. The pass current then flows away, in the weakly amplifying direction

This 3-transistors, 6-resistors latch should be cascadable in theory, it uses only one kind of transistor and is minimalistic. But a fully clocked DFF requires 2 latches so it is not yet a solution...

The solution to the "latch duplication problem" would be in the sequencing of the latch strobes. I had considered a method, some years ago, and I'll have to refresh it... There would be as many phases to the clock as there are latches, so only one is transparent at a time. The temporary overlap is not a problem for the display part, but the sequencer must not use more than 2 transistors, 1 would be best.

And I must make sure the latch is cascadable.

Which is a tricky question because this circuit seems to let the pass transistor transmit a positive front transient... and I had to remove the emitter common resistors to have enough current to reset the slave.

This is solved with this circuit with a better protection against back-pulses on the supply rail.

Yann Guidon / YGDES

Yann Guidon / YGDES

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.

If you're trying to use as few NPNs as possible how about reversing the polarity of the whole circuit so that PNPs are in the majority?

Are you sure? yes | no

well this is indeed the usual method, though I'm more used to NPN.

The circuit can be reversed to use PNP.

Are you sure? yes | no