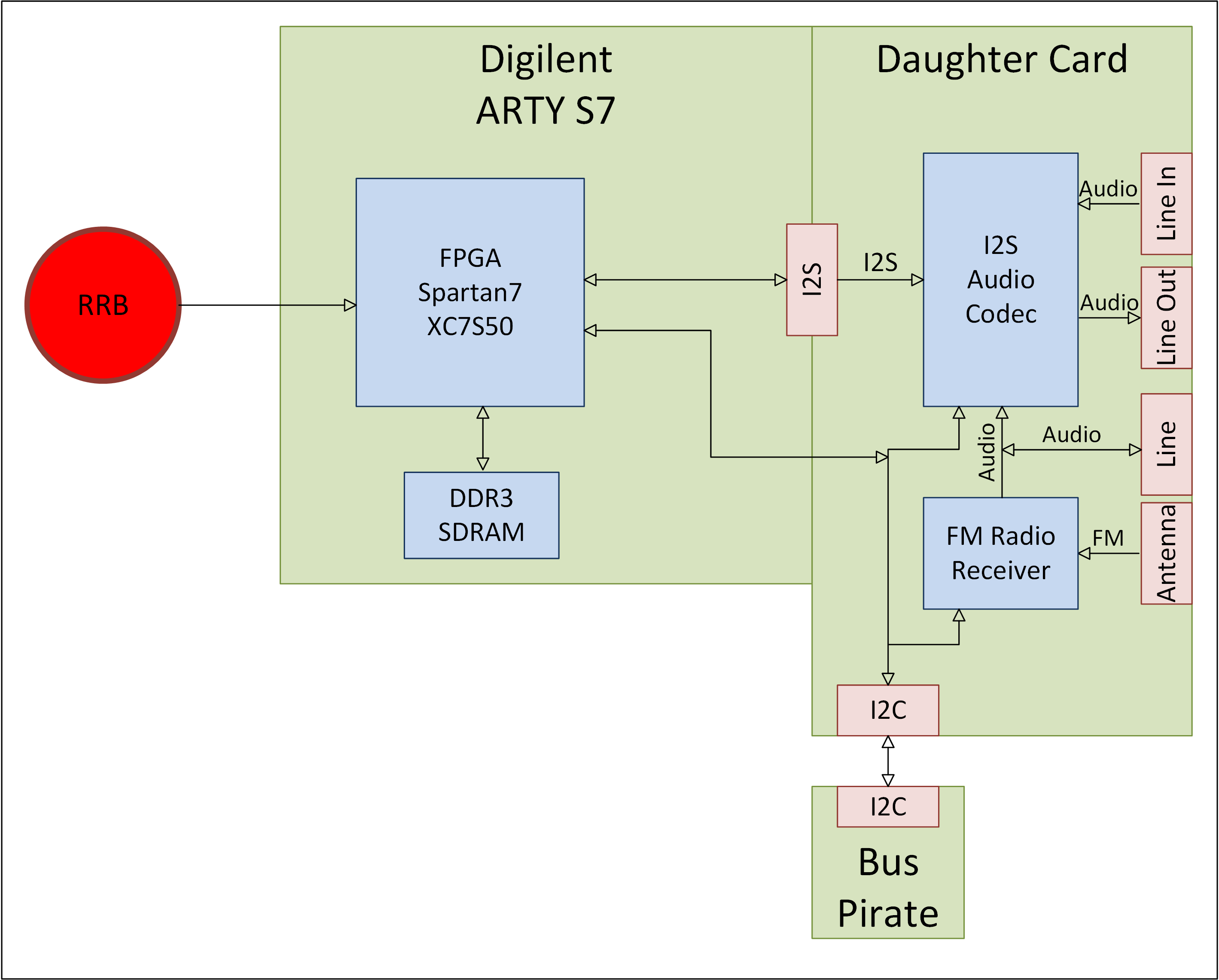

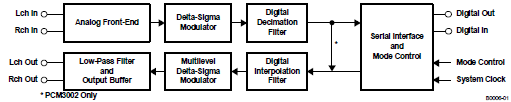

The idea is to have a FM receiver chip with I2S interface to get the audio data into the digital domain as quickly as possible. The FPGA implements a ring buffer inside the SDRAM memory with an I2S to line out back end. A small controller, probably Arduino is going to to control the radio station and a small display with a all necessary information as FM frequency, rewind metric and memory telemetry. Finally the main controller, a BIG red button to rewind your radio and give superior listen experience.

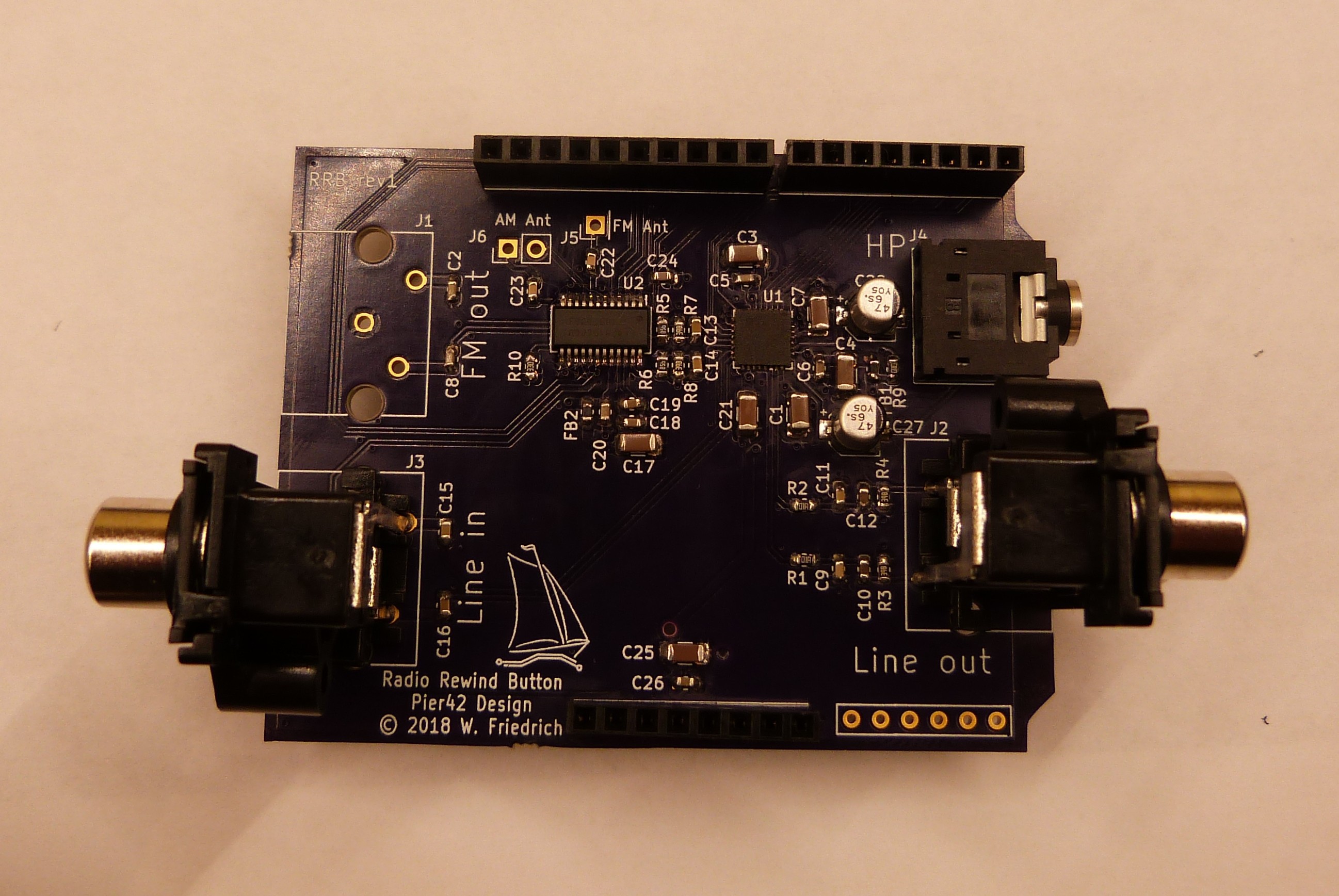

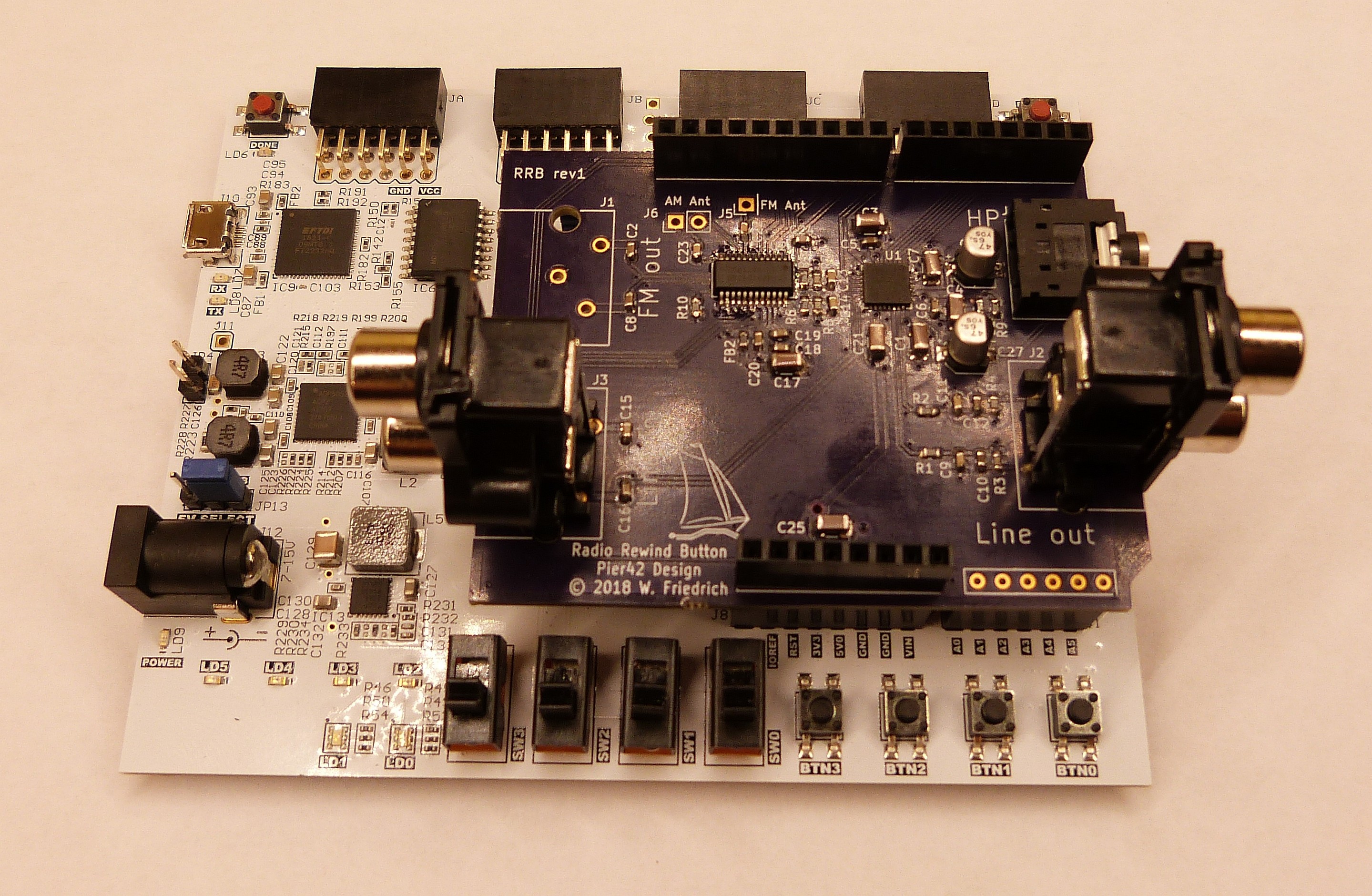

The concept changed somewhat, I decided to run the analog audio rom the FM reciever chip to the audio processor and use its I2S interface as the only digital link. Makes for a much cleaner data flow.

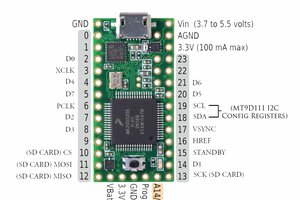

The base platform is going to be a Digilent ARTY S7 board which provides 256MB of SDRAM already, so I don't have to do the risky SDRAM over PMOD interface. The daughter card with all audio circuit will be in a Arduino Shield formfactor for potentially later re-use.

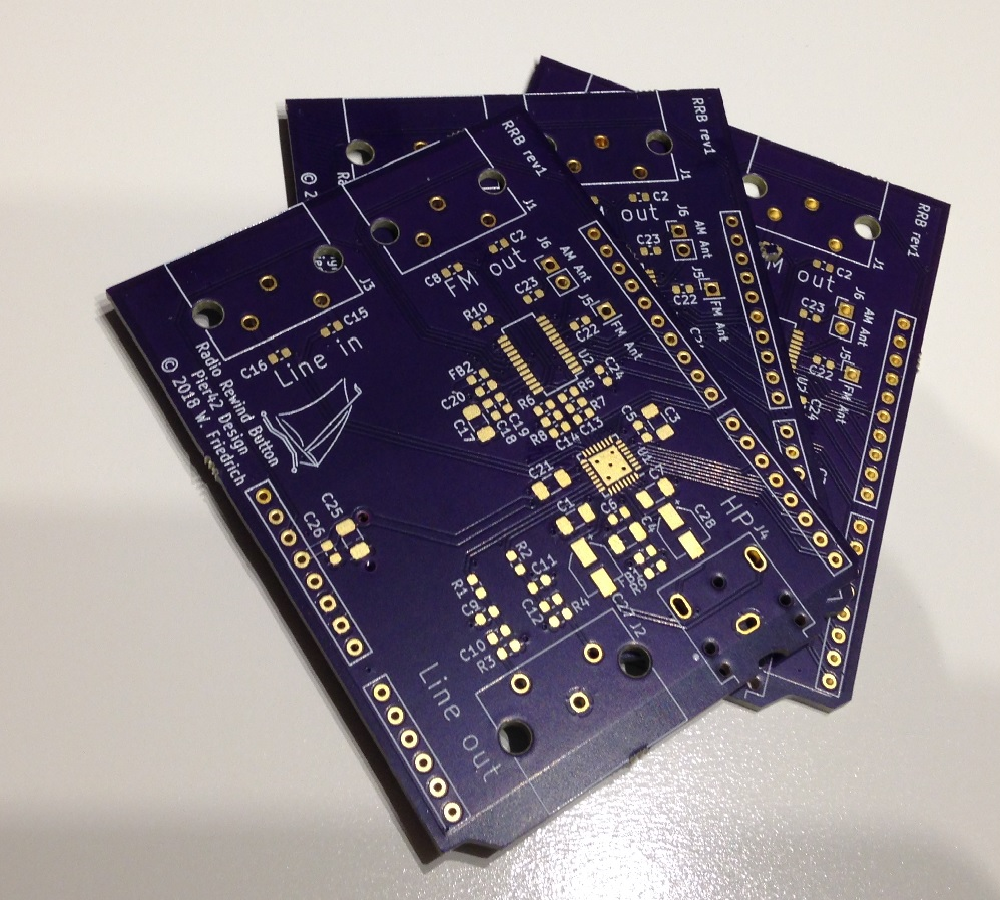

The design and layout is finished, schematic (with fixes) and assembly drawing are in the files section.

And to fill in some gaps: With 256 MB of memory all used in one big ring buffer and assuming 44.1 kSamples/sec, my math adds up to just under 25 minutes of rewind time, which should be plenty.

MagicWolfi

MagicWolfi

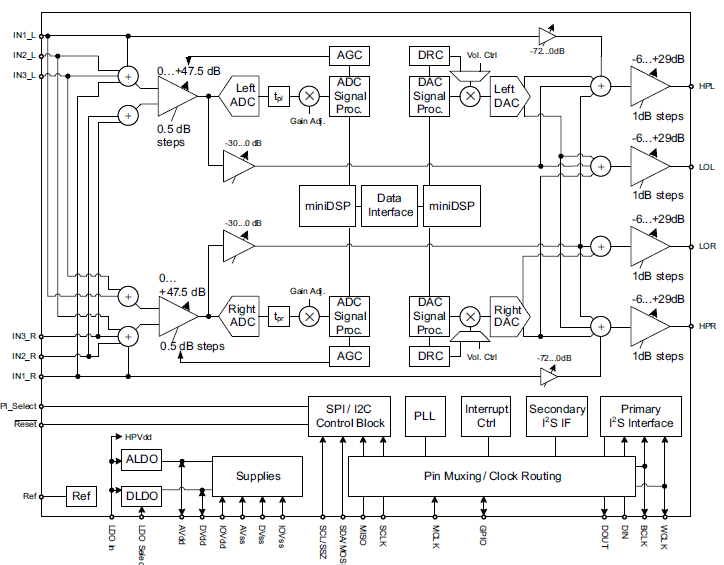

Another option would be the TI PCM3070 audio codec chip, which has 3 audio input pairs. This would change the architecture quite a bit, running the FM radio audio stream analog into the PCM3070 and only have a single I2S interface for all digital audio data. Also the control interface is I2C which would help in my quest to save signal pins between the ElbertV2 and my RRB daughter card.

Another option would be the TI PCM3070 audio codec chip, which has 3 audio input pairs. This would change the architecture quite a bit, running the FM radio audio stream analog into the PCM3070 and only have a single I2S interface for all digital audio data. Also the control interface is I2C which would help in my quest to save signal pins between the ElbertV2 and my RRB daughter card.  Decisions, decisions.

Decisions, decisions.

Jason Nelson

Jason Nelson

Jac Goudsmit

Jac Goudsmit

Anthony

Anthony

Michael Kafarowski

Michael Kafarowski

You could also use RDS to implement commercial skipping.