DIY ALU III

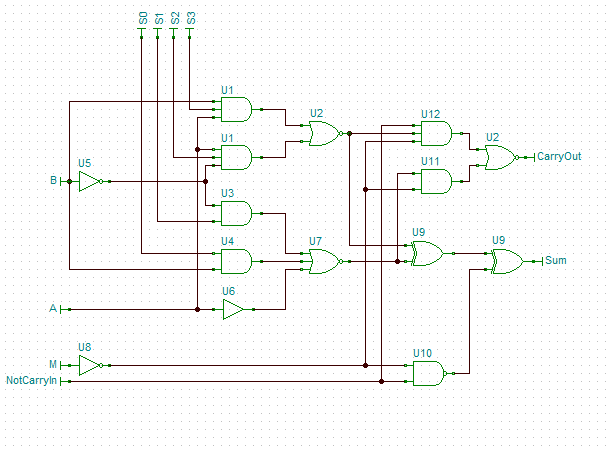

Well I can't leave it alone! I decided to have a closer look at the 74181, so I extract a bit-slice from the schematic (the comparator logic is lost):

Not hard, even found a schematic error - I wonder if anyone else has found it as well?

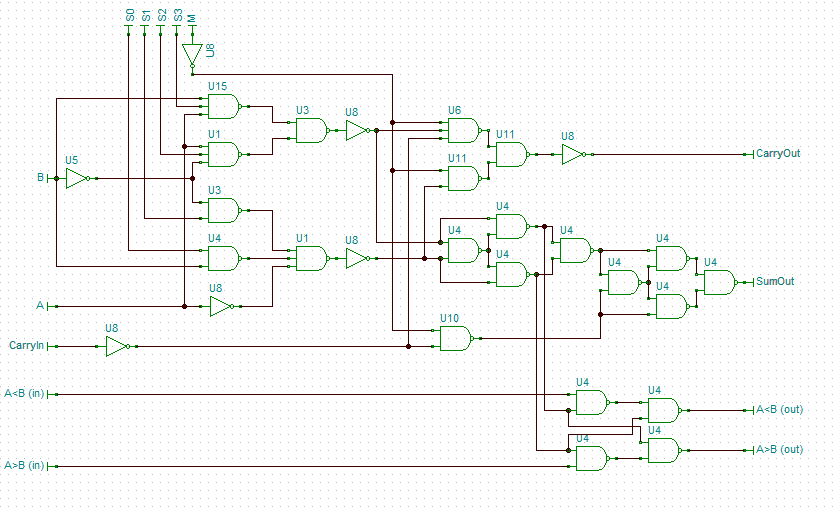

I then converted the gates to NANDs, and added in my preferred comparator logic. Here is the result:

So now I am down to 1 inverter for the Carry In (don't like the Not Carry logic of the 74181) and 27 gates per bit-slice. The main difference with my version is it will be slower to propagate.

So the total gates for the 74181 was 100 and my version is 109 (but includes a better comparator logic). Add six gates for the Selection Decoder (refer to the 4 Bit CPU ALU issues) and I get 115 gates.

This design would equate to seven packages per bit slice (much better!).

I case you have forgotten why I an not using XOR gates or MSI logic, this work is in preparation for a possible transistor CPU, so it uses SSI NAND gates.

I will have to look at the selection logic to see if I can fix it (another post?) or merge the Selection Decoder.

AlanX

agp.cooper

agp.cooper

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.