Taming the 74LS181 ALU

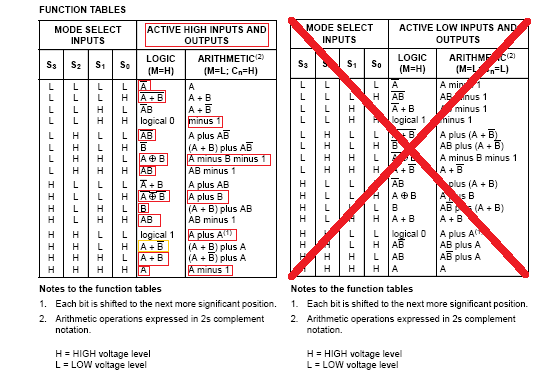

First the useful instructions:

Okay you may disagree with my list but here are the reasons:

- I am only interested in active high logic.

- Of the arithmetic functions only every third one is useful.

- I can do without MINUS.

- The logic functions are a bit more subjective.

- I have hi-lighted in orange one that is useful for my ALU because of the way it works.

So I got 16 codes, sweet now get back to work!

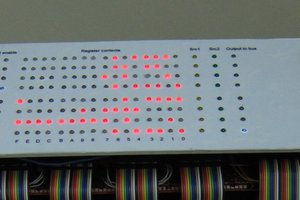

The ALU design for the 4 Bit CPU

For a 4 Bit CPU there are only 16 possible Op-Codes and I need to reduce the ALU set down to eight. You may not have picked up what I want! I really mean M, S3, S2, S1, S1 need to be remapped to 3 bits. Okay, but how do you do that, the codes are a mess!

First the eight codes I have selected:

- PLUS (A plus B)

- XNOR

- LAST (B)

- AND

- DEC (A-1)

- OR/NOT (A+!B)

- OR

- MOVE (A)

Note that A is now called MOVE and B is called LAST and will be discussed later.

You will note that I have chosen instructions for S3 high so my task is reduced to reducing 4 bits to 3 bits.

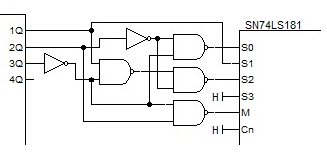

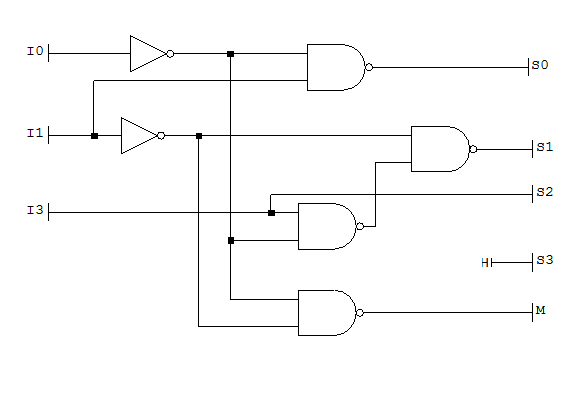

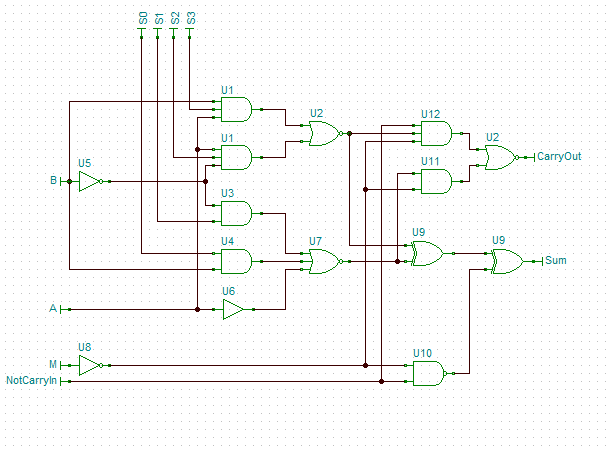

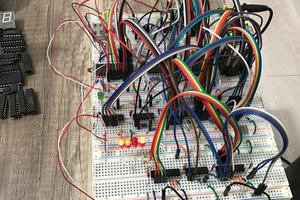

You will also note that other than ADD and DEC, the select codes (i.e. M, S0-S4) are unchanged. So I only need to remap ADD from 01001 to 11000 and DEC from 01111 to 11100. Note M and S3 are now always high. Here is the schematic for the remapping:

If your interested I did not solve the remapping by hand. I used LogicFriday:

LogicFriday is a front end for Espresso by Richard Rudell (rudell@ic.Berkeley.EDU).

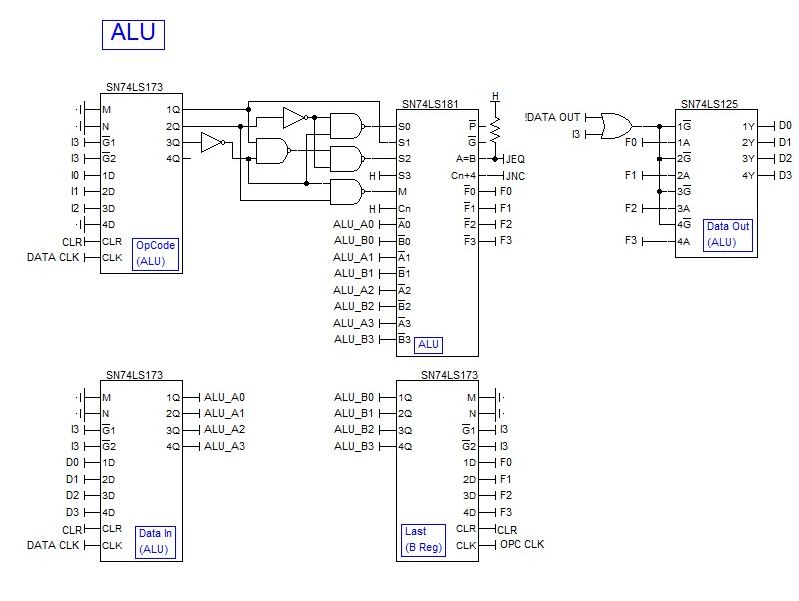

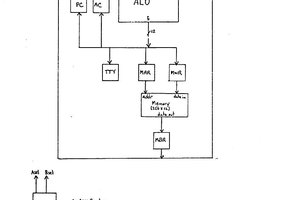

ALU organisation for the 4 Bit CPU

I adopted a single register programming model for my ALU.

Basically:

- Fetch data from the memory

- Process the data

- Deposit the result back to memory

For this to work then the previous results need to be reused as the "B" operand.

An ADD sequence would be:

- MOVE [Memory B] to [Memory B] (Sets the B operand)

- ADD [Memory A] to [Memory C] (A is ADDed to B and stored in C)

Okay what is with OR/NOT, LAST (B) and MOVE (A)?

- OR/NOT (A OR NOT B) code was the closest available code remaining for use with the decoding decisions adopted, it us used to NOT the previous results.

- The B code is the same as the LAST result.

- The A code is the same as a MOVE.

Consider a NAND sequence:

- MOVE [Memory B] to [Memory B] (Sets the B operand)

- AND [Memory A] to [Memory C] (A is ANDed to B and stored in C)

- OR/NOT [Value 0] to [Memory D] (Not B and OR with 0)

Here the result of A AND B is NOTed and then ORed with zero, result is a A NAND B.

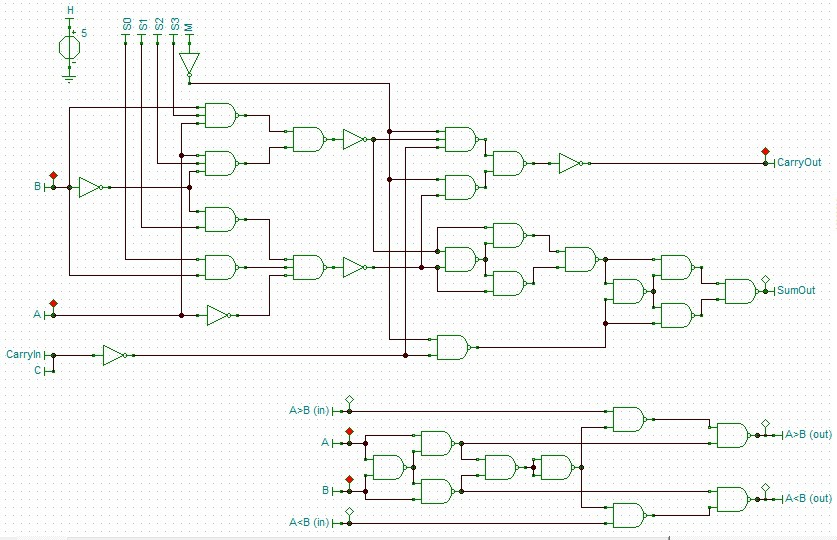

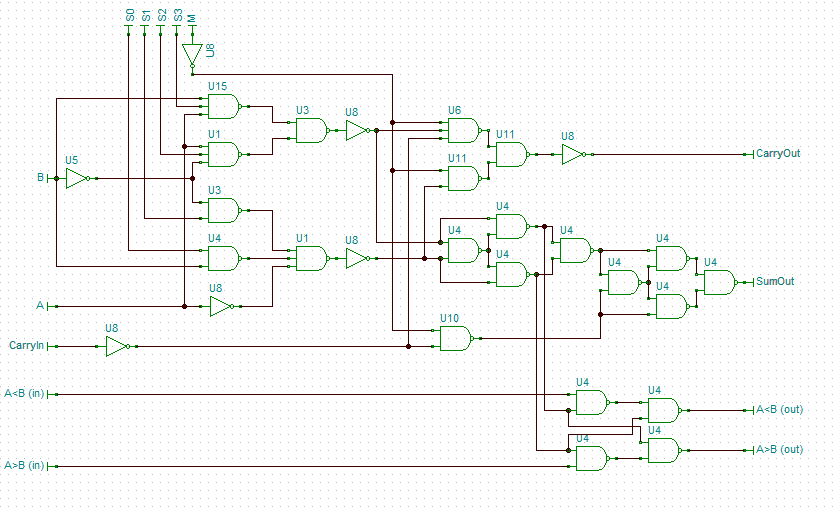

Here is the ALU schematic for the 4 Bit CPU:

Are you still with me? AlanX

agp.cooper

agp.cooper

Dr PEKER

Dr PEKER

Pavel

Pavel

AranweLTT

AranweLTT

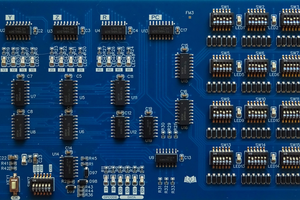

Hi Alan - I arrive a bit late to the party, but I have an ALU that might interest you.

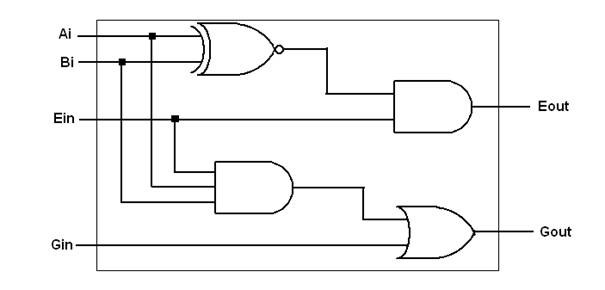

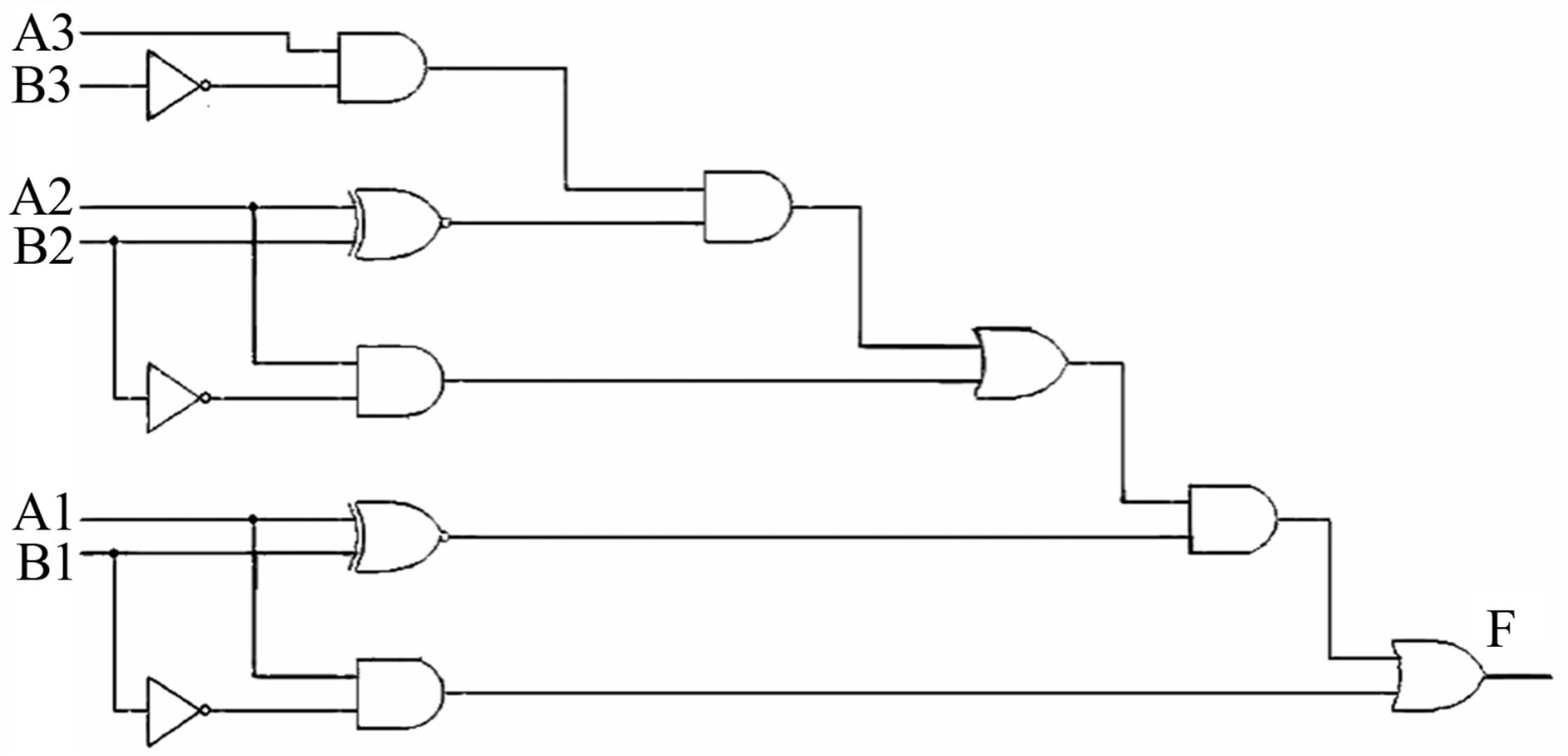

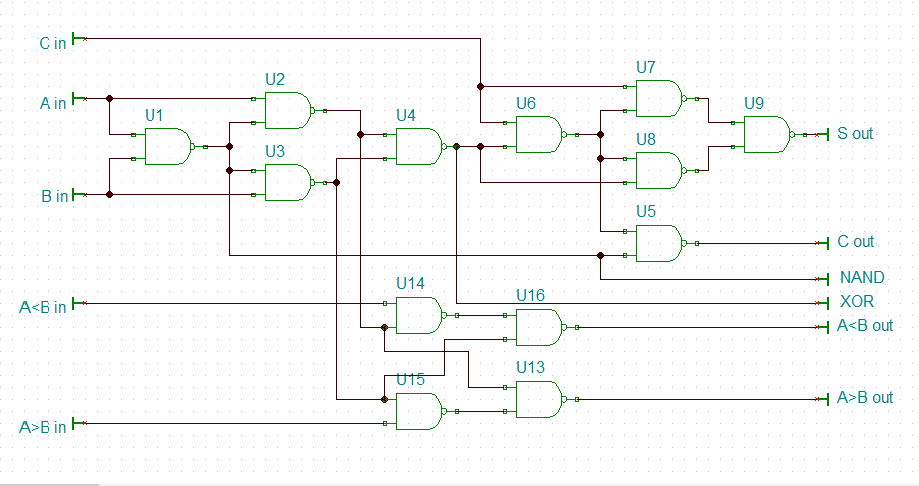

If we consider a single bit-slice, it consists of a full adder, with an XOR gate on the B input , so we can selectively invert B when doing subtraction.

As we know, the full adder produces a sum term (XOR) and a Carry term (AND). When we want a logic function, we can combine the AND and OR outputs in a 2-input multiplexer, (controlled by I4 and I5) which will give us ZERO, XOR, AND, and OR.

If you want the inverted logic functions follow the mux output with another XOR, to invert it.

When used for logic functions, you will have to suppress the carry from passing onto the next slice.

Diagram below,,

Regards

Ken

![]()