-

SD access now works

09/26/2016 at 18:00 • 0 commentsI added SD card support VHDL code, but did not have the time until now to debug it. Now I have a TMS9900 assembler program which successfully displays the root directory of a FAT16 partition.

-

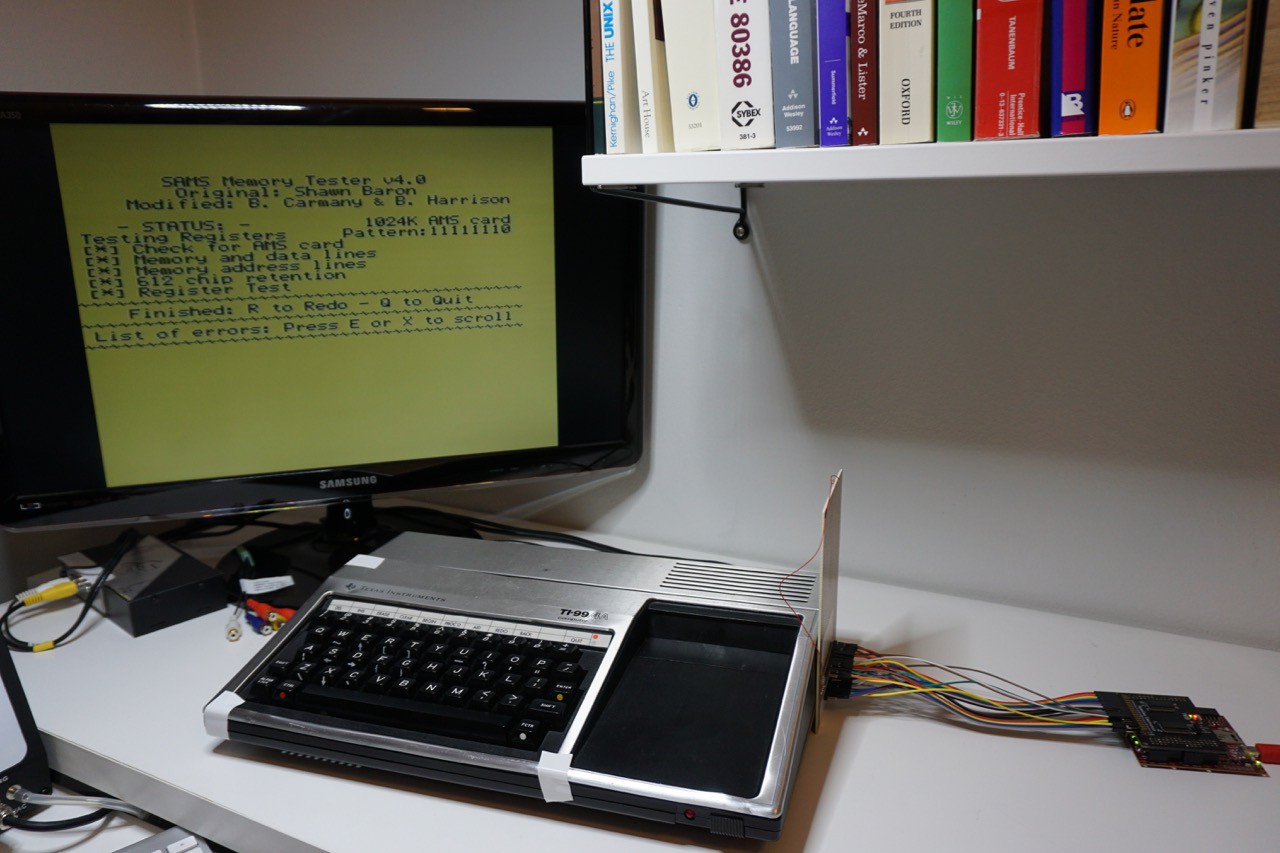

Super AMS compatibility done

09/21/2016 at 20:14 • 0 commentsI modified the memory paging side of the design somewhat, so that the paging is controlled using the same bits as with "Super AMS" memory paging unit. This required the addition of the support of the TMS9900 "CRU" memory space - but in a limited manner. Now the the FPGA based memory expansion passes the SAMS memory tester. This is very nice indeed - also since I don't have to write memory test code myself :)

![]()

-

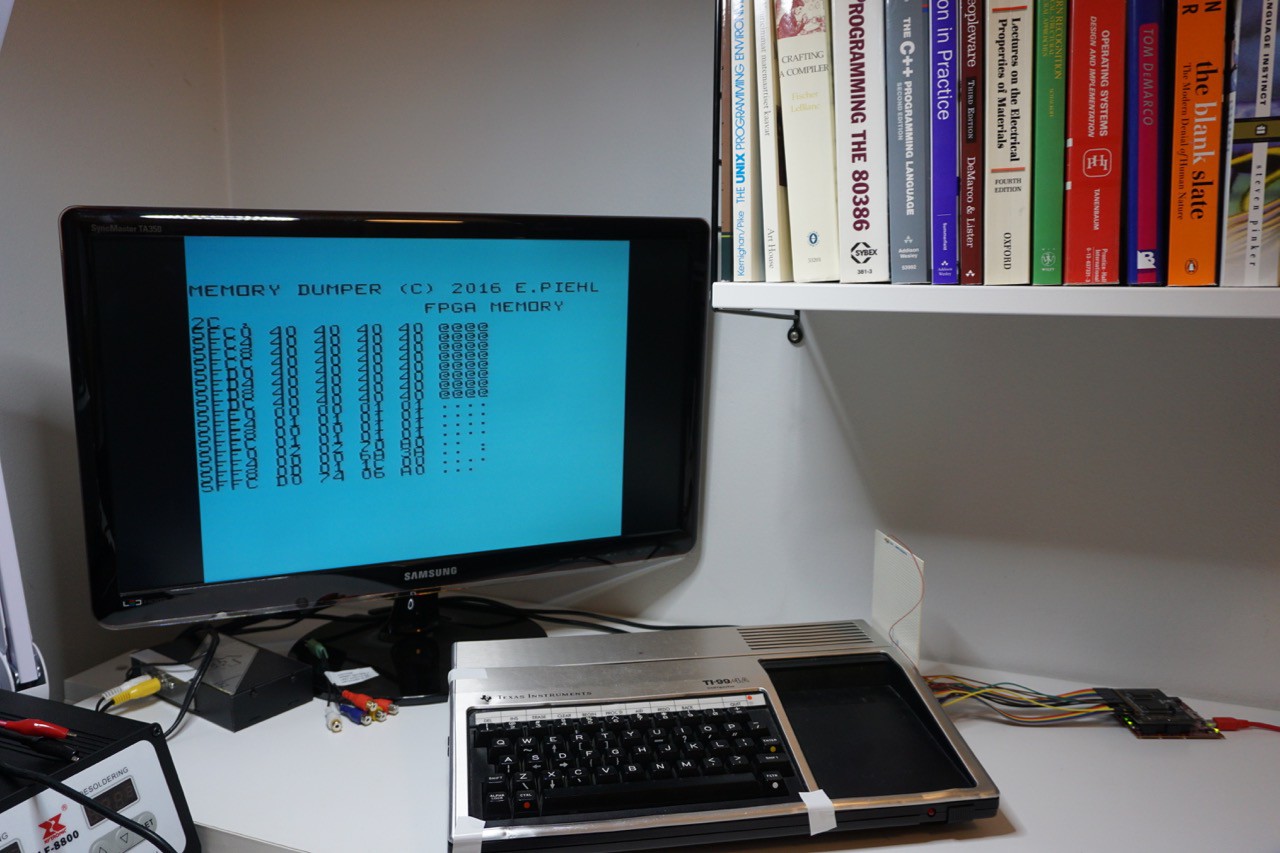

SPI interface and software development

09/20/2016 at 17:54 • 0 commentsReal life kept me busy, but I finally had a moment and added SPI interface to the FGPA design. It allows the use of SD card, but needs driver software, so I also have spent a little time building some software. At this point the software is a simple memory dumper, controlled by button presses. Very useful for hardware testing, and now that there is simple user interface capability it will be hopefully easy to get the SD card driver side done and tested.

![]()

-

PC connectivity using DMA style approach

09/04/2016 at 20:21 • 0 commentsNow I finally have an easy to way to push software to the TI. I built support for serial communication (over USB) at 230kbps allowing me read and write the memory expansion concurrently to the TI - without the TI noticing. This is hugely useful also for software development and debugging.

-

GROM functionality now done by the FPGA

08/26/2016 at 20:12 • 0 commentsAfter some debugging sessions, I got the GROM address counter bugs fixed and now the FPGA alone also integrates the extended basic cartridge.

-

ROM and ROM page switching moved over to FPGA.

08/24/2016 at 06:35 • 0 commentsI wish there was more time to work on this, but at least I could take a simple step of moving the extended Basic ROM in the cartridge port into the FPGA, along with the ROM page selection logic. Thus now the only thing requiring the cartridge port to be occupied at all is the GROM section, which needs to move over to the FPGA next.

Obviously having cartridge functionality in the expansion bus is probably not exactly proper behavior, but I don't have the extended basic cartridge. I suppose the FPGA could have a sense mode, to see if there is a cartridge driving the databus, and if not, then take over and become the cartridge.

-

SDRAM controller working...

08/19/2016 at 08:05 • 0 commentsYesterday got the SDRAM controller working. More testing and validation required, but it is nice to have 64 megs of memory! Memory paging unit is still not working completely.

-

SDRAM controller implementation started

08/16/2016 at 06:59 • 0 commentsOne of the next steps in this project is to integrate all the functions on the other boards into the FPGA. I also want to start using the external LPDDR RAM memory. The use of that is not trivial, but this FPGA includes a memory controller. The problem with it is that this component is highly configurable and complex. But I did manage last evening to go through the first step, which is to instantiate the controller and have it drive the clocks in the logic. That means that the PLL in the memory controller is now generating a 100MHz clock that drives the logic. Next need to build a state machine to control memory writes and reads, and hope for the best...

TI-99/4A memory extension with Pipistrello FPGA

64 megabytes RAM expansion for the TI-99/4A using the Pipistrello FPGA board and a buffer board.

Erik Piehl

Erik Piehl