As I start to "get" ECL, I discover its topological language and various methods to do the same thing.

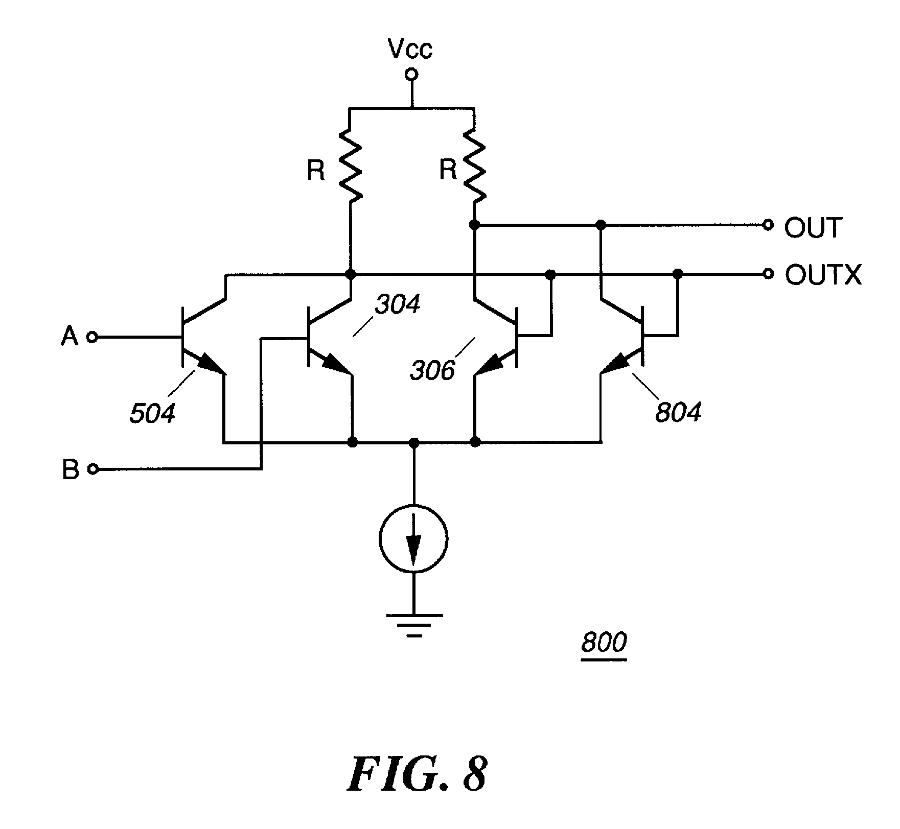

For example a OR gate, without the common bias node of MECL10K, found in an old patent http://www.google.ch/patents/US5831454 :

So that's one thing to do : compare this topology with the common-zener one. As germanium is pretty sensitive, I wonder which circuit will work best.

The latches are another concern, apparently there are a few ways to make them, and 6 transistors per latch seems to be the minimum (12 per DFF, similar to other technologies).

Update 20200524:

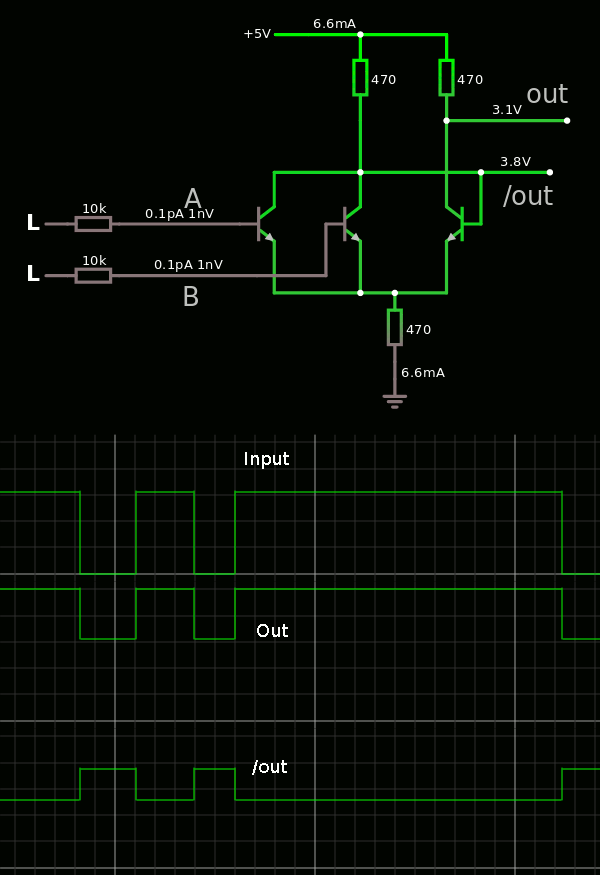

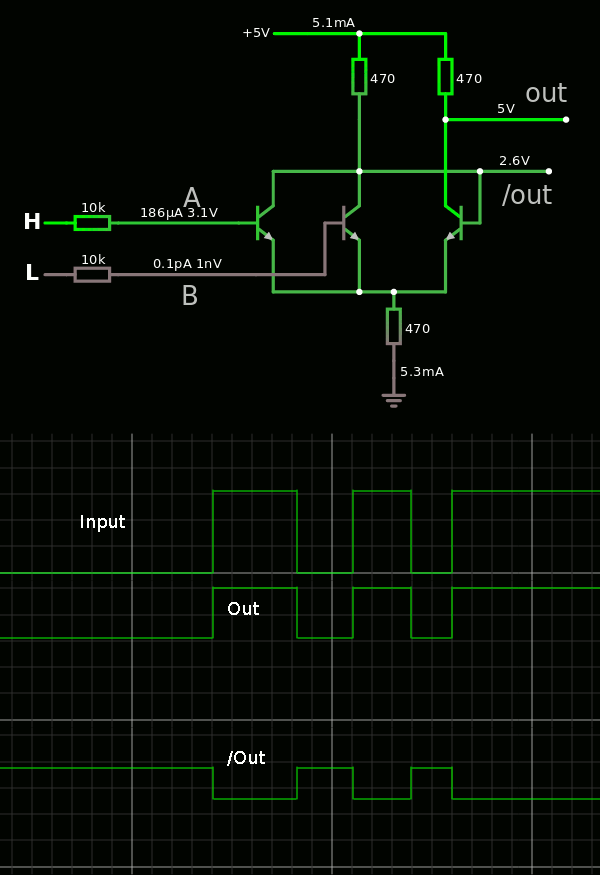

Thank you Falstad :-)

The 2 transistors on the right are just to balance the current because of the gain... So I try with only one.

The sims show that the output levels are not comparable :

The inverting output has a lower range than the non-inverting output... It is indeed clamped by the base of the right-hand transistor.

Finding the right values for the resistors is another challenge, it's not mentioned in the patent (?)

With all resistors at 470, I find :

Vin-h : 3.1V

Vout : 5V - 3.1V

V/out : 3.8 - 2.6V

Anyway this is an unbalanced system because in "normal" ECL the branches are mostly independent.

The non-inverting output needs to be level-shifted...

And it is a system that has about 1.2V of hysteresis !

Yann Guidon / YGDES

Yann Guidon / YGDES

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.

This stuff makes me wonder... So much of our processing-power these days is *constantly* changing-state... and, for mosfets, the most current-draw is *while* changing-state... Almost seems like there'd be a balance somewhere where using something like ECL would actually take less-power than the equivalent CMOS.

Are you sure? yes | no

They tried with the Pentium4 :-D

You haven't heard about the "dark silicon" problems though.

Are you sure? yes | no

Interesting, learned a lot. But can't find this about the P4... search-fu fail, I guess :/

Are you sure? yes | no

Dark silicon : it's hard today to feed all the transistors with power when all the parts of the chip are active. So it's not a good idea to let them work in constant-current-like mode. It's important that not everybody switches at the same time, or the resistance of the supply wires drops too much voltage.

About P4 : I have no confirmation about the internal technology but they used a sort of ECL-like topology to reach the screaming speeds. Of course, screaming power consumption. Not a desired trend, particularly when the chips get larger, power supply wires are longer and drop more (hence the dark silicon remark).

Fortunately I'm not affected by this now ;-)

Are you sure? yes | no