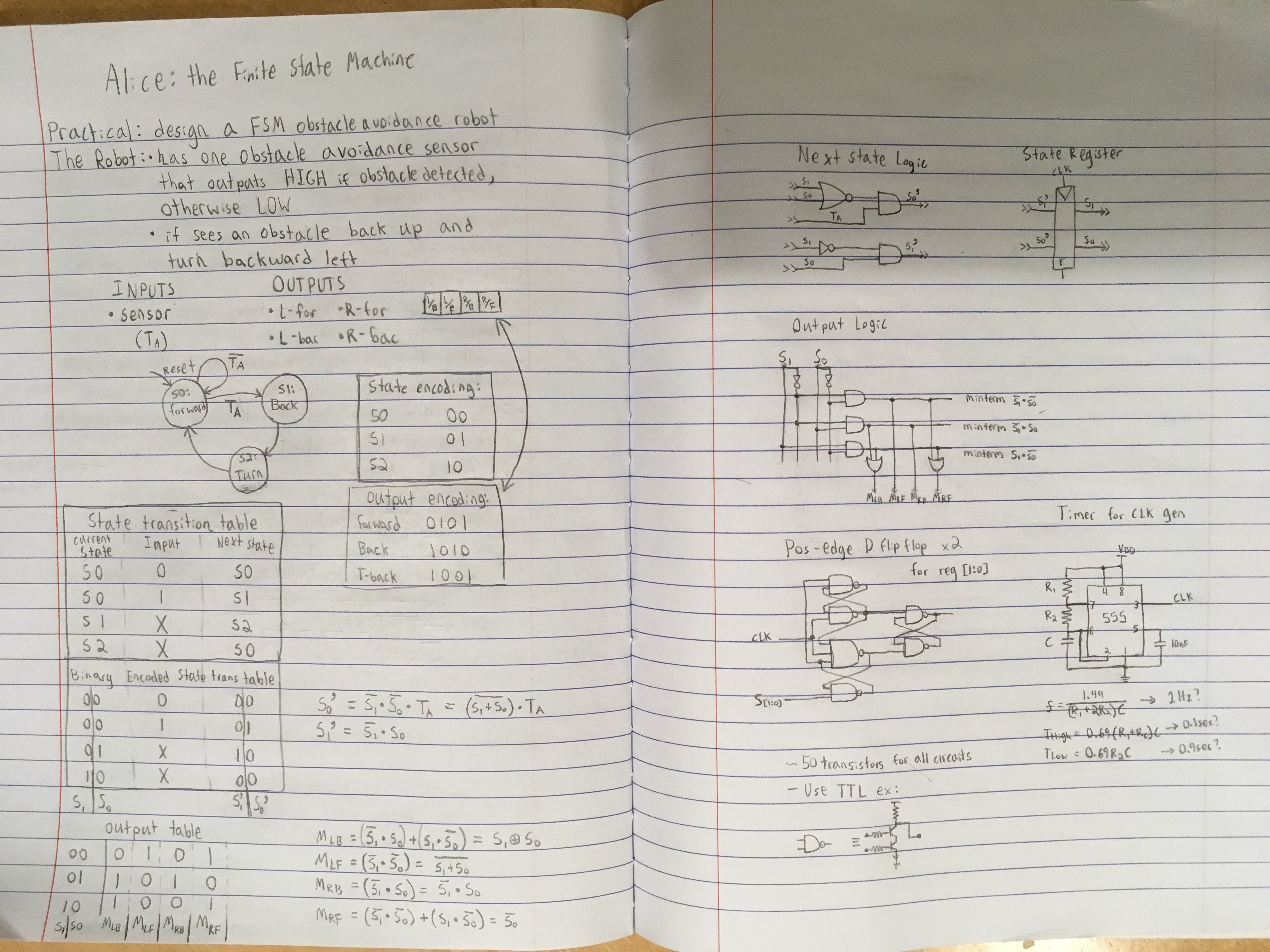

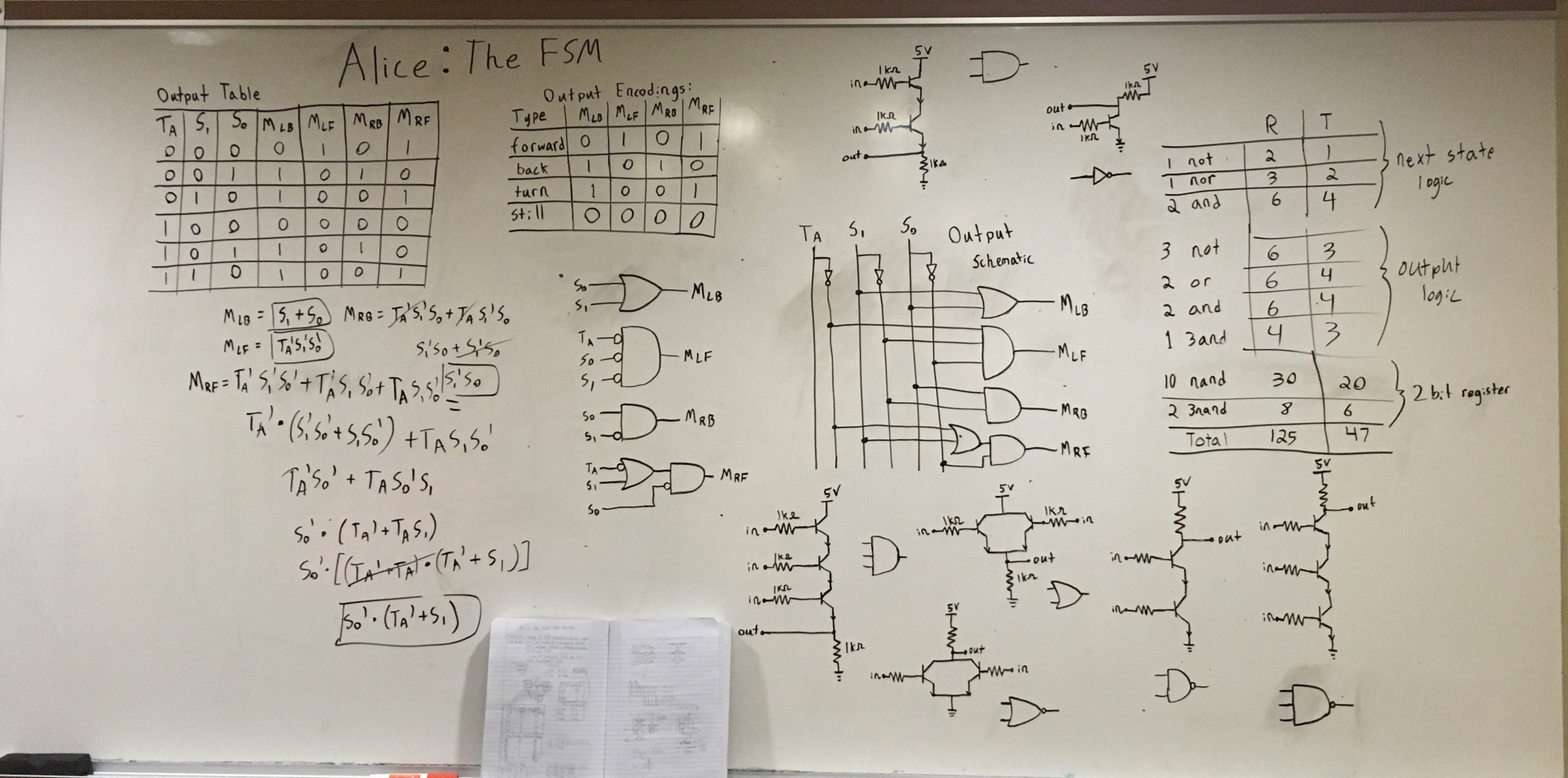

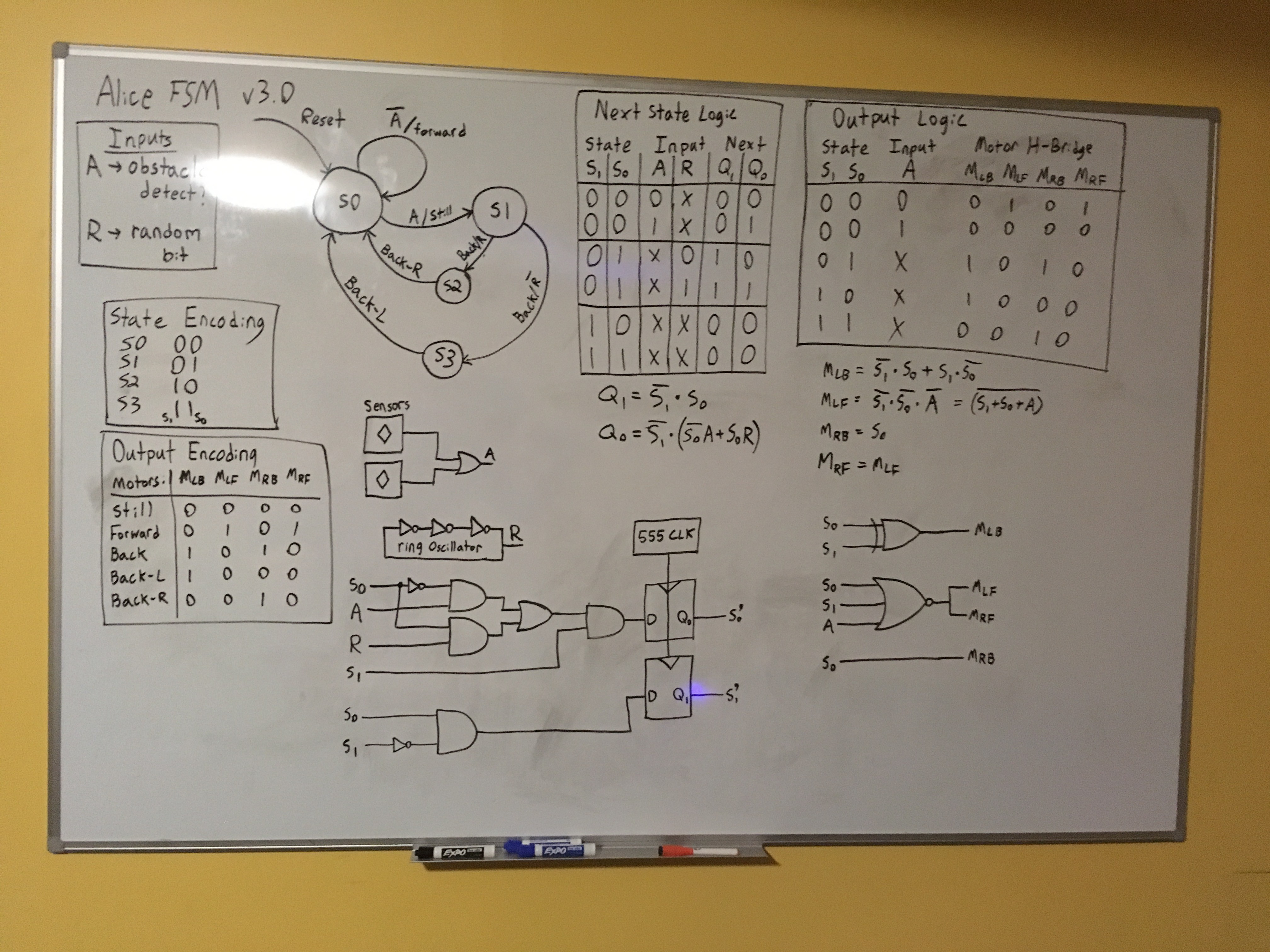

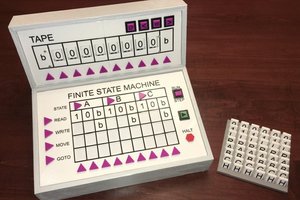

Alice went through several iterations of design through the past few months. I redrew the FSM and the accompanying logic and transitions tables several times. I eventually settled on a Mealy FSM design instead of my original Moore FSM design as this would allow Alice to stop as soon as it saw an obstacle instead of waiting until the next state transition:

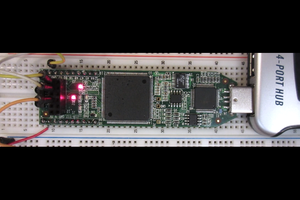

Before implementing the FSM in transistors, I implemented it in Verilog and simulated it on a DE0-nano FPGA to make sure all the logic was sound:

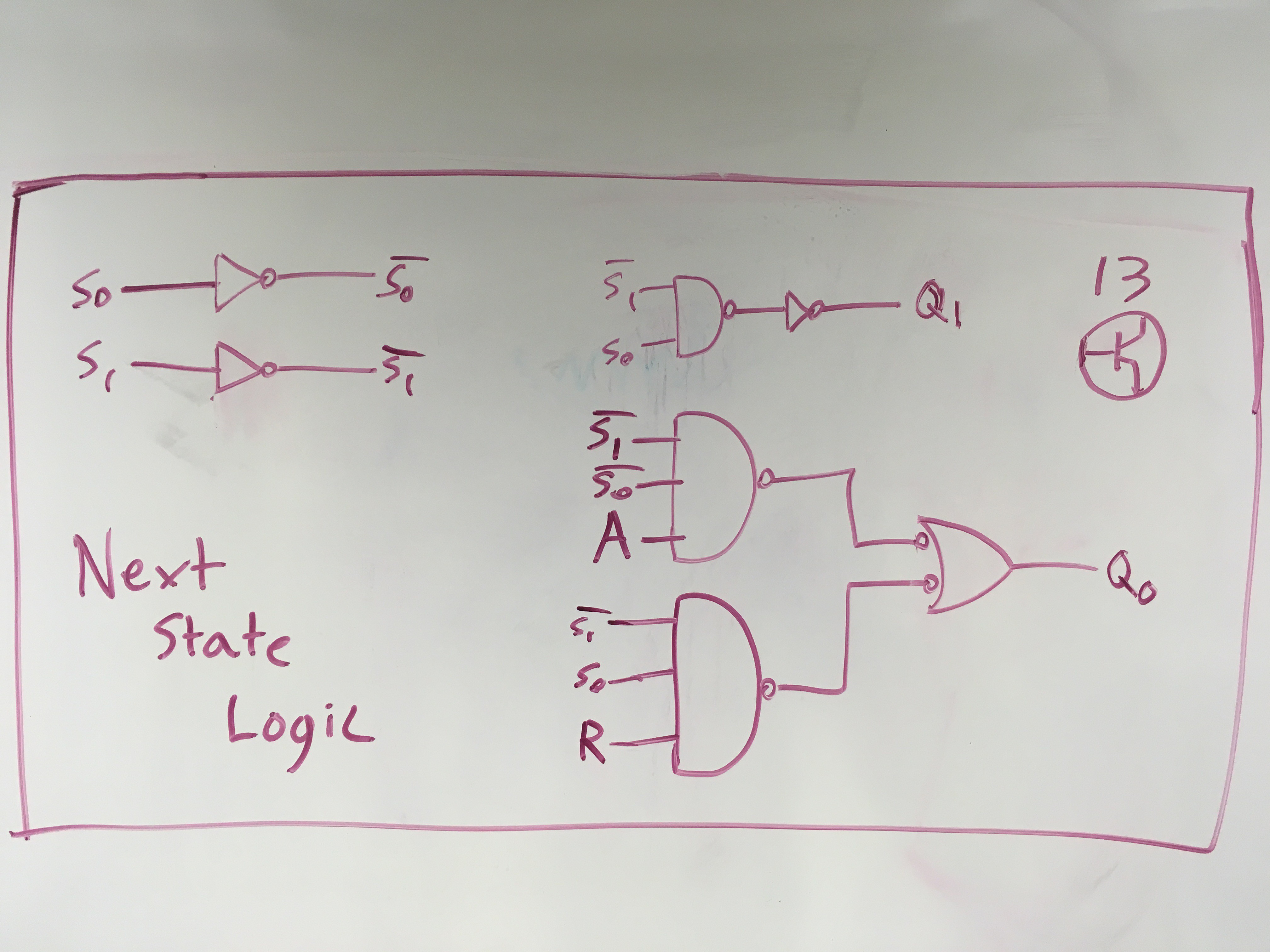

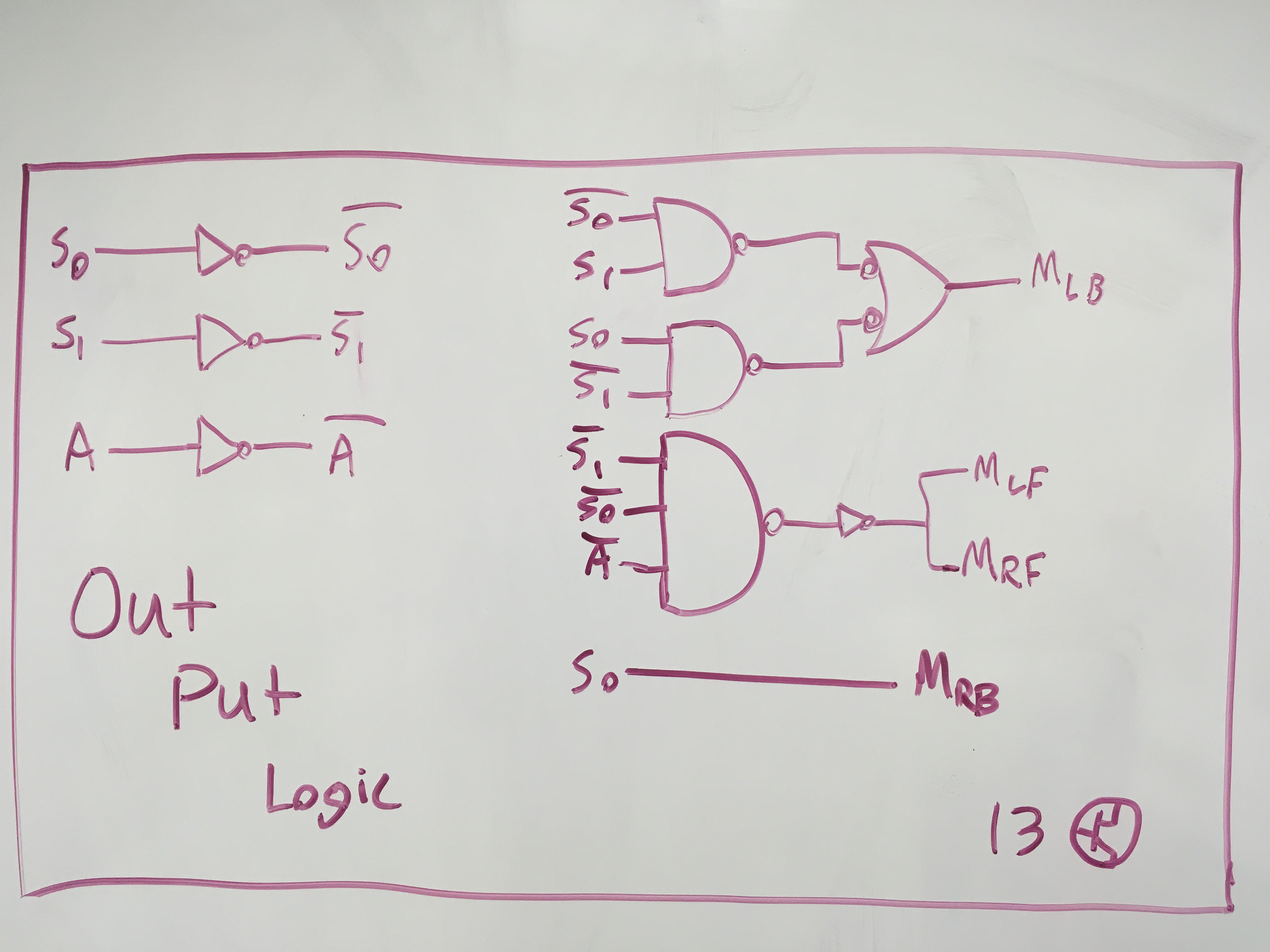

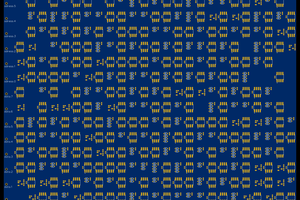

Here are the designs for the and logic blocks I decided to use (originally I attempted to implement the next state logic with regular AND and OR gates and realized that with only 1KOhm resistors these gates did not behave correctly, so I decided to stick with NAND and NOT):

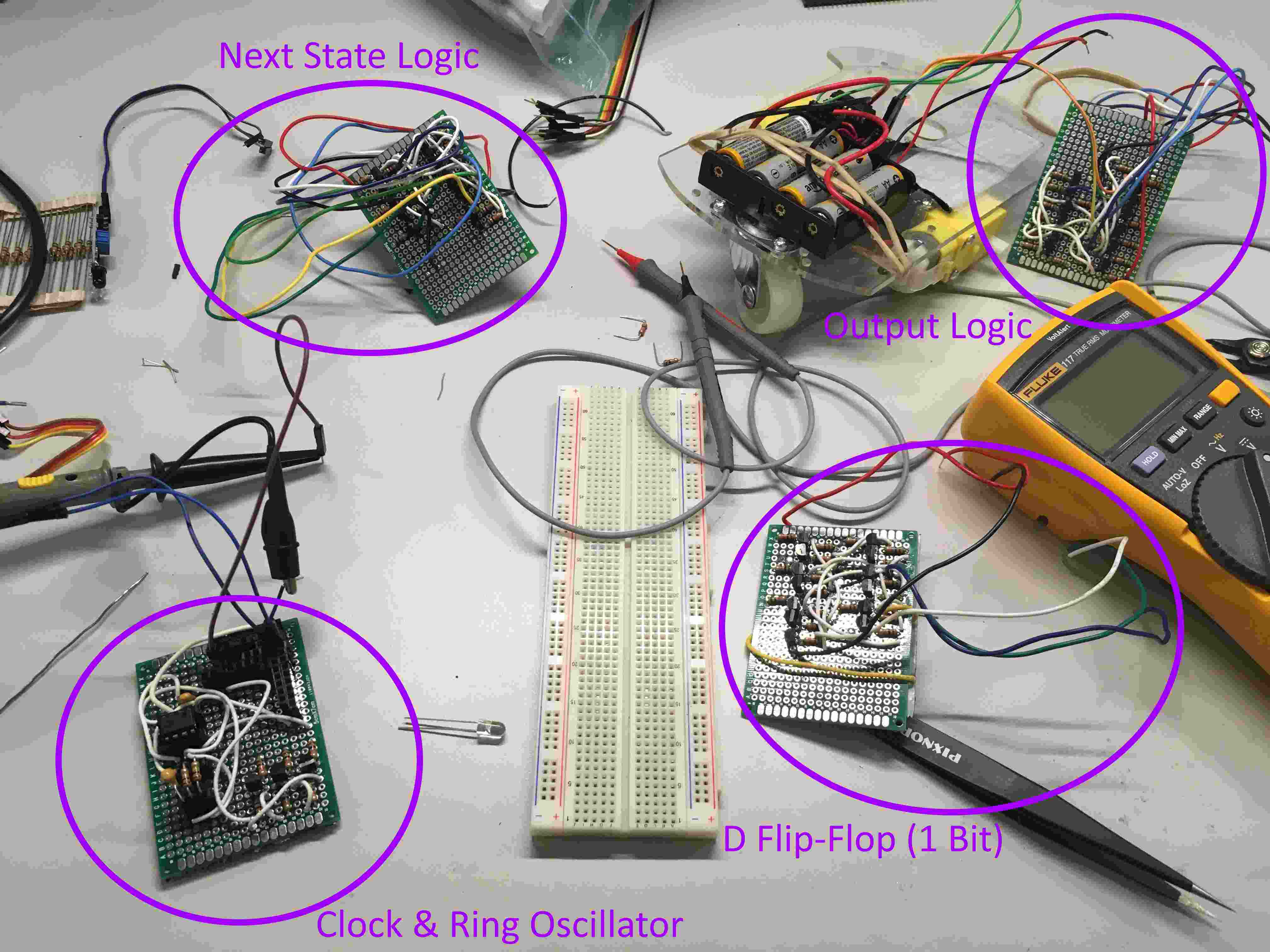

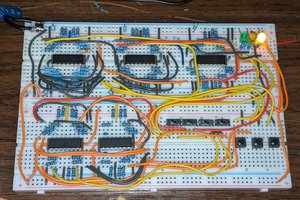

Here are some of the boards after assembly:

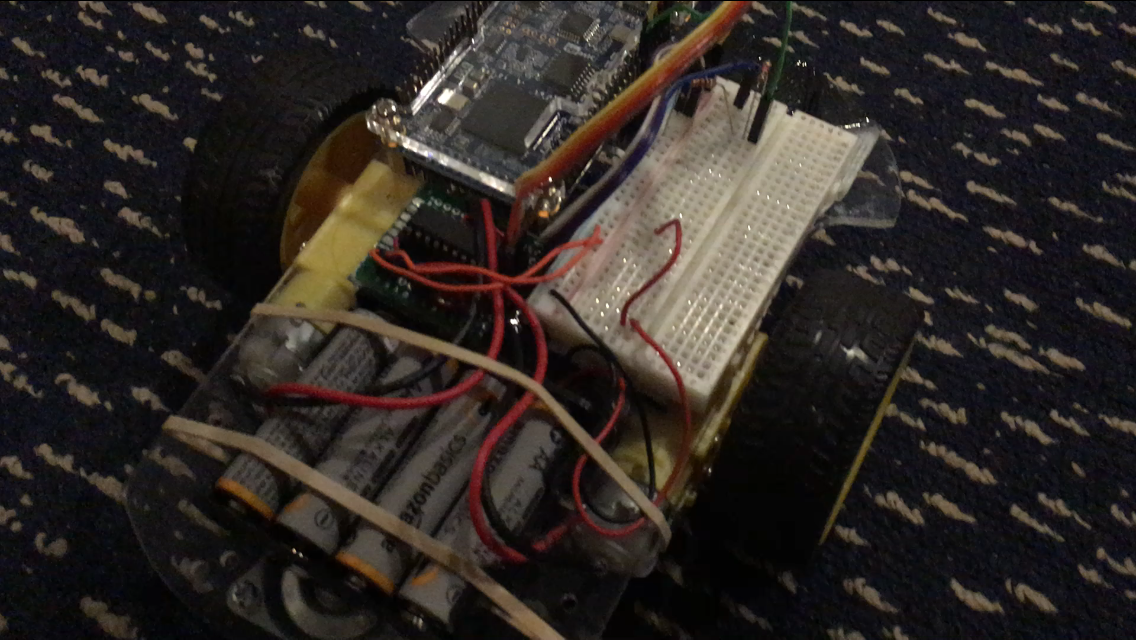

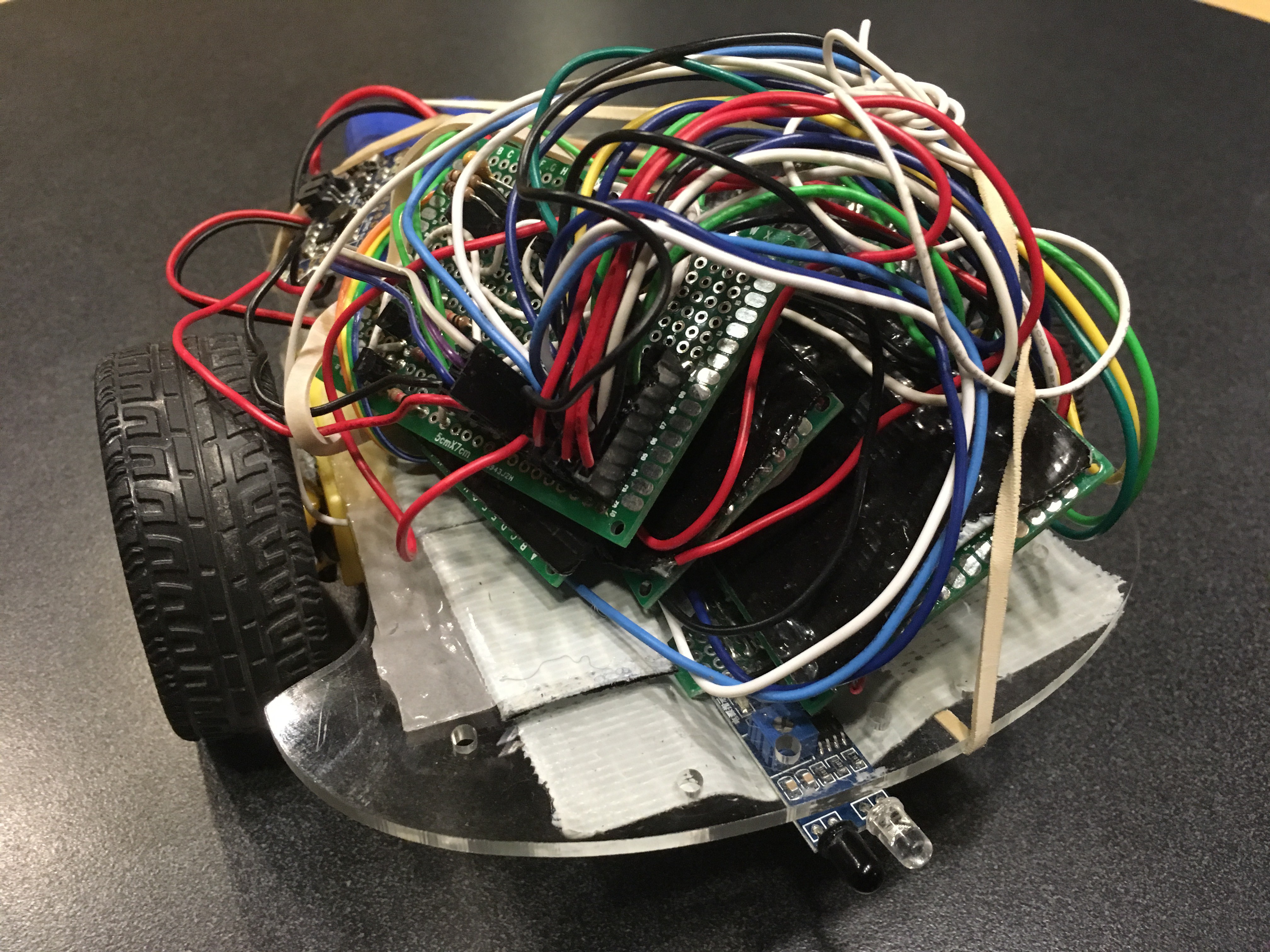

And... Here's the finished product!

Joseph Primmer

Joseph Primmer

Michael Gardi

Michael Gardi

Al Williams

Al Williams

Tim

Tim

Dave Collins

Dave Collins

Very nice use of RTL :-)