After working on updating the verilog module used in my camera to support the HyperRAM using DDR modules and the PLL of the ECP5 FPGA I'm using.

The change increased the performance by 4x. This enables us to capture the datarate from the Boson 640 cores.

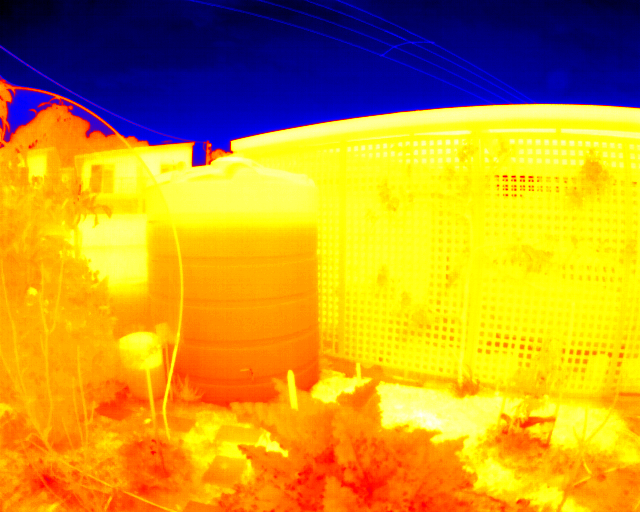

Here is a photo of the water tank ~80% full.

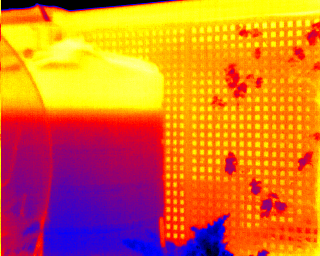

For reference here is the same tank using the Boson 320 core.

There are still many performance improvements I have on a list to work on.

But the major functionality of the device is working. We can capture Images at about 3 FPS.

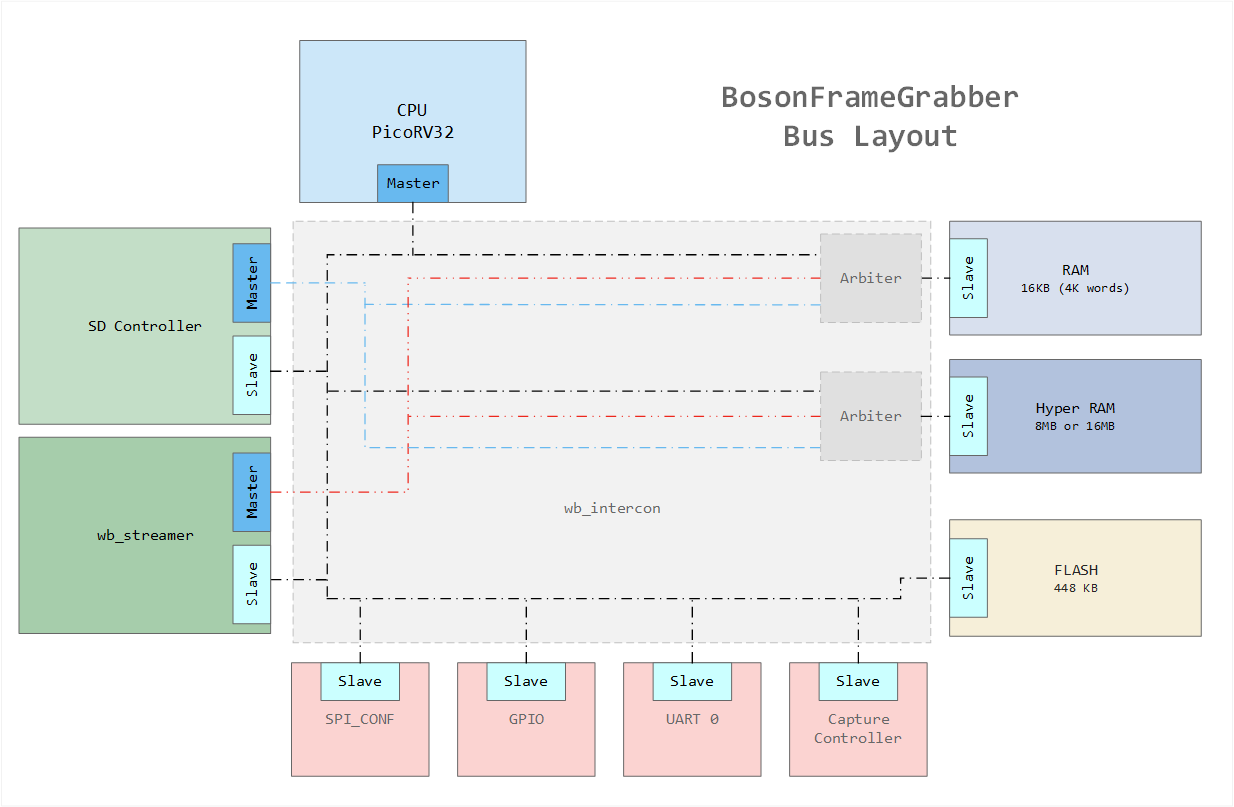

Here is the layout of the internal modules in the FPGA

All the components make use of a common wishbone bus. There are 3 masters that enable data-flow through the device without requiring the CPU. Basically these are simple DMA controllers.

All the components make use of a common wishbone bus. There are 3 masters that enable data-flow through the device without requiring the CPU. Basically these are simple DMA controllers. Everything is wired together using wb_intercon (https://github.com/olofk/wb_intercon). This package automatically creates a verilog file with muxes/arbiters/address decoders based on a simple config file.

I'm using picoRV32, as this worked very well on the HX8K hardware I started with. I studied RISCV in a computer architecture class, so I have a good base of knowledge when debugging issues. The CPU handles the filesystem using FatFS. This enables us to access FAT, and exFAT formatted SD cards.

The firmware is still very basic. It's operation is as follows

- Prime wb_streamer to capture the camera stream into HyperRAM.

- Wait for vsync signal from the camera.

- Capture 1 frames worth of data.

- The RISCV handles creating and allocating a new file. (IMG_0001.RAW)

- The DMA of the SD controller writes the file contents from HyperRAM into the SD card.

- We Finally blinks a LED and repeat.

To the user once powered all they see is the LED on the back of the camera blinking away.

greg davill

greg davill

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.

I just want to say that is really inspiring to read your posts (project logs). As a beginner in FPGA firmware and hardware development it's really great to see these kinds of projects. It's very motivating! Thanks for sharing it with us!

Are you sure? yes | no

Thank you for the kind words! :)

Are you sure? yes | no