-

Breadboarding braiNIAC ROM

03/17/2019 at 02:01 • 0 commentsAfter the completion of the IC level design, I could begin breadboarding. I began with the ROM module, which includes the 32k ROM chip and 4 4 bit counters to increment the address. You can view my designs from the last two logs, but I essentially just connected all the ICs to power and ground, wired up all the counter inputs to zero, chained them together through their clock lines, and connected all their data lines to the address pins of the ROM chip. I then connected ROM data lines and clock / reset lines from the counters to a female pin header on the breadboard for a simple user interface.

-

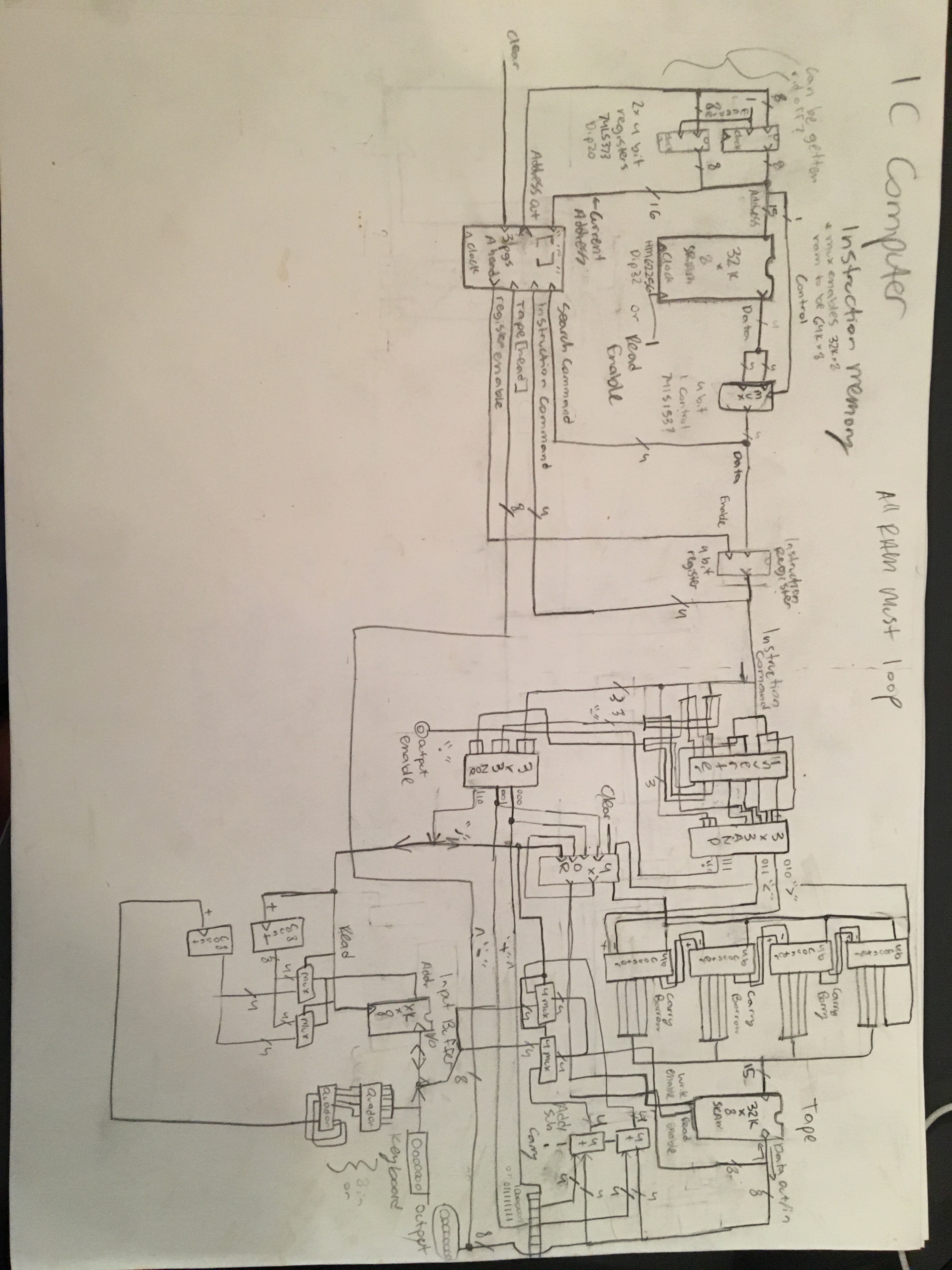

Redesigning braiNIAC At The IC Level

03/16/2019 at 19:28 • 0 commentsAfter simulating the computer on logisim, and being sure of its ability, I have to redesign it from the IC level on paper.

-

Designing BraiNIAC On Logisim

03/16/2019 at 19:23 • 1 commentI lost my original designs when I switched computers, so I have to start from scratch on simulating the computer on Logisim. Logisim is pretty high level, so I will need to redesign the computer from the IC level after completing the simulation.

Curtis Bucher

Curtis Bucher