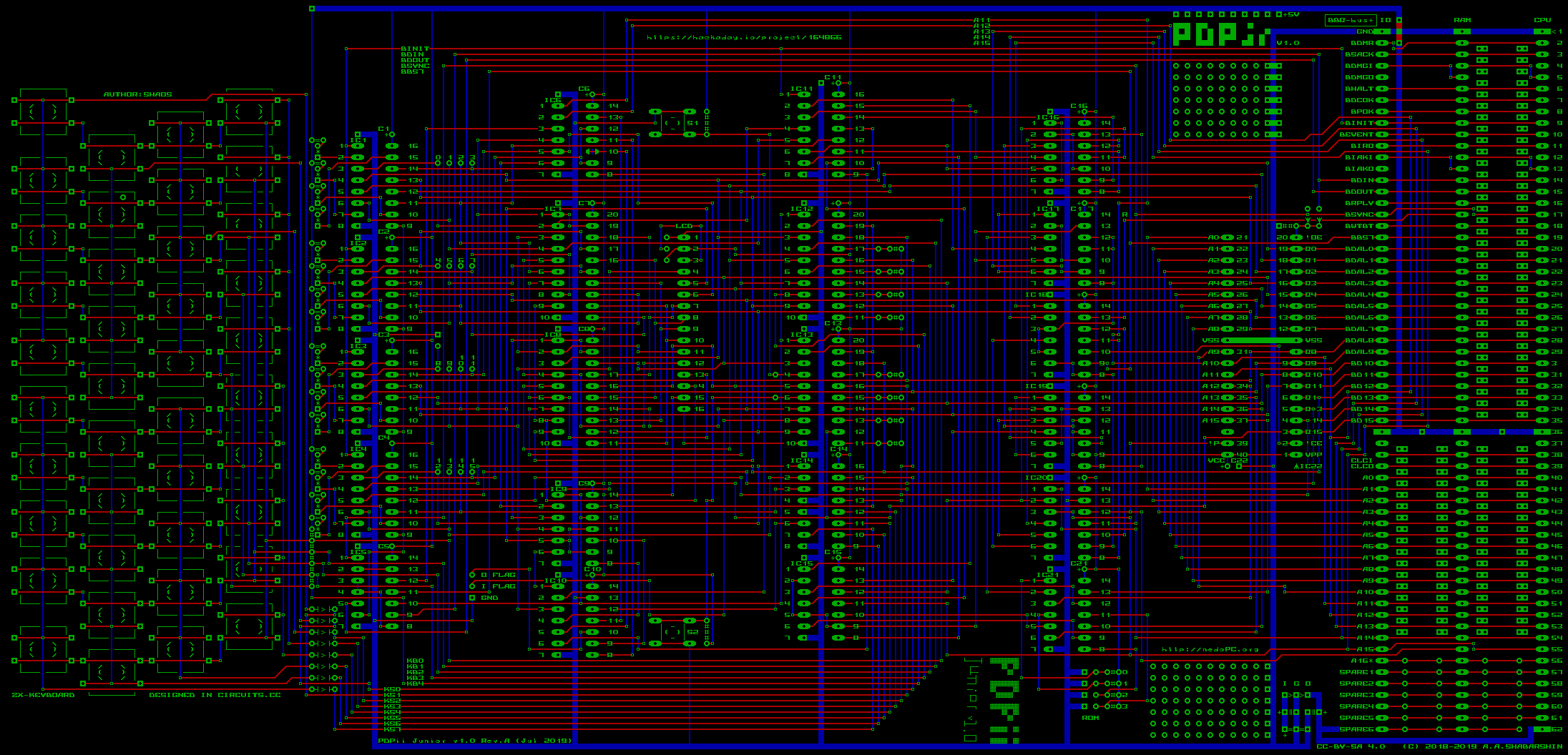

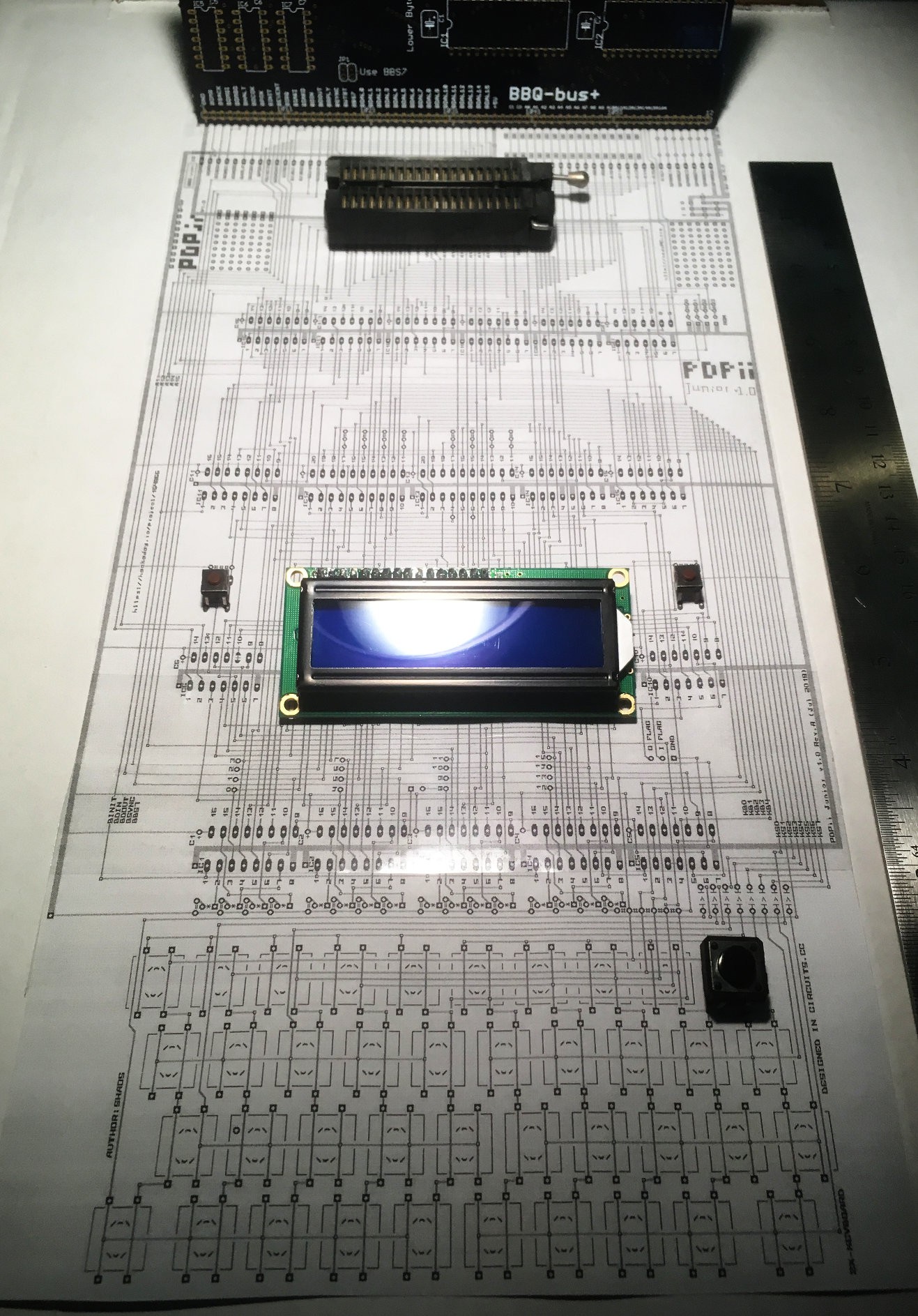

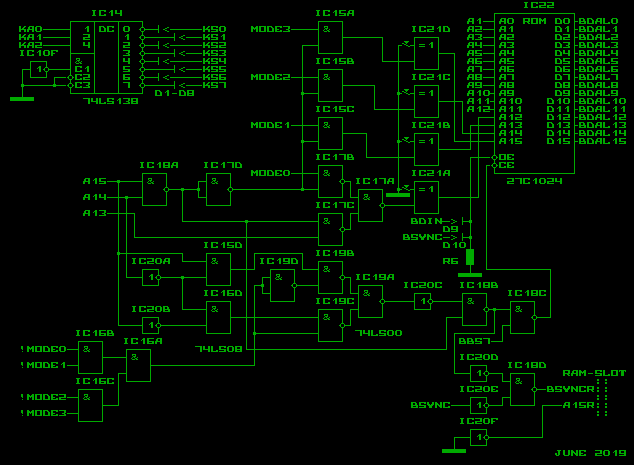

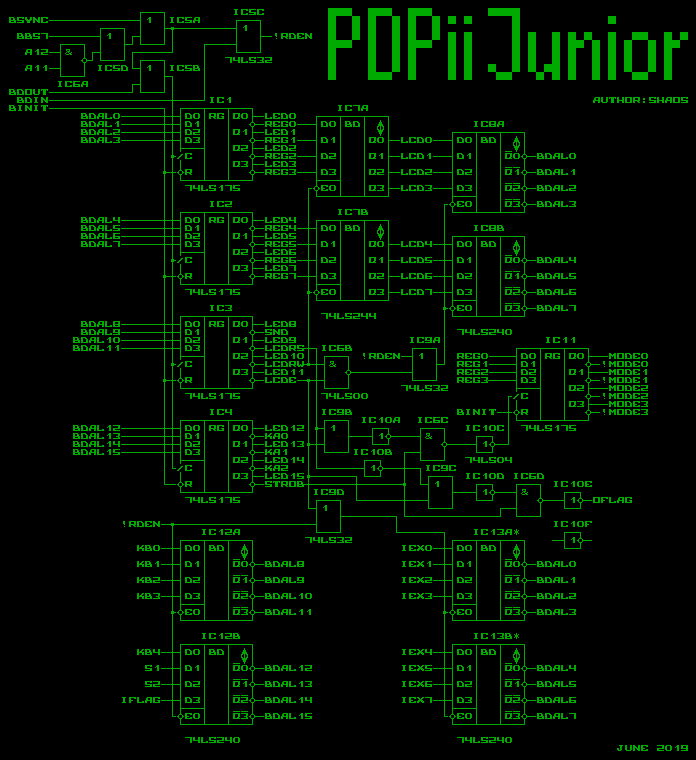

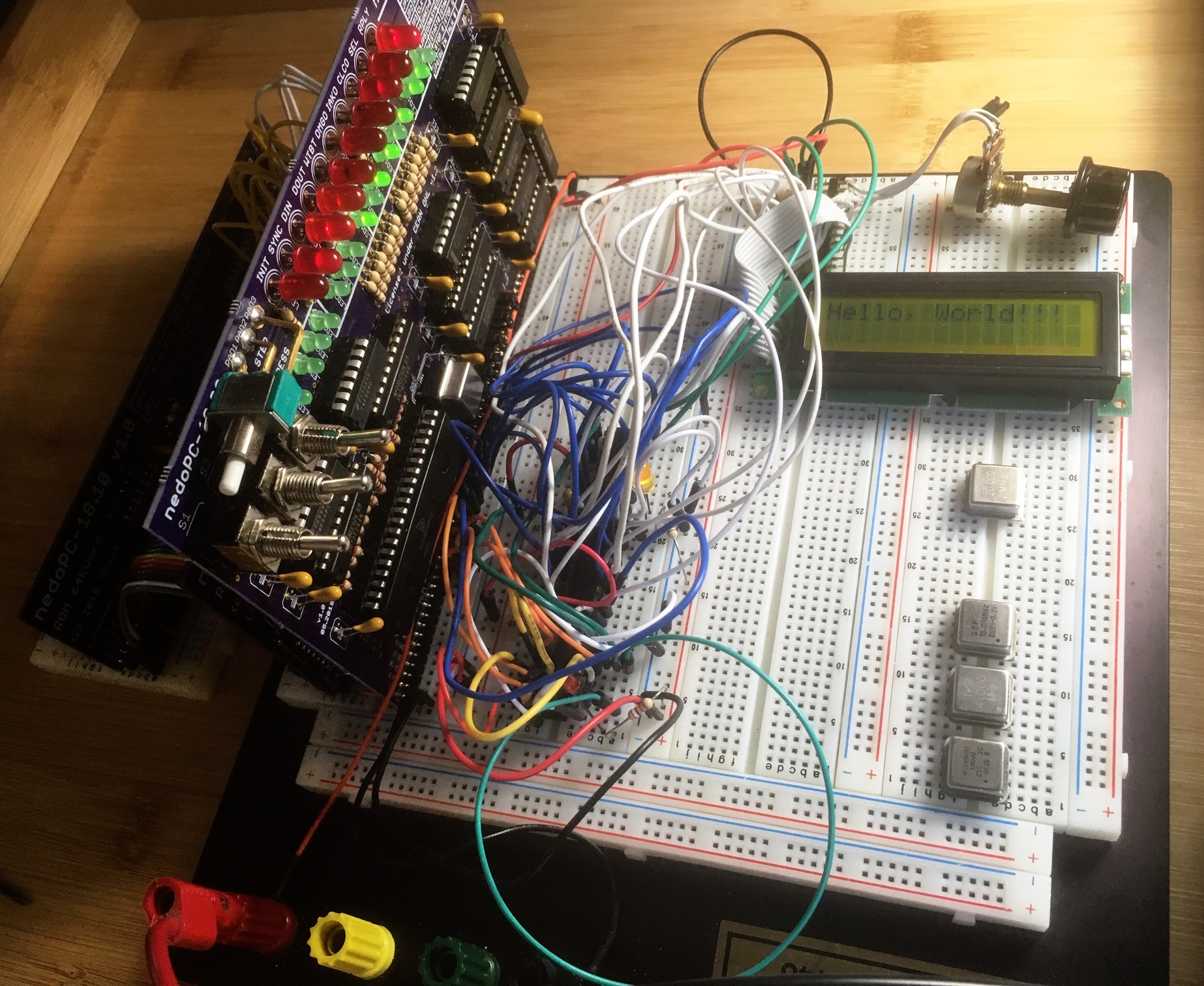

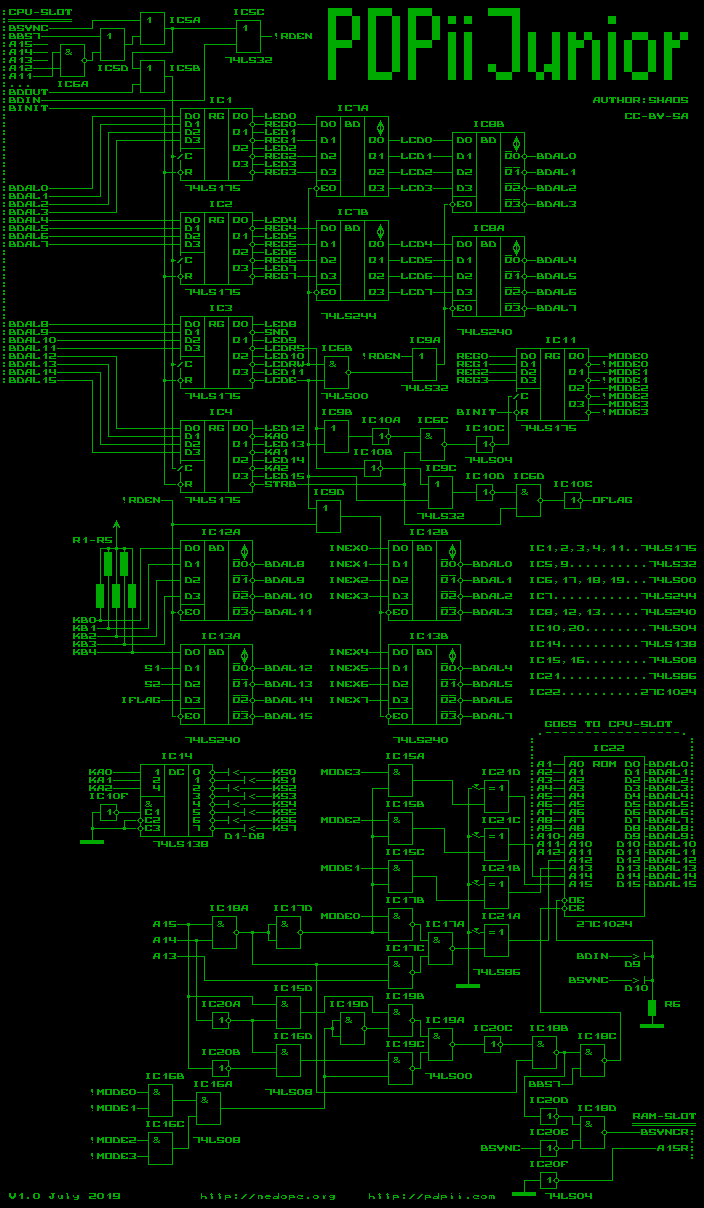

PDPii Junior is simplified #PDPii created specifically for Hackaday Prize 2019 in attempt to make a product. It will use CPU-module from #PDPii project with 1801VM2 (PDP-11 instruction set), #PDPii 16 KWords RAM module (in dedicated slot with slightly modified wiring to be able to mask RAM if needed) and also it will have 64 KWords ROM on-board (single chip 27C1024), 16x2 text LCD with parallel interface and on-board keyboard that is similar to ZX-Spectrum one (but it will be possible to connect any matrix keyboard with up to 104 buttons with help of 8 extra inputs). Current state:

Goal number 1 - run RT-11, stretch goal - run downsized Unix :)

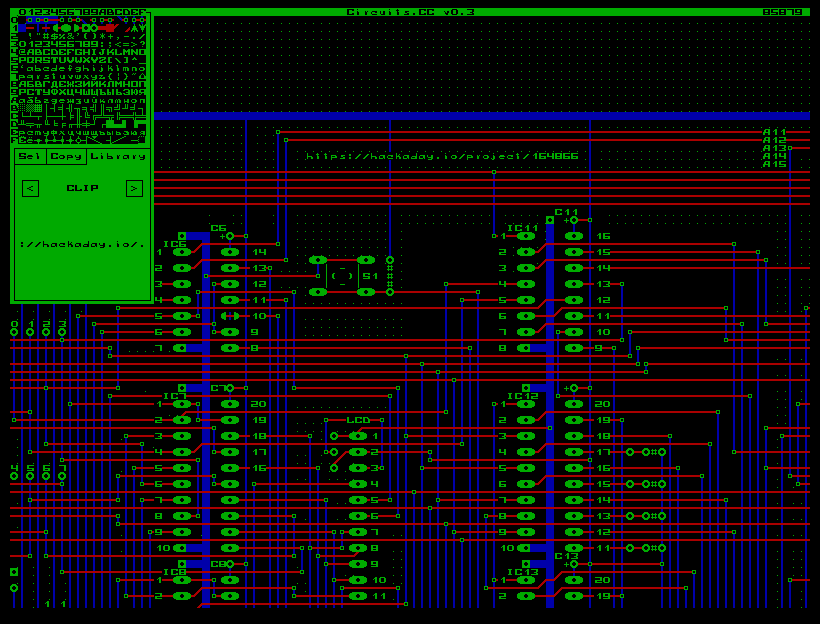

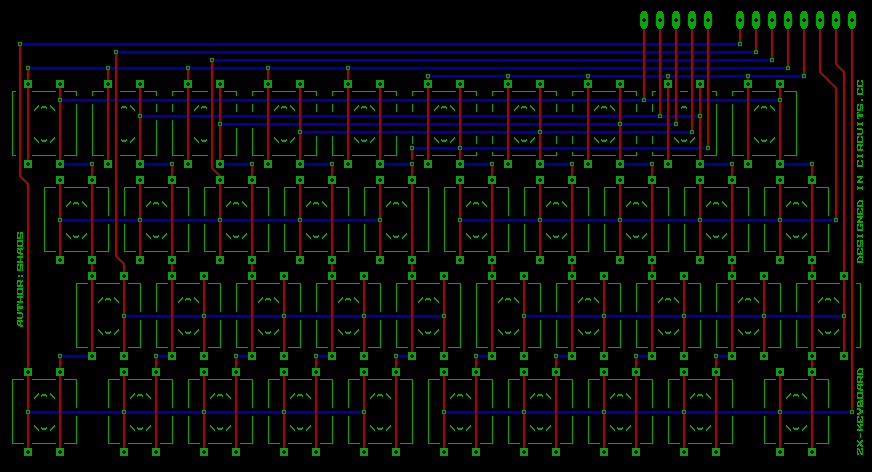

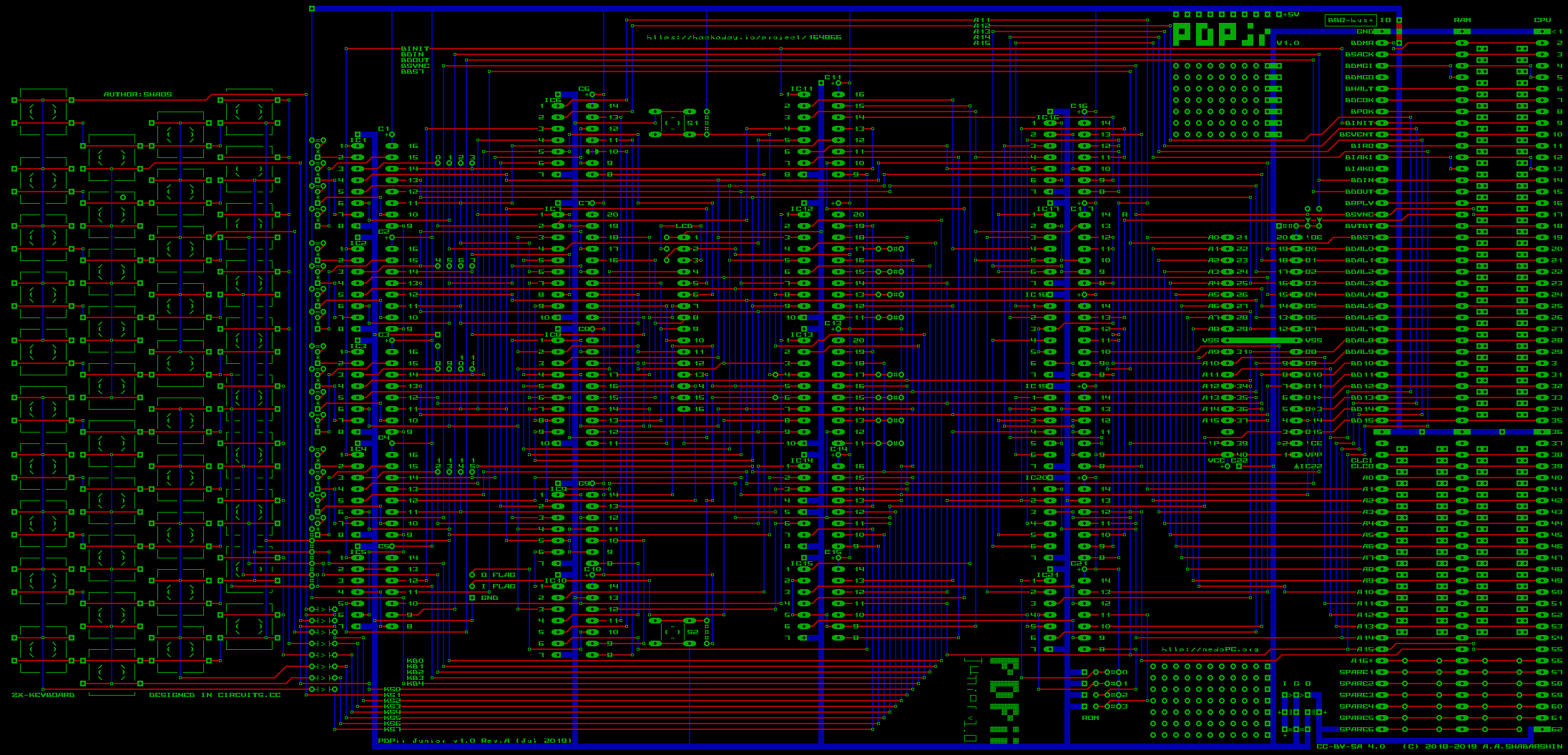

Also as part of this project I want to create an open source tool that will do auto-routing with Gerber output based on netlist. For now I do manual drawing in my own online multiuser PCB and schematics editor http://Circuits.CC :

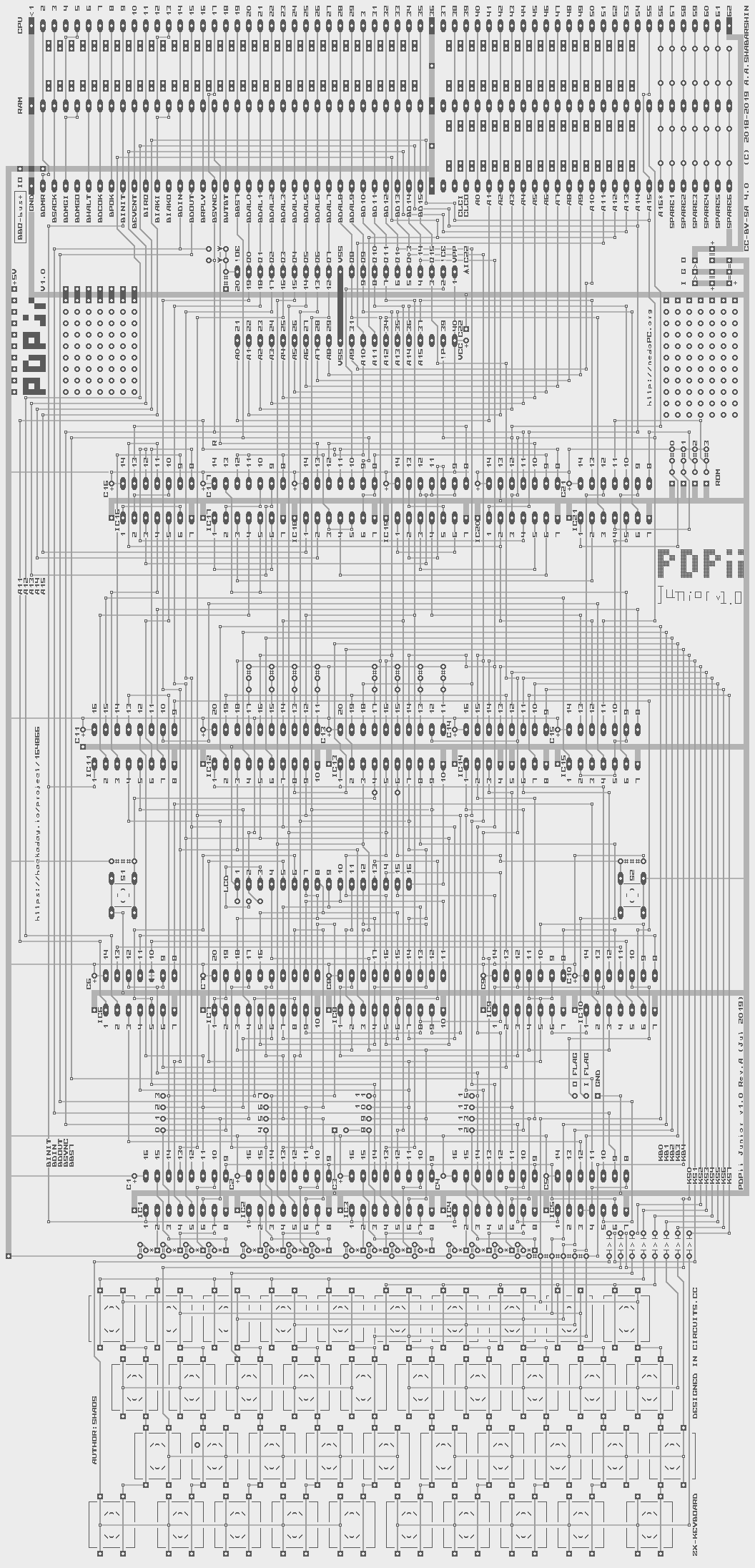

PCB dimensions are 6.6 x 13.7 inches:

PCB dimensions are 6.6 x 13.7 inches:

Hackaday article (July 13, 2019):

Hackaday article (July 13, 2019): https://hackaday.com/2019/07/13/a-pdp-laptop-for-various-definitions-of-a-laptop/

SHAOS

SHAOS