The Chip-beacon has sounded; he is on his way. . .somewhere.

The Chip-beacon has sounded; he is on his way. . .somewhere.

Welcome everyone, thanks for joining the Hack Chat today. We've got Ken and Chip Gracey from Parallax here today, ready to answer all your questions.

Welcome everyone, thanks for joining the Hack Chat today. We've got Ken and Chip Gracey from Parallax here today, ready to answer all your questions.

Ken, Chip - welcome aboard and thanks for taking time out of your day for us. Looks like we have Jeff Martin too?

![]() Jeff Martin and I are both here, from Parallax.

Jeff Martin and I are both here, from Parallax.

Chip is still logging in; password update and here he comes. Yep, you have Jeff Martin and David Carrier here as well.

Chip is still logging in; password update and here he comes. Yep, you have Jeff Martin and David Carrier here as well.

Okay, I think I'm in.

Okay, I think I'm in.

Welcome to all the Parallax team then! Thanks for joining us today.

Welcome to all the Parallax team then! Thanks for joining us today.

Jeff has developed our software tools for 20+ yrs and participated in P1 design; David does firmware, PCB design, manufacturing support and anything else. Fozzie is here.

Jeff has developed our software tools for 20+ yrs and participated in P1 design; David does firmware, PCB design, manufacturing support and anything else. Fozzie is here.

![]() Hi everyone!

Hi everyone!

[Kamilion] Hi guys! Guess the first question is, how are things looking with the die test at onsemi? We're all awaiting the P2 for xmas with baited breath.

[Kamilion] Hi guys! Guess the first question is, how are things looking with the die test at onsemi? We're all awaiting the P2 for xmas with baited breath.

Hello, Boian.

Hello, Boian.

![]() Jim (Publison) here to provide bodygaurd provisions for Ken ana Chip

Jim (Publison) here to provide bodygaurd provisions for Ken ana Chip

[de∫hipu] bated breath

[de∫hipu] bated breath

![]() Hi Ken, Chip. Wanted to say I'm a huge fan of Chips work. I ran sxlist.com back in the day and appreciated being able to translate PIC code to SX and run it 4x faster. (or nearly 4X, jumps killed the que of course)

Hi Ken, Chip. Wanted to say I'm a huge fan of Chips work. I ran sxlist.com back in the day and appreciated being able to translate PIC code to SX and run it 4x faster. (or nearly 4X, jumps killed the que of course)

hmmmm it smells like ASIC here :-)

hmmmm it smells like ASIC here :-)

Chip will answer the die-testing question; I'll address the availability of chips by ChipMas.

Chip will answer the die-testing question; I'll address the availability of chips by ChipMas.

Well, the chips we got back, initially, work great. However, ON Semi started running into lots of trouble testing the remaining wafers. It turns out that we have a latch-up problem in the I/O circuit that will require a slight redesign.

Well, the chips we got back, initially, work great. However, ON Semi started running into lots of trouble testing the remaining wafers. It turns out that we have a latch-up problem in the I/O circuit that will require a slight redesign.

![]() James, I am glad sxlist is still running, I used it to find something last year, when working on an SX project!

James, I am glad sxlist is still running, I used it to find something last year, when working on an SX project!

ON Semi has about 1K die (possibly more) which are engineering samples we will soon have packaged. They plan on getting the packaging done after they unravel the current testing issues with Chip. At that time, we're looking at about 7 weeks from release to packaging.

ON Semi has about 1K die (possibly more) which are engineering samples we will soon have packaged. They plan on getting the packaging done after they unravel the current testing issues with Chip. At that time, we're looking at about 7 weeks from release to packaging.

chip testing can look dull but it's actually something I focus on in some of my Hackaday projects, so please elaborate and explain you workflow :-)

chip testing can look dull but it's actually something I focus on in some of my Hackaday projects, so please elaborate and explain you workflow :-)

![]() Huge fan of Kens work as well, but the chip work (see what I did there?) was amazing.

Huge fan of Kens work as well, but the chip work (see what I did there?) was amazing.

The chips that we have here work better than anticipated, since the PLL got cleaned up and the new clock-gating cut the power consumption in half.

The chips that we have here work better than anticipated, since the PLL got cleaned up and the new clock-gating cut the power consumption in half.

[Kamilion] aye, I've been following along on the forum with the die tests; and watched the call go out to P2-ES gloptop owners to check the IO resistances

[Kamilion] aye, I've been following along on the forum with the die tests; and watched the call go out to P2-ES gloptop owners to check the IO resistances

clock gating ? swwweeeeeet :-)

clock gating ? swwweeeeeet :-)

[Kamilion] I'm still in awe y'all managed to blow past 300Mhz for a fMAX of 185Mhz/85C

[Kamilion] I'm still in awe y'all managed to blow past 300Mhz for a fMAX of 185Mhz/85C

These 1K chips could easily help us build another 250 Propeller 2 Evaluation Boards and accessories. I think it's realistic to say we'll have these boards available ChipMas (if I have to guess) so we all have something productive to do when relatives come over.

These 1K chips could easily help us build another 250 Propeller 2 Evaluation Boards and accessories. I think it's realistic to say we'll have these boards available ChipMas (if I have to guess) so we all have something productive to do when relatives come over.

[Kamilion] reminds me of the old Celeron 300A -> 450Mhz

[Kamilion] reminds me of the old Celeron 300A -> 450Mhz

![]() Chip, were the Rev1 chips put through the same testing as rev 2?

Chip, were the Rev1 chips put through the same testing as rev 2?

I'm hoping we can get a few hundred chips out of the current lot, before the next fab turn. We are ready to build lots of new P2 Eval boards.

I'm hoping we can get a few hundred chips out of the current lot, before the next fab turn. We are ready to build lots of new P2 Eval boards.

[Kamilion] I just wanna say, I am TOTALLY fine with a "preproduction" with a disabled bank of smartpins for chipmas.

[Kamilion] I just wanna say, I am TOTALLY fine with a "preproduction" with a disabled bank of smartpins for chipmas.

@engineering, yes. Due to some lower substrate resistance, though, the latch-up problem reared its head.

@engineering, yes. Due to some lower substrate resistance, though, the latch-up problem reared its head.

@IRC, these chips will have no disabilities.

@IRC, these chips will have no disabilities.

@Kamilion good to know. This kind of flexibility has been appreciated. It seems that your chips would be fully functional.

@Kamilion good to know. This kind of flexibility has been appreciated. It seems that your chips would be fully functional.

Anyway, it feels like we got to the finish line, but tripped over it.

Anyway, it feels like we got to the finish line, but tripped over it.

![]() @Chip Gracey - How will engineering sample users prevent the latch up problem?

@Chip Gracey - How will engineering sample users prevent the latch up problem?

Chip design is an art ;-)

Chip design is an art ;-)

For those looking for more detail than a chat can provide, this is a good start https://propeller.parallax.com/

For those looking for more detail than a chat can provide, this is a good start https://propeller.parallax.com/

In the next few days, we should have these silicon problems remedied, but then we need to wait for another fab run to get final production parts.

In the next few days, we should have these silicon problems remedied, but then we need to wait for another fab run to get final production parts.

![]() Since I haven't really been following the propeller closely, can someone set the stage for this with the back story? What's been the issue?

Since I haven't really been following the propeller closely, can someone set the stage for this with the back story? What's been the issue?

![]() Kamilion, none of them will be wasted; we'll use the ones with bad pins for internal development.

Kamilion, none of them will be wasted; we'll use the ones with bad pins for internal development.

![]() Ah, nevermind, just saw the line.

Ah, nevermind, just saw the line.

![]() link

link

@jeff, there is nothing to do on the user's end. Some chips just won't latch up. Others will.

@jeff, there is nothing to do on the user's end. Some chips just won't latch up. Others will.

[Kamilion] backstory here, James: http://forums.parallax.com/discussion/170380/new-p2-silicon/

[Kamilion] backstory here, James: http://forums.parallax.com/discussion/170380/new-p2-silicon/

![]() thanks

thanks

[Kamilion] V2431 is the one that is most concerning to me

[Kamilion] V2431 is the one that is most concerning to me

![]() In general, don't send signals to I/O pins, before powering on a semiconductor.

In general, don't send signals to I/O pins, before powering on a semiconductor.

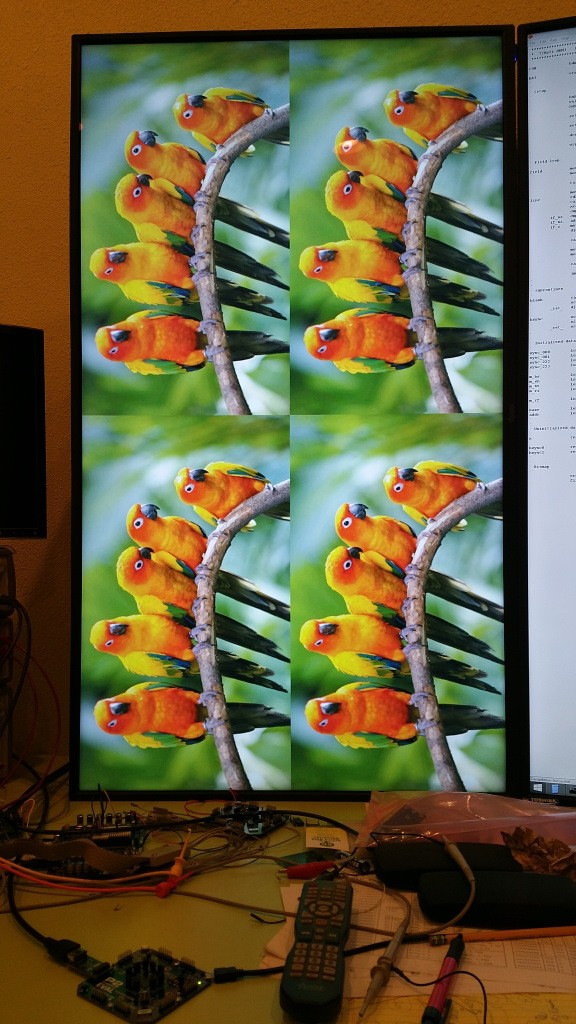

Everything checks out okay on the new silicon. The HDMI works, the scope pins work, etc.

Everything checks out okay on the new silicon. The HDMI works, the scope pins work, etc.

[Arsenijs] HDMI? that's cool!

[Arsenijs] HDMI? that's cool!

So it sounds like P2 will be production ready around Christmas / Chipmas? Any chance of a P2 Expo before that?

So it sounds like P2 will be production ready around Christmas / Chipmas? Any chance of a P2 Expo before that?

Can HDMI out be repurposed ? :-D

Can HDMI out be repurposed ? :-D

@IRC, the latch-up can occur on any VIO pin. We've seen it all over on some dies at ON Semi.

@IRC, the latch-up can occur on any VIO pin. We've seen it all over on some dies at ON Semi.

![]() We can't have a P2 expo without P2s, so an Expo will have to be after.

We can't have a P2 expo without P2s, so an Expo will have to be after.

@yann, HDMI can be repurposed if you can use the TMDS encoding in another type of application.

@yann, HDMI can be repurposed if you can use the TMDS encoding in another type of application.

![]() @David Carrier - Yeah, we "tried" that once before. ;-P

@David Carrier - Yeah, we "tried" that once before. ;-P

@Jac Goudsmit a P2 Expo has definitely been on our minds and will be planned. When (a) we have enough chips on hand for people to build their own boards (maybe before December, if we allocate some of the 1K units for individual sale) and (b) we have six months to plan it we can schedule. I'm really hoping we can have an Expo by May.

@Jac Goudsmit a P2 Expo has definitely been on our minds and will be planned. When (a) we have enough chips on hand for people to build their own boards (maybe before December, if we allocate some of the 1K units for individual sale) and (b) we have six months to plan it we can schedule. I'm really hoping we can have an Expo by May.

@Chip some high-bandwidth interco maybe ? :-D

@Chip some high-bandwidth interco maybe ? :-D

With the new streamer and scope pins, you can capture two analog channels and 16 I/O pins in every clock. That replicates my desk scope function, but the analog bandwith is only a few MHz.

With the new streamer and scope pins, you can capture two analog channels and 16 I/O pins in every clock. That replicates my desk scope function, but the analog bandwith is only a few MHz.

[Kamilion] the i/q stuff works in the respin too :D

[Kamilion] the i/q stuff works in the respin too :D

Yes, the IQ modulators work on the new silicon. So do the rotary encoder inputs.

Yes, the IQ modulators work on the new silicon. So do the rotary encoder inputs.

![]() Someone really needs to pickup and run with the SDRAM Thing idea for a low cost scope. The P2 could provide logic and IO for that pretty easily.

Someone really needs to pickup and run with the SDRAM Thing idea for a low cost scope. The P2 could provide logic and IO for that pretty easily.

It's frustrating - everything works, but we don't have production chips, yet.

It's frustrating - everything works, but we don't have production chips, yet.

![]() Hello Chip!

Hello Chip!

Hi, JDat.

Hi, JDat.

![]() Sorry for repetitive question: what about code protection on chip?

Sorry for repetitive question: what about code protection on chip?

Chip, what does it feel like to work on the same project for so many years?

Chip, what does it feel like to work on the same project for so many years?

[Kamilion] James, there's already a HyperRAM board rolled up using http://www.issi.com/US/product-cellular-ram.shtml (similar ISSI PSRAM chip to what's found on the ESP32-WROVER-B )

[Kamilion] James, there's already a HyperRAM board rolled up using http://www.issi.com/US/product-cellular-ram.shtml (similar ISSI PSRAM chip to what's found on the ESP32-WROVER-B )

![]() Besides taco machines? :)

Besides taco machines? :)

![]() Hello Ken and Chip! Glad to hear the ON believes they found the cause of the latchup problem. Can't wait to get a P2ES Rev.B :)

Hello Ken and Chip! Glad to hear the ON believes they found the cause of the latchup problem. Can't wait to get a P2ES Rev.B :)

@ken, it's like wandering in the desert for 40 years. It's great when it finally comes together, though, and everything is working better than hoped.

@ken, it's like wandering in the desert for 40 years. It's great when it finally comes together, though, and everything is working better than hoped.

[Arsenijs] me away for 3 minutes

[Arsenijs] me away for 3 minutes

[Arsenijs] *30

[Arsenijs] *30

The world changes a lot in 13 years. I hope there are still lots of inventors out there who want to build from a first-principles basis, and make things they have absolute control over.

The world changes a lot in 13 years. I hope there are still lots of inventors out there who want to build from a first-principles basis, and make things they have absolute control over.

![]() Kamilion, I don't want to derail chat, but I don't see the point of those HyperRAM boards just based on the cost vs standard SDRAM. Can we chat about that separately?

Kamilion, I don't want to derail chat, but I don't see the point of those HyperRAM boards just based on the cost vs standard SDRAM. Can we chat about that separately?

![]() Chip, not sure it has been asked on the fourm; wile the rev2 work on a rev1ES board?

Chip, not sure it has been asked on the fourm; wile the rev2 work on a rev1ES board?

![]() I thing that P2 is coming on right time. Mainstream marked for DIYers is stabilised and you know what onchip peripherals are necessary for DIYers and can offer exactly what people need.

I thing that P2 is coming on right time. Mainstream marked for DIYers is stabilised and you know what onchip peripherals are necessary for DIYers and can offer exactly what people need.

@james, HyperRAM takes only 11 pins. SDRAM takes at least double, if I recall.

@james, HyperRAM takes only 11 pins. SDRAM takes at least double, if I recall.

C64 ISEPIC 1986

C64 ISEPIC 1986

Apple 2 SoundAce 1987 (?)

PIC Programmer 1990

BASIC Stamp 1 1992

BASIC Stamp II 1995

SX Key/Chips 1997

Propeller 1 2006

A bit of Chip's development history.

![]() Chip, can you explain why you feel the P2 is still relevant in this day and age of lower cost FPGAs and other silicon?

Chip, can you explain why you feel the P2 is still relevant in this day and age of lower cost FPGAs and other silicon?

![]() For those interested, we plan on making the P2 compatible with all xSPI devices, including HyperRAM. It is a new protocol, but as more companies implement it, the price is dropping quickly.

For those interested, we plan on making the P2 compatible with all xSPI devices, including HyperRAM. It is a new protocol, but as more companies implement it, the price is dropping quickly.

@james, I think the P2 will be relevant because it lets you control signal timing easily. FPGAs can do that, but with much complexity along the way. Microcontrollers can't do that, unless they have dedicated silicon peripherals. With the P2, you can cook up your own.

@james, I think the P2 will be relevant because it lets you control signal timing easily. FPGAs can do that, but with much complexity along the way. Microcontrollers can't do that, unless they have dedicated silicon peripherals. With the P2, you can cook up your own.

![]() Chip, the SDRAM thing idea uses most of those pins to make the RAM drive itself. You don't need all of them... but yes, more than 11... If hyperram prices drop, it's worth doing.

Chip, the SDRAM thing idea uses most of those pins to make the RAM drive itself. You don't need all of them... but yes, more than 11... If hyperram prices drop, it's worth doing.

![]() So, like the SX, it makes bit banging "virtual peripherals" easy?

So, like the SX, it makes bit banging "virtual peripherals" easy?

![]() Chip did you count how many times Ken told you: "We need to finish P2" ?

Chip did you count how many times Ken told you: "We need to finish P2" ?

[Kamilion] personally, it's relevant as "another fast MCU that isn't leveraging linux", and thus inheriting all the realtime quirks of linux. I am really interested in using it for physical interfacing, and as an inexpensive alternative to stupid-expensive asics like RA8876L

[Kamilion] personally, it's relevant as "another fast MCU that isn't leveraging linux", and thus inheriting all the realtime quirks of linux. I am really interested in using it for physical interfacing, and as an inexpensive alternative to stupid-expensive asics like RA8876L

My push now is to get Spin2 working, which will make a very easy and fast test bed for demonstrating P2 capabilities.

My push now is to get Spin2 working, which will make a very easy and fast test bed for demonstrating P2 capabilities.

![]() The P1 is excellent at implementing designs that would otherwise require an FPGA, but allowing easier sequential programming. The P2 ups those capabilities, meaning that more designs that would have required the longer design time of an FPGA are possible with easier sequential programming.

The P1 is excellent at implementing designs that would otherwise require an FPGA, but allowing easier sequential programming. The P2 ups those capabilities, meaning that more designs that would have required the longer design time of an FPGA are possible with easier sequential programming.

Just because the unit price of an FPGA is dropping doesn't mean that the extra development time is worth it.

![]() @IRC - or some other RTOS. Agreed.

@IRC - or some other RTOS. Agreed.

![]() Hi Chip - I have been using the P1 since 2006 on altitude-controlled balloons - flown at both poles and many places between up to 18kft. Have also been developing a 4-axis stepper driver / gcode interpreter using the P1. I am very excited about the P2 and look forward to working with it soon! I am in awe of your work.

Hi Chip - I have been using the P1 since 2006 on altitude-controlled balloons - flown at both poles and many places between up to 18kft. Have also been developing a 4-axis stepper driver / gcode interpreter using the P1. I am very excited about the P2 and look forward to working with it soon! I am in awe of your work.

Yes, Ken has said many times that P2 must be done. My dad was saying that everyday for years. Before the P1 was done, Ken was getting really upset with me that it was taking so long. My dad was a calming factor.

Yes, Ken has said many times that P2 must be done. My dad was saying that everyday for years. Before the P1 was done, Ken was getting really upset with me that it was taking so long. My dad was a calming factor.

[Kamilion] yeah, FOMU demonstrates that a cheap FPGA is nice, but having to wait for the logic to settle on powerup can be an issue for many designs.

[Kamilion] yeah, FOMU demonstrates that a cheap FPGA is nice, but having to wait for the logic to settle on powerup can be an issue for many designs.

@Pvoss, I think you will like it.

@Pvoss, I think you will like it.

![]() David Carrier, glad to see you here.

David Carrier, glad to see you here.

![]() @pvoss - do you have any temperature data to share? Extremes?

@pvoss - do you have any temperature data to share? Extremes?

![]() The powerup delay can be a serious issue... especially motor drivers and servo controllers and the like. A lot of bad things can happen in uS and they don't always bias things correctly for no action until ready.

The powerup delay can be a serious issue... especially motor drivers and servo controllers and the like. A lot of bad things can happen in uS and they don't always bias things correctly for no action until ready.

[Kamilion] the kendryte K210's FpIO is also very nice, but it's more of a pin matrix mux, versus the p2's eggbeater. ESP32's also got internal peripheral to pin mux, but it's not very flexible.

[Kamilion] the kendryte K210's FpIO is also very nice, but it's more of a pin matrix mux, versus the p2's eggbeater. ESP32's also got internal peripheral to pin mux, but it's not very flexible.

![]() Is there going to be a focus on being able to use Blocky with the P2 or is Spin2 going to be the main programming method?

Is there going to be a focus on being able to use Blocky with the P2 or is Spin2 going to be the main programming method?

[Kamilion] And then there's cypress. Nice hardware, but way too expensive to license IP if you ever want to go into production. ( like $11k/yr for just the USB core, ugh )

[Kamilion] And then there's cypress. Nice hardware, but way too expensive to license IP if you ever want to go into production. ( like $11k/yr for just the USB core, ugh )

[Kamilion] Joshua, Blockly and stuff will probably be driven by the community

[Kamilion] Joshua, Blockly and stuff will probably be driven by the community

Jmg, a guy on the forum, really pushed for fast boot-up on the P2. I believe the P2 can power-up and start running user code in about 30ms.

Jmg, a guy on the forum, really pushed for fast boot-up on the P2. I believe the P2 can power-up and start running user code in about 30ms.

[Kamilion] IIRC, that 30ms does not include SD init, does it?

[Kamilion] IIRC, that 30ms does not include SD init, does it?

Lutetium

Lutetium

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.