-

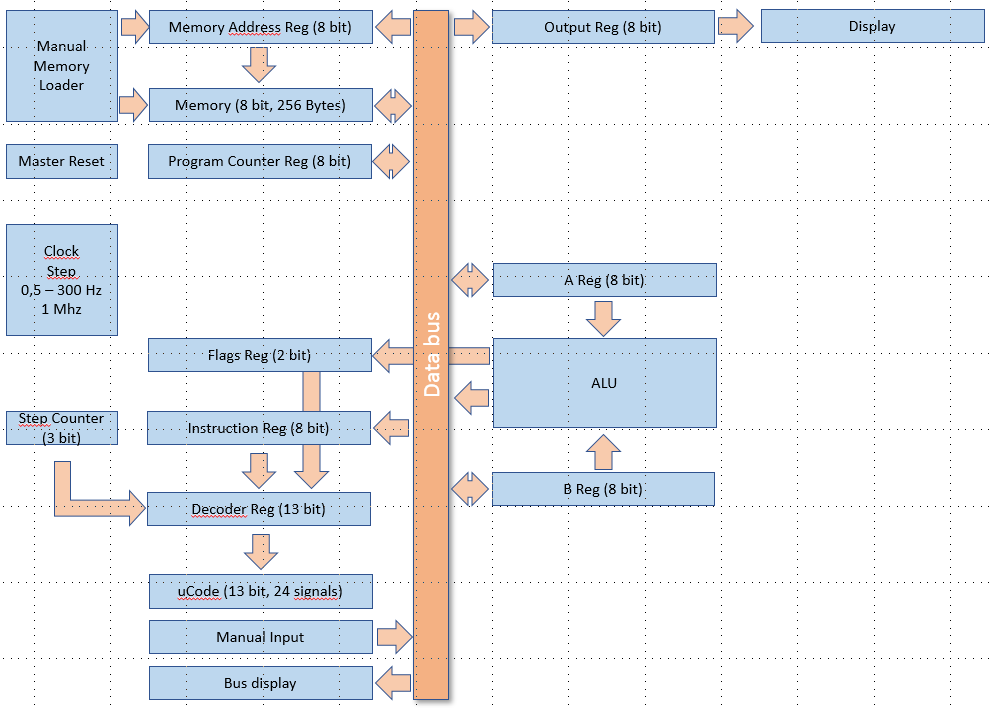

General Architecture

10/31/2019 at 16:41 • 0 commentsThe goal is to create a viable CPU with its own language able to run simple programs.

It is based on a Von Neumann architecture with the following features:

- 8 bit shared data bus

- 8 bit general purpose A register

- 8 bit general purpose B register

- 8 bit Program Counter register

- 8 bit Instruction register

- 8 bit memory address register

- 256 bytes non volatile static RAM

- Led visualisation at each level (registers, bus, status, etc)

- Dip switch manual entry (bus value, memory adrress and data programming)

- 4 digit 7 segment led display (signed / unsigned values)

- ALU with add / substract functions and the capability to evolve to more features

- Flag register with Carry Flag, Zero Flag

- EEPROM based instruction decoder with up to 24 action signals

- variable speed and step by step clock

The general architecture will evolve with updates to the project. However here are the basic elements:

The following modules will be detailed (order may vary):

- Bus module with bus value display and manual setting

- A & B registers (General purpose registers)

- Program Counter

- Memory including Memory Address register, Manual RAM loader, Ram out driver

- ALU with it's basic add/substract function, Flags register, R register (ALU result register)

- Instruction register

- Instruction decoder, stepper

- Input / Output, 7 segment display module

And of course, in order to understand the inner mechanics of the CPU:

- Micro instructions (action signals)

- Steps description

- Macro instruction

Ced

Ced