After observing the PLL performance over several days it became obvious that both the tracking accuracy and the loop stability could be improved. As a result I made the following changes:

- Added logging of PLL frequency correction.

- Increase effective DAC resolution to 16 bits through offset twiddling.

- Reduce PLL overshoot by applying adaptive gain based on error magnitude.

- Fix offset in error estimation by shifting clock bins 0.5 cycles to match ideal signal alignment.

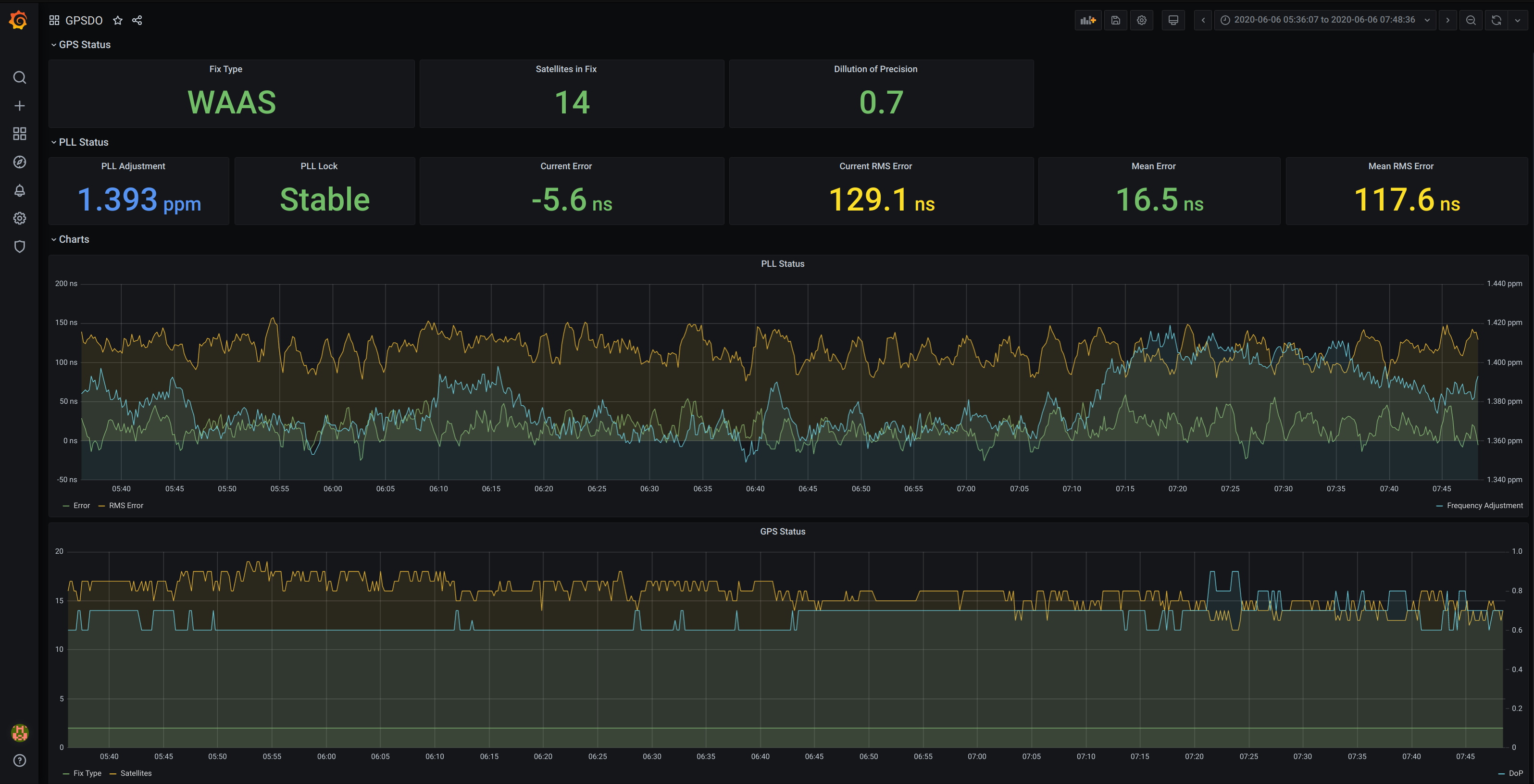

Before:

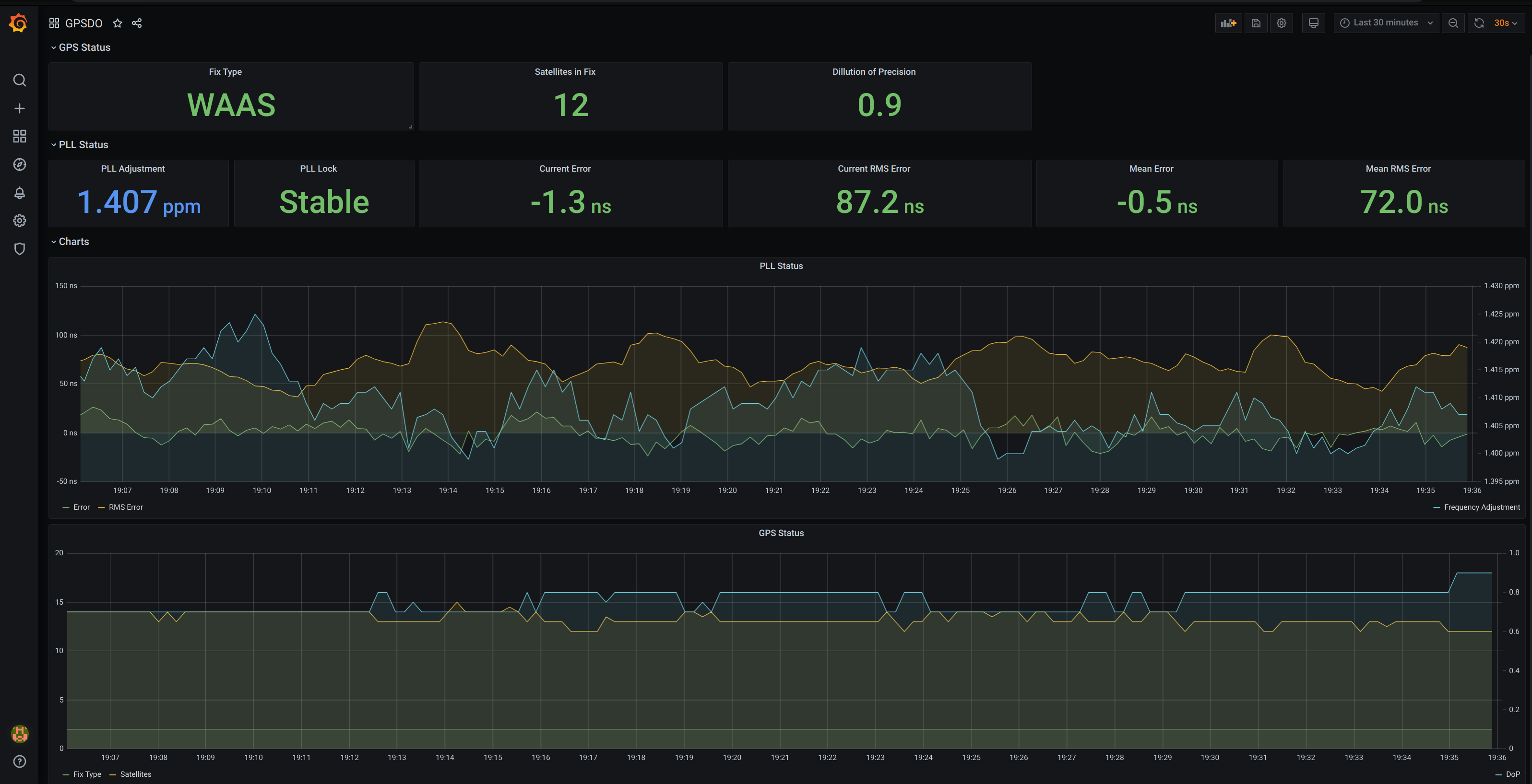

After:

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.