Two tables can be set aside for 16bit increment, though its likely I woud use a separate devices for 16bit counting. Avoid the complication of multiplexing different width results.

Two tables (sans carry, with carry) set aside for functions that might reference only one input byte. The other input byte can then select between 256+256 smaller tables.

Perhaps two tables set aside for packed flag results? We collide any 8 bits vs another 8 bits and out pop 2 cases of flags that might simultaneously represent carry, borrow, reverse subtract's borrow, zero and flags thrown by single byte tables vs 256 small functions as described above.

Not sure its a problem that flags aren't simulateous with results? Sometimes we just want to know wether to break out of a loop or branch, and knowing the numerical result is not important. Other times might need only a result. Unwanted flag updates may be irrelevant, even a nuisance.

Adding and subtracting wide numbers, and of course wide rotations seem to be the cases where a simultaneous carry output helps.

Is it worthwhile to parallel a smaller device to store flags?

Is it better to occupy half the width of the device with a scarce few flags? Carry could feed an address bit instead of selecting between two simultaneously presented cases. Might be the easy solution, but for the wasted potential...

More on this later, I got years of notes I need to clean up and try to make presentable.

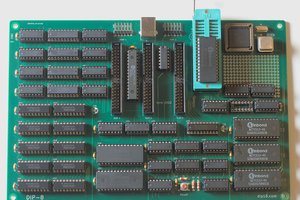

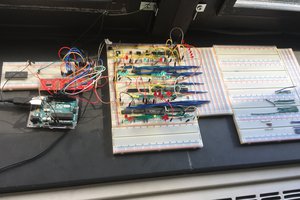

And I need a better DIP converter, compatible with normal breadboards. Not all pins of the TSOP-II 54 device need breakout. 40pin DIP might be plenty for an optimized breakout. The Cypress NVSRAM also requires a capacitor to backup volatile SRAM to quantum traps on shutdown. Everspin MRAM needs no backup capacitor. Otherwise the pinouts seem similar...

I don't actually have the pictured adaptor in hand at the moment, buried somewhere in storage. And this old photo has a filename that suggests a much smaller table space than the 16megabit I thought I had mounted. Hopefully I just mislabeled the photo or misread a faded number. In the photo, I count only 44 pins broken out, not 54. So probably stuck with 4Megabits and only 18 address lines. Suppose it can still find use as program counter or flags.

I didn't want to dumb this down to 7 bits, but might have to consider it now. Solves the flag problem and uses two less address bits which have suddenly discovered themselves in short supply.

kaimac

kaimac

Jorj Bauer

Jorj Bauer

Maciej Witkowiak

Maciej Witkowiak

can you share the source code of your program? I want to test it for my new program of Frankincense Resin store, you can see here https://frankincensedirect.com/shop/