I've wanted to build a 68000 system for a long time. I built some commercial systems back in the 1980's based on the 68000 and really like the CPU.

There's a few 68000 builds on YouTube. The best documented 68000 build is Jeff Tranter's build of the TS2. Jeff has a very nice build BLOG and demonstration video on YouTube.

The TS2 is based on Alan Clements' book Microprocessor Systems Design: 68000 Family Hardware, Software, and Interfacing. The advantage starting from a published book is that the documentation of the design is really good.

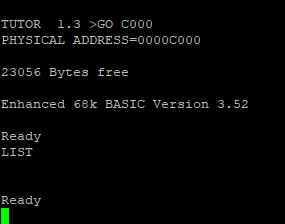

There was a commercial design that is compatible, the Motorola MC68000 Educational Computer Board (MEX68KECB) (referred to as MECB). There is a TUTOR monitor, Tiny BASIC, Enhanced BASIC, and FORTH for the board.

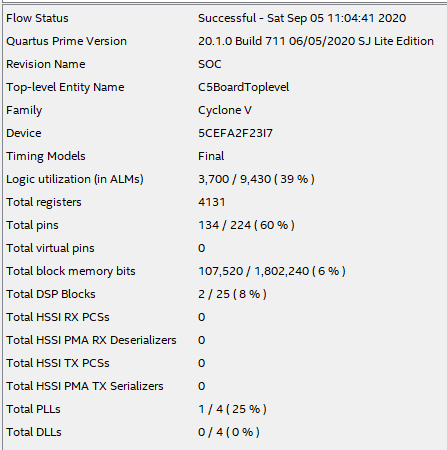

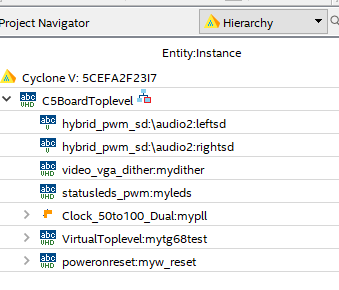

The design doesn't fit into the minimal Multicomp FPGA board due to the memory requirements. It does fit into a larger FPGA like the Altera/Intel EP4CE15. I am using my RETRO-EP4CE15 card as the hardware platform which support Cyclone IV and Cyclone V FPGAs..

The main features are:

- M68000 CPU

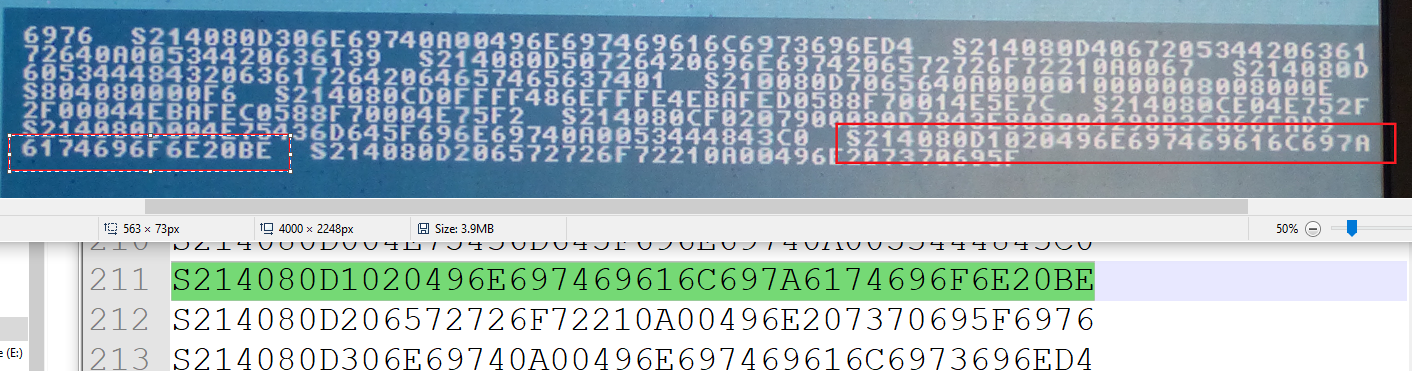

- Teesite TS2BUG (4KB) or MECB TUTOR (16KB) Monitor ROMs

- 32KB Internal SRAM

- More SRAM depending on FPGA size

- 144 KB SRAM on 5CEFA2F23I7N

- More SRAM depending on FPGA size

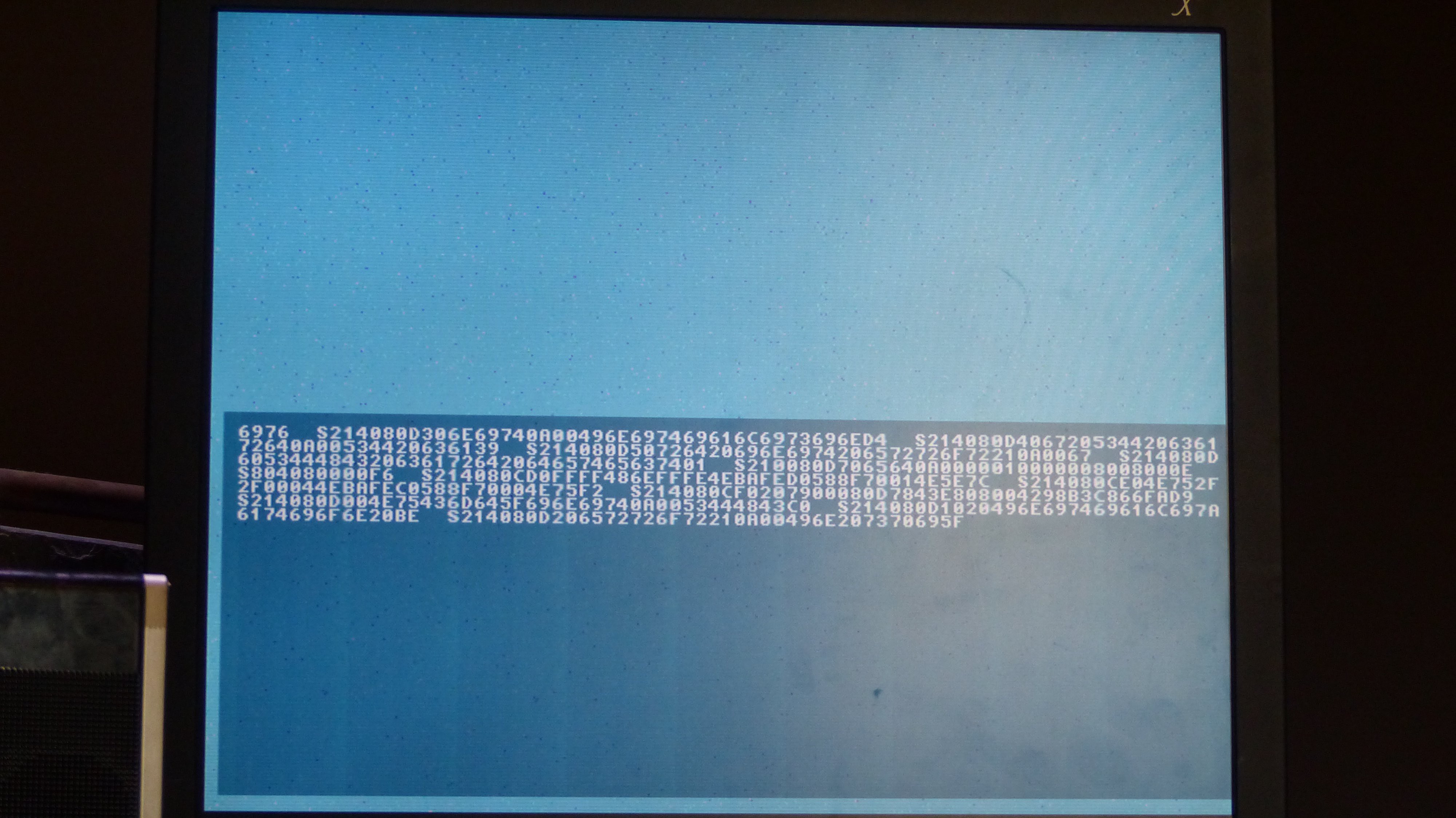

- ANSI Video Display Unit (VDU)

- VGA and PS/2

- 6850 ACIA UART

- USB to Serial

- SD Card

- Supports SD or SDHC cards

- GPIO

- 3 + 8 + 8 Input-Output bits

- USB powered over USB-Serial connection

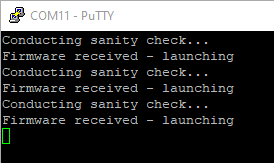

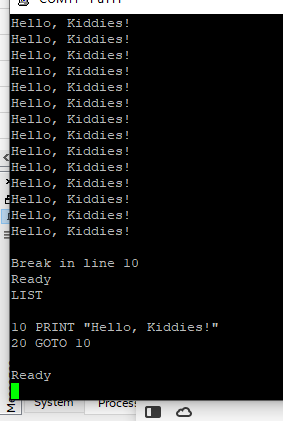

The board works and loads Gordo's MC68000 Tiny BASIC v1.2 as well as EnhBASIC.

land-boards.com

land-boards.com

f4hdk

f4hdk

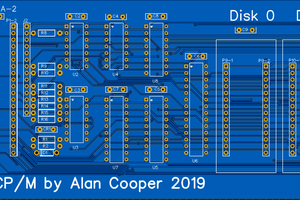

agp.cooper

agp.cooper

slederer

slederer