MIKBUG was the classic Motorola ROM for the MC6800 CPU. Engineering Note 100 has the original source code. The downside of the original code is that it used bit-banging of a Parallel port for serial I/O.

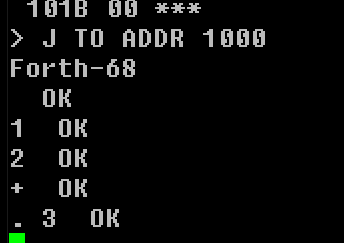

There is some recent work on MIKBUG. Mike Lee has a MC6802 build which has a MC6850 ACIA (UART) instead of the parallel I/O port. This fits nicely with Multicomp which provides two versions of the ACIA. One of the versions is brought to a serial port. The other implements the UART as a VGA output with PS/2 keyboard. This allows the FPGA card to emulate an external terminal without extra hardware.

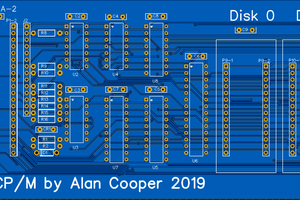

Mike Lee's board has the following hardware:

- MC6802 CPU

- SRAM at $0000-$7FFF (32KB)

- EPROM at $F000-$FFFF (4KB)

- (2) MC6821 Dual 8-bit Parallel I/O devices for 32 bits of I/O at $8000/1 and $8008/9

- MC6850 ACIA at $8018/9

Mike has source code for the SMITHBUGS version of MIKBUG which uses the ACIA for I/O. The code has defines for the PIA but doesn't have any initialization code so it should be possible to build the FPGA without including PIA hardware.

SmithBug is fairly small and only uses space from $C000-$C8FF. The "Operating System" scratch space RAM is at $7F00-$7FFF so there will need to be RAM at the top of the 32KB SRAM range - should be no problem for the EP4CE15 FPGA.

Our Implementation

We relocated SmithBug to $F000-$FFFF and opened an I/O space from $FC00-$FCFF for the built-in Video Display Unit (ANSI terminal) and ACIA (Serial Port). That leaves a potential for 60KB of SRAM (if the card has enough SRAM) and plenty of other I/O.

land-boards.com

land-boards.com

Bruce Land

Bruce Land

Alex Bowen

Alex Bowen

ziggurat29

ziggurat29

agp.cooper

agp.cooper