The new netlist probe algo has a better inherent sensitivity to driver conflicts, which should not occur in normal netlists but VHDL usually favors the std_logic type, which is a resolved version of std_ulogic that has less adoption despite its inherent ability to detect these driver conflicts.

The netlist probe detects a conflict because a resolved value is "likely" to differ from a valid signal signature. To ensure some margin, the signature is given by a simple polynomial using the driver's number : a multiplier and an offset, both of which are primes.

-- The polynomial parameters: shared variable Poly_factor : integer := 13; shared variable Poly_offset : integer := 5; -- Ideally, choose both as prime numbers, and the -- offset MUST be less than the factor (one half is good). -- The compromise is between execution speed (each -- factor of 8 adds another probe cycles) and -- error discrimination (fewer chances of coincidence).

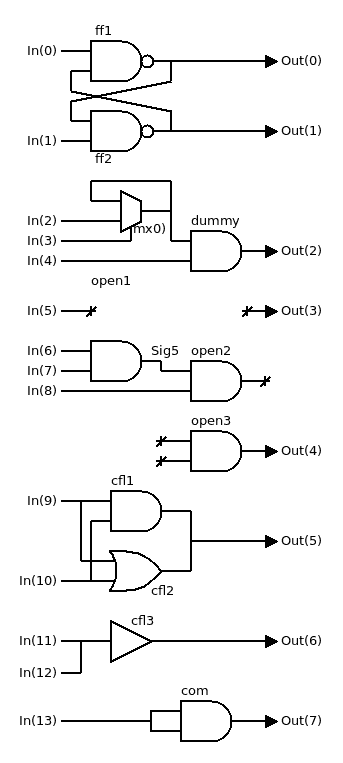

I have enabled the test of this features in test4_cornercases:

The gates clf1, cfl2 and cfl3 detect a driver conflict on an output port and a gate input. But it didn't work immediately: this depends on the polynomial factors, and some (which ?) will work and others not. 17-7 didn't work for this test, but 13-5 did, YMWV.

At first glance, the chance of detection will increase with the poly factor, but this also increases the number (and runtime) of the probe.

- If you are sure there is no conflict, use 1-0 to save time, particularly for huge netlists.

- 7-3 adds 1 probe cycle

- 61-23 will add 2 probe cycles

- 499-257 will add 3 probe cycles (new safe default)

- You could run the probe several times with various factors but it is more efficient to use larger factors. Help yourself.

Those values should be configurable with a generic one day.

The first version of the netlist probe was also able to identify the drivers of a conflict, now it's only possible to show the sink, but at least it's faster.

Each driver conflict is counted as an unconnected input and will abort the probe. It wouldn't make sense otherwise. Floating nodes are handled inside the gates.

Yann Guidon / YGDES

Yann Guidon / YGDES

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.