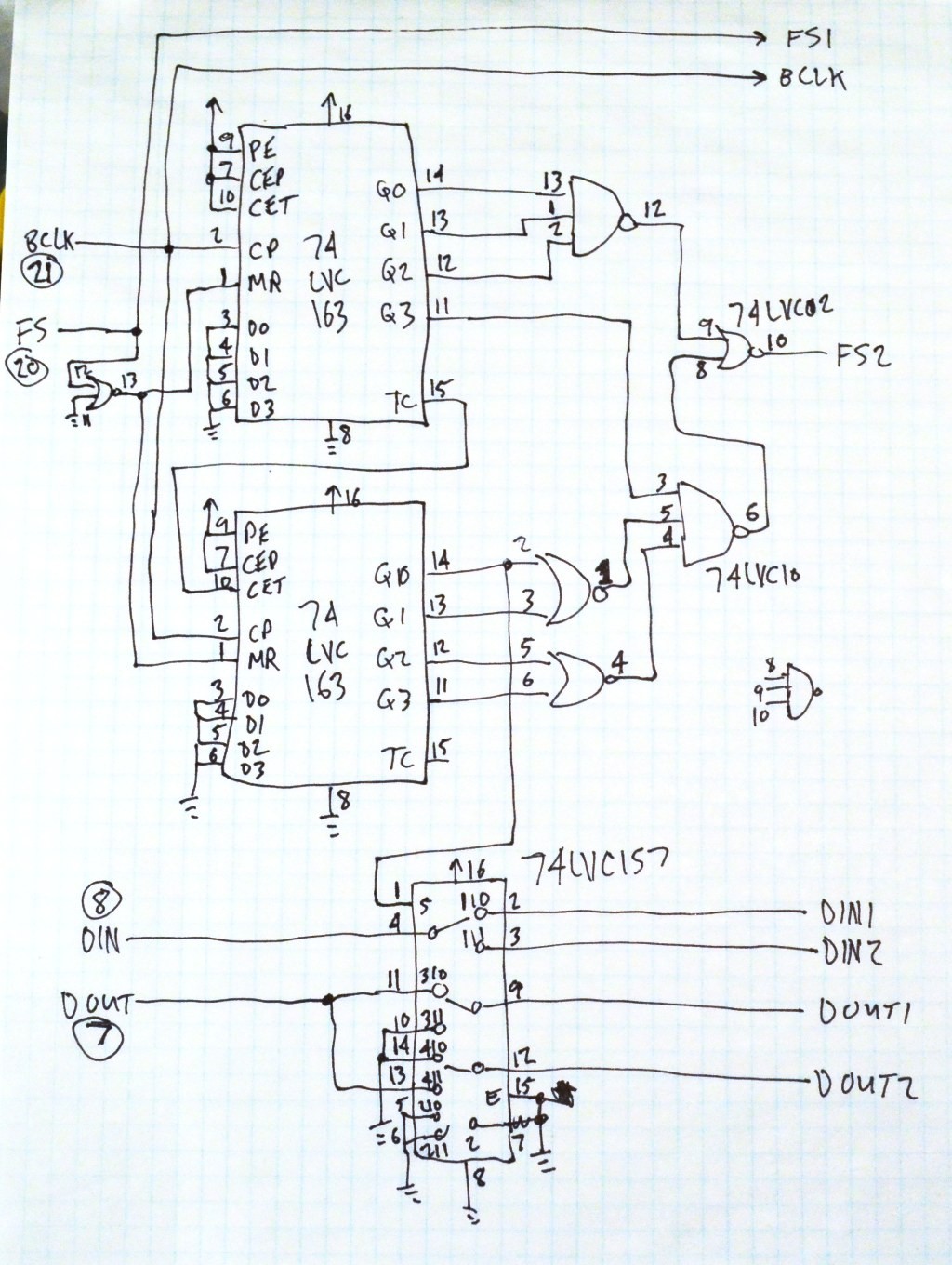

In the spirit of trying to share as I go, here's my first idea of how this state machine might work.

The basic idea is those 74LVC163 chips are connected to form an 8 bit counter, which gets reset when the FS signal is asserted.

The 2:1 mux chip routes the output from one of the CS42448 chips to Teensy every 16 cycles, and it sends Teensy's output alternately to the 2 chips in each 16 cycles.

Those NAND and NOR gates are supposed to generate a logic high when the counter is at 00001111, and logic low for all other states. I didn't simulate or test this at all... just made it up and doodled it on this graph paper. It's completely untested!

Paul Stoffregen

Paul Stoffregen

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.