Overview

The simplistic circuits shown in old books for driving step motors work fine at very low step rates. When the step rates start to increase, the motor torque output falls off very quickly. There are two reasons for this:

1) Motor back EMF generation.

2) Motor winding inductance.

Back EMF is a "feature" seen in most DC motors and step motors. When the coils move through a magnetic field, they generate a voltage. In the case of step motors, the magnetic field moves and the coils are stationary. The polarity of the generated voltage is opposite the polarity that would be required to drive the motor in that direction. The result of this is that the net voltage across the coils is the input voltage - the back emf voltage. The faster the motor turns, the less voltage availible to the coils.

Motor winding inductance is just the physics of the motor construction. The number of turns in the coils of wire and the magnetic structure of the motor set the inductance. Inductance opposes changes of current. Skipping the calculus, assuming that the drive voltage is constant, the current rises at a fixed rate. As the step rate increases, the amount of time for the current to rise in each step gets shorter so the motor current drops off. For a step motor, the net voltage across the coil does not stay constant as the speed goes up, the net voltage across the coil drops from the back EMF generated.

Raising the input voltage will overcome both of these problems, at the cost of creating one new problem. The new problem is that when the motor is stopped or moving slowly, the higher voltage across the coils will drive too much current and the motor will heat up rapidly. The solution to this problem is to regulate the current into the motor.

The inductance of the motor makes it fairly easy to regulate the current. When a voltage is applied across an inductor, the current rises linearly with time. If you measure the current flow and turn off the voltage when the current rises to the desired level, the average current is pretty well controlled.. The rest of the step motor driver system already supports switching the voltage on and off to each coil rapidly, so all that is needed to regulate the current is to install a low value resistor between the transistors on the low side and ground, and a comparator to sense the voltage across that resistor. The resulting circuit is called a chopper drive circuit because of the on/off action of the current regulation.

When the current rises to the desired value and the comparator switches off the voltage supply to the coil, the current already flowing circulates through the motor coil and the diodes protecting the transistors. These diodes may be internal to the transistors in the case of MOSFETs or external. It is not uncommon to use external diodes to help the internal diodes (called body diodes) on MOSFETS because the body diodes tend to not be great diodes. In operation, the current circulating takes a while to decay, so it does not drop to zero instantly when the supply transistor switches off. When the current drops below the set value, the supply side transistor turns back on. The current cycles above and below the desired value fairly closely.

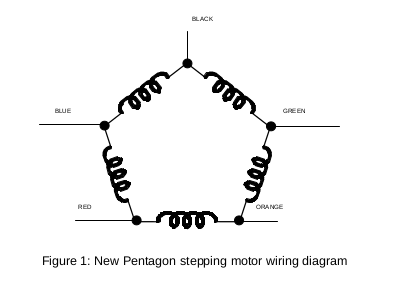

As mentioned in the introduction, these motors are 5 phase motors. The drawing below shows the configuration of the windings (TM Oriental Motor)

None of the step motor driver chips that I saw will support this configuration other than the ones sold by Oriental Motor.

There is good documentation on the MPJA web site for the motors and drivers, so I designed the step generation logic in 74HC logic. When I was done, the implementation would have been at least 12 chips. After adding the power and gate drivers, this was starting to look like a medium sized 4 layer board which would be expensive. As a way to reduce board area, I found some little Xilinx CPLD (Complex Programmable Logic Device) parts that would be large enough for the step generation...

Read more » Bharbour

Bharbour

ottoragam

ottoragam

ridonkulus

ridonkulus