I just had a first successful test run in VHDL using w16. It's not finished but the result is almost as good as I expected.

[yg@Rizen5 PEACLS]$ ./runme.sh In=0000000000000000 X:010000000000000000 Out=0000000000000000 In=0000000000000000 X:011101110101101101 Out=0000000000000000 In=0000100000000000 X:010111010111011011 Out=0000100000000000 In=0000000000000000 X:000100101101001001 Out=0000000000000000 In=0000000000000000 X:011100000100100101 Out=0000000000000000 In=0000000000000000 X:000000110001101110 Out=0000000000000000 In=0000000000000000 X:001100110110010100 Out=0000000000000000 In=0000000000000000 X:011101101000000010 Out=0000000000000000 In=0000000000000000 X:011010011110010110 Out=0000000000000000 In=0000000000000000 X:011000000110011001 Out=0000000000000000 In=0000000000000000 X:000010100100110000 Out=0000000000000000 In=0000000000000000 X:001010101011001010 Out=0000000000000000 In=0000000000000000 X:011101001111111010 Out=0000000000000000 In=0000000000000000 X:010111111011000100 Out=0000000000000000 In=0000000000010000 X:000101001011001111 Out=0000000000010000 In=0000000000000000 X:011101000110000100 Out=0000000000000000 In=0000000000000000 X:000010010001010011 Out=0000000000000000 In=0000000000000000 X:011111010111011000 Out=0000000000000000 In=0000000000000000 X:010001101000101011 Out=0000000000000000 In=0000000000000000 X:000001000000000100 Out=0000000000000000 In=0000000000000000 X:000010101000110000 Out=0000000000000000 In=0000000000000000 X:000011101000110100 Out=0000000000000000 In=0000000000000000 X:000110010001100100 Out=0000000000000000 In=0000000000000000 X:011001111010011000 Out=0000000000000000 In=0000000000000000 X:000000001011111100 Out=0000000000000000 In=0000000000000000 X:001010000110010101 Out=0000000000000000 In=0000000000000000 X:011010010010010001 Out=0000000000000000 In=0000000000000000 X:000100011000100110 Out=0000000000000000 In=0000000000000000 X:011110101010111000 Out=0000000000000000 In=0000000000000000 X:010011000011011110 Out=0000000000000000 In=0000000000000000 X:000001101110010111 Out=0000000000000000 In=0000000000000000 X:000100110001110110 Out=0000000000000000

I send 2 individual bits and the data on the line (X) is a nice mess. The output is exactly as expected however!

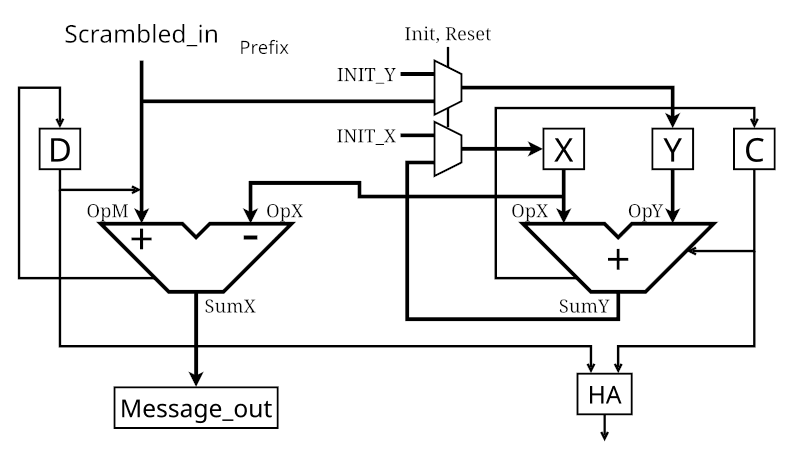

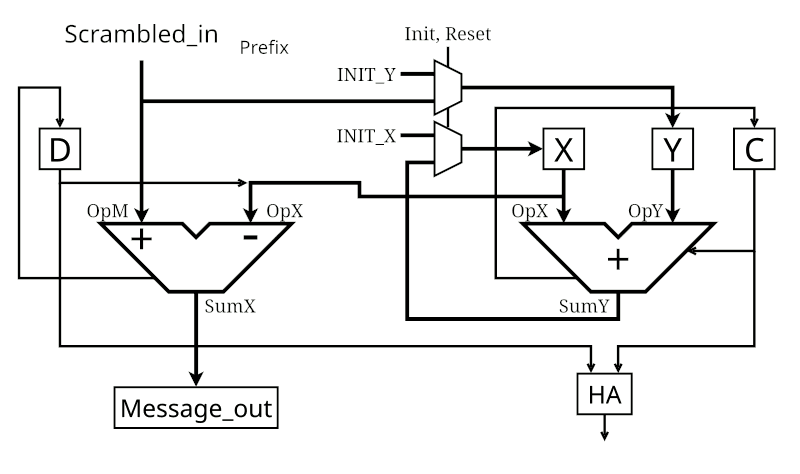

The "schematics" are almost straight out of 79. Taxonomy:

Encoder:

Decoder:

There is a slight delay due to pipelining/buffering so the output log above is "compressed".

I can play with the INIT_X and INIT_Y values, for now I use

INIT_X <= "0110110111011011"; INIT_Y <= "1101110101101101";

One thing I notice though is that the D bit is very dependent on the input message. When there is no input entropy, the prefix/HA output is either 00 or 01, barely ever 10. C seems to have a good behaviour but I need a way to toggle D more. Or even remove D...

.

.

.

But otherwise, so far it's a success, almost like expected.

.

_____________________________________________

.

I updated the "circuit" because the D should subtracted from the message, instead of added.

So this solves a "little problem" with the output that gets off-by-one in certain situations.

Get PEACLS_20241013.tgz !

The carries will give a lot of problems, for sure. The 2-bit prefix depends a LOT on the message's MSB, for example. But the XOR part is quite good.

Yann Guidon / YGDES

Yann Guidon / YGDES

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.