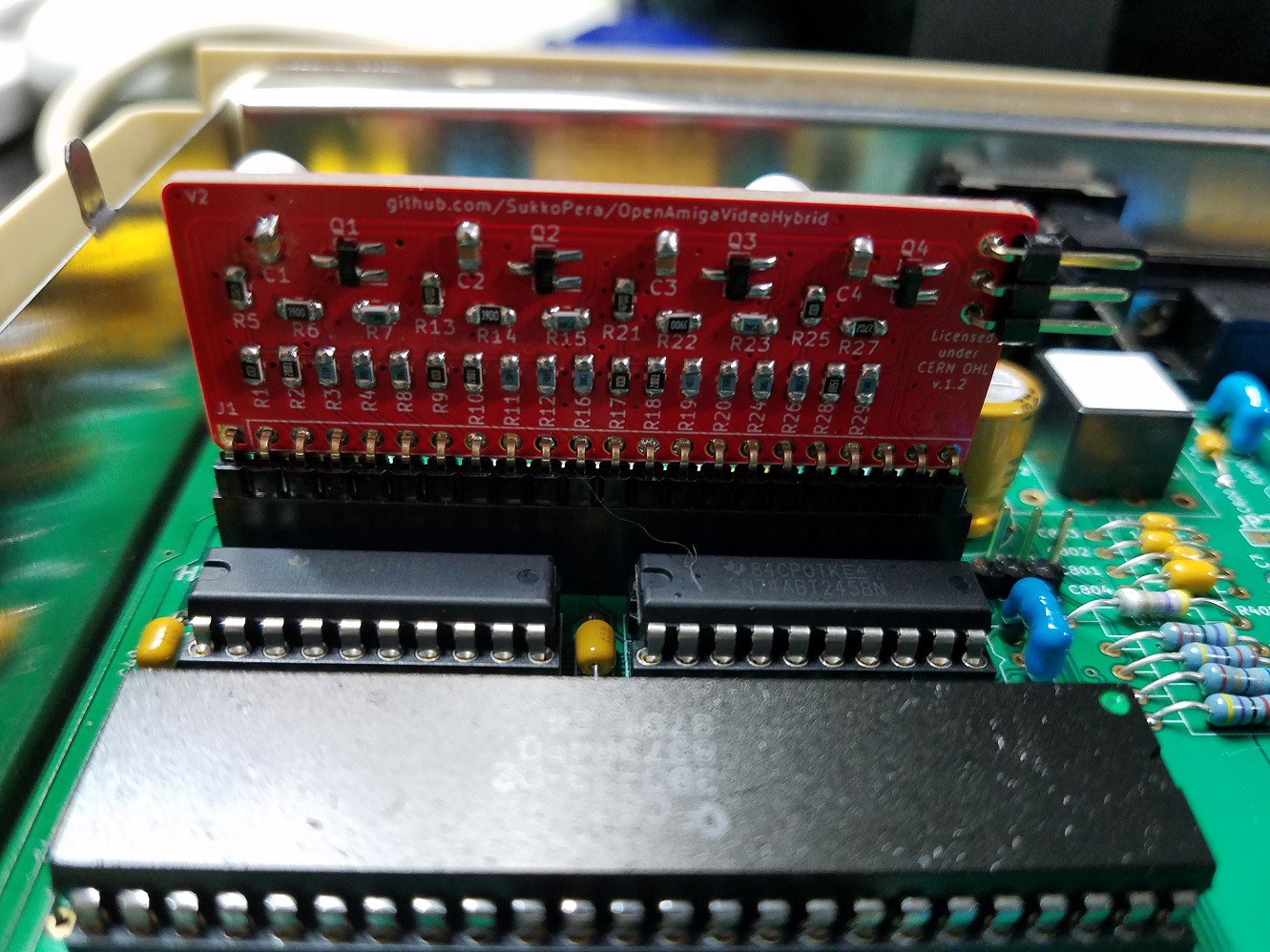

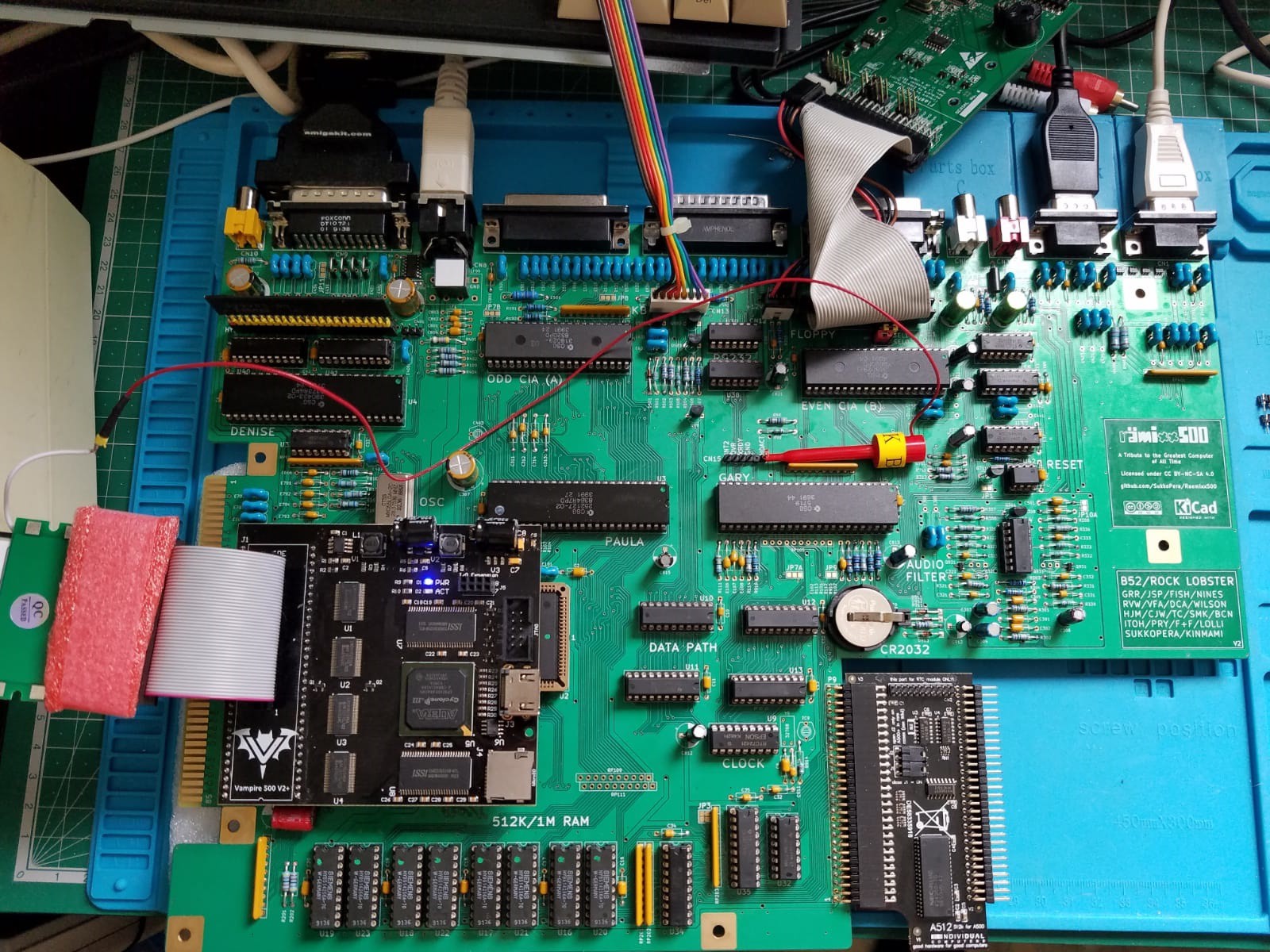

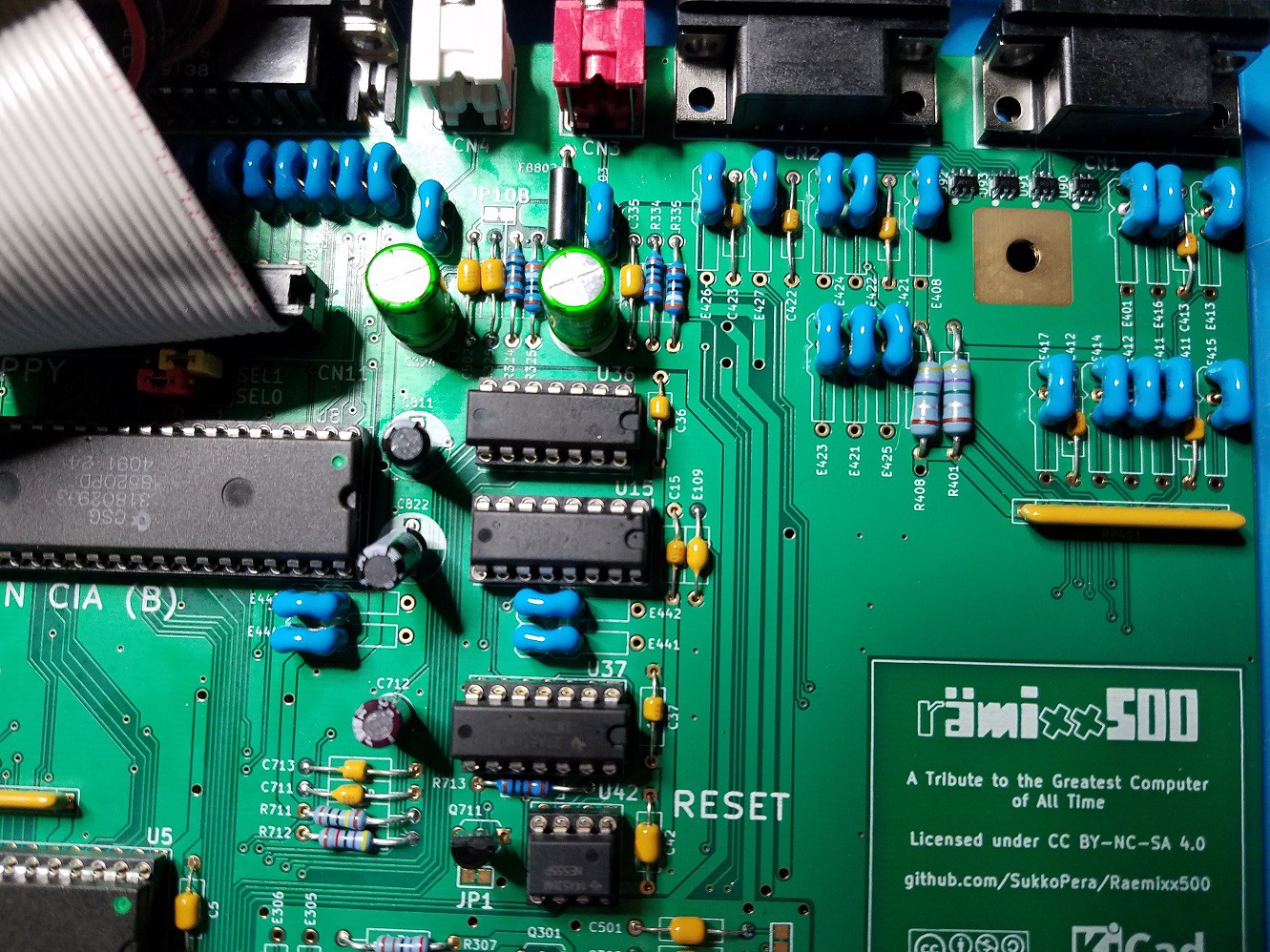

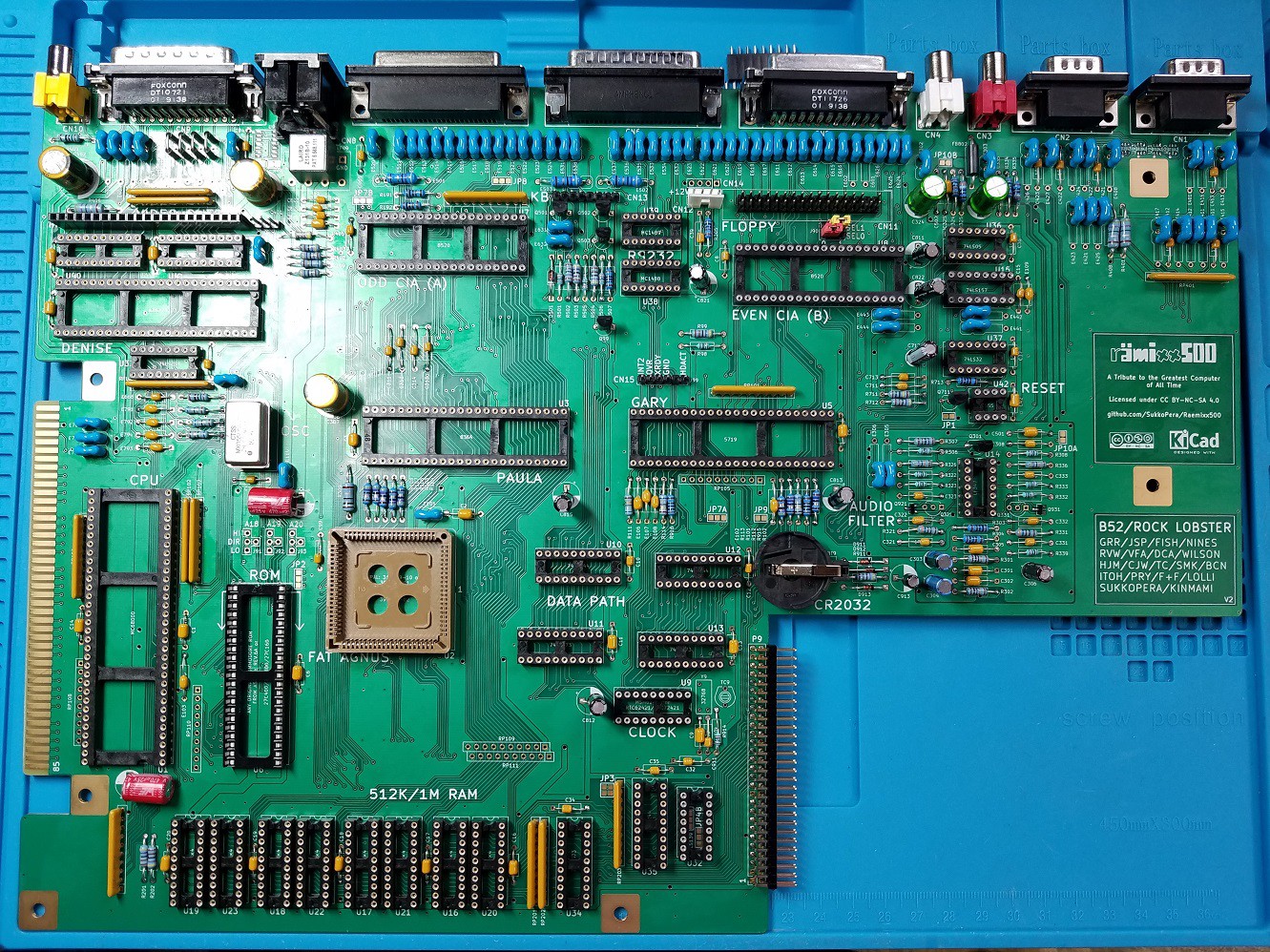

There are other projects like this one out there, but none of them is Open Source and none of them comes with both schematics and board. This is a big advantage, since anyone can modify the board and make new improved versions.

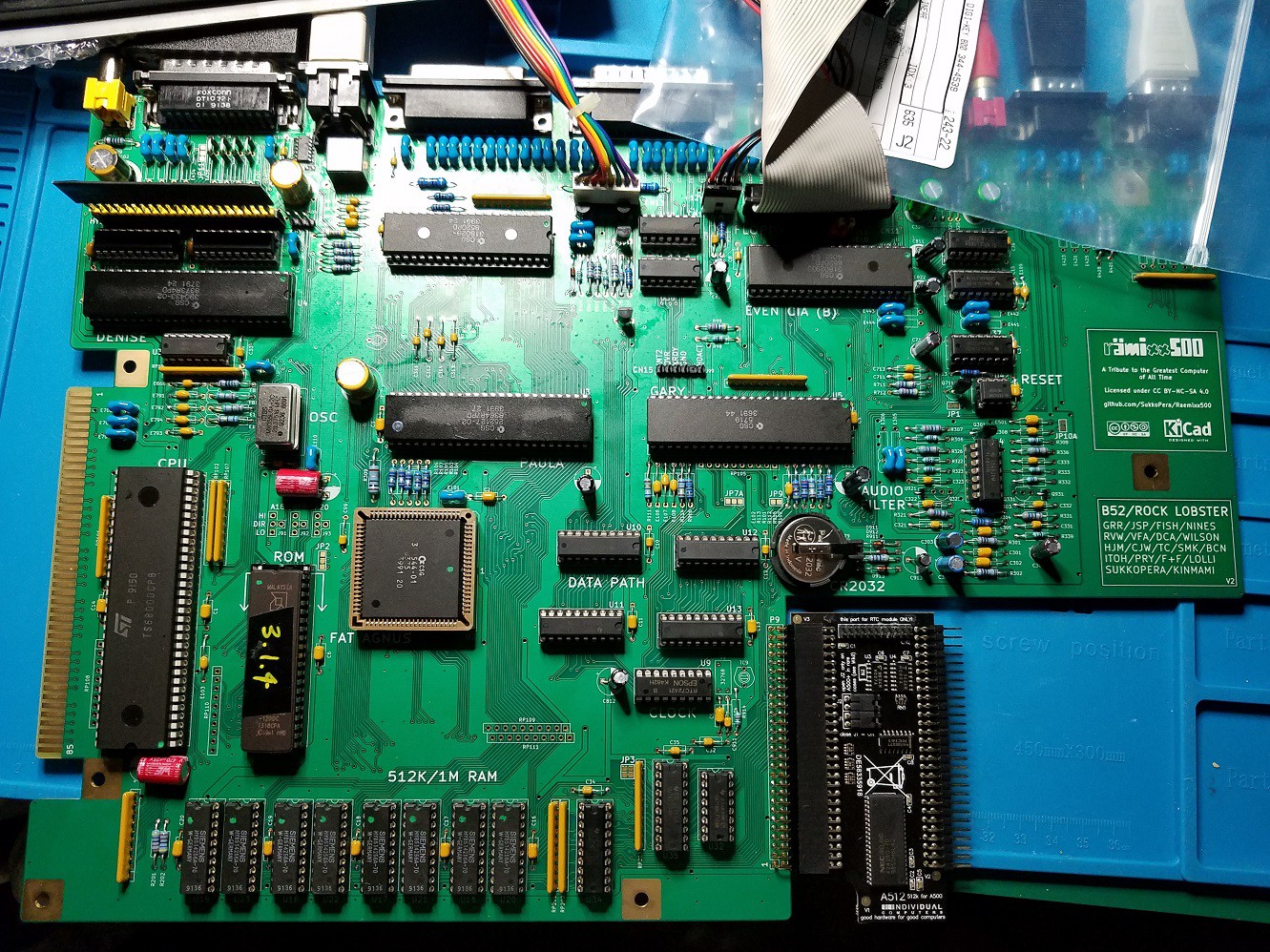

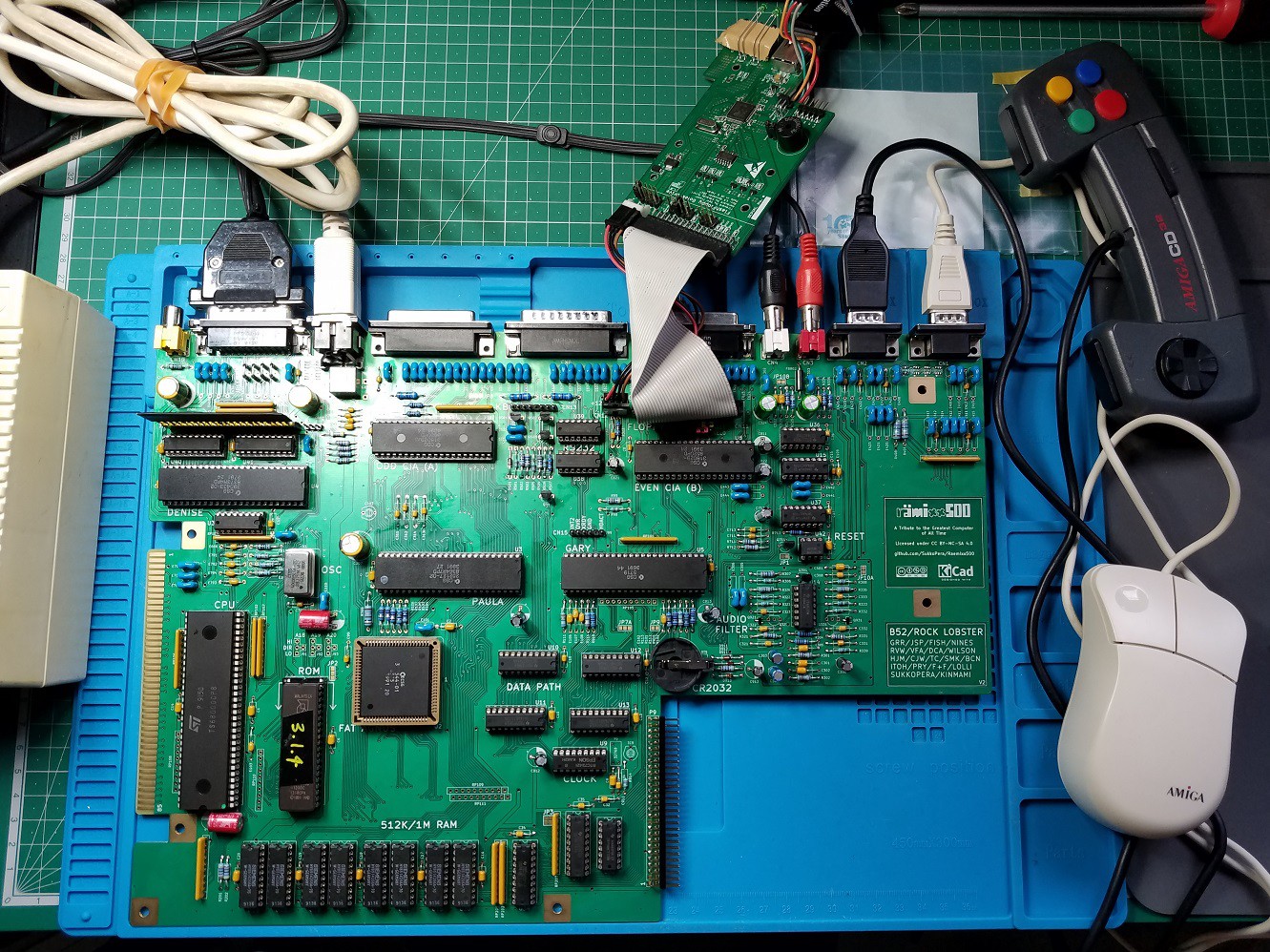

Rämixx500 - Amiga 500+ Mainboard

Open Hardware Remake of this Commodore Masterpiece

SukkoPera

SukkoPera

The Big One

The Big One

Thomas Baum

Thomas Baum

Anderson Antunes

Anderson Antunes

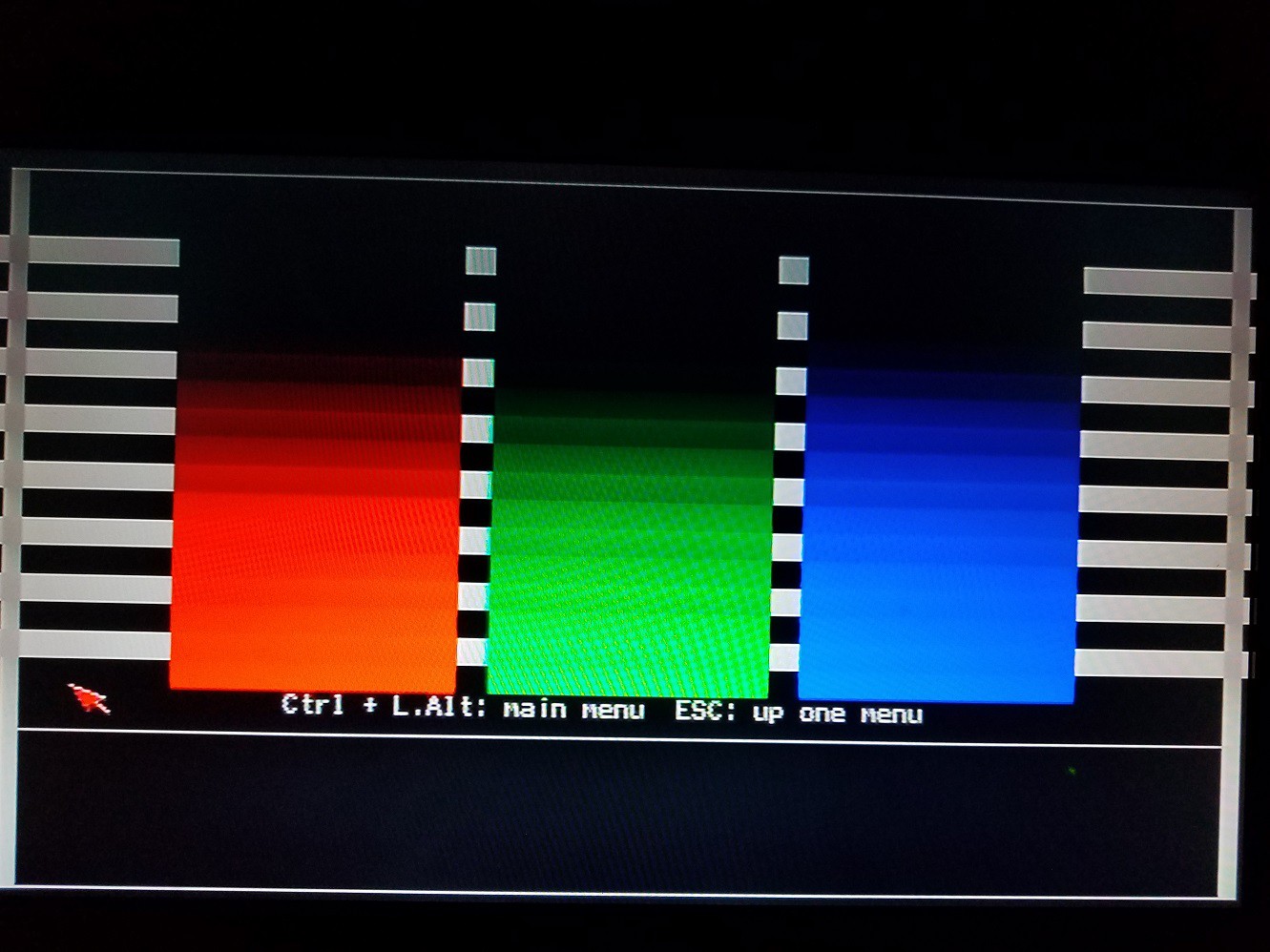

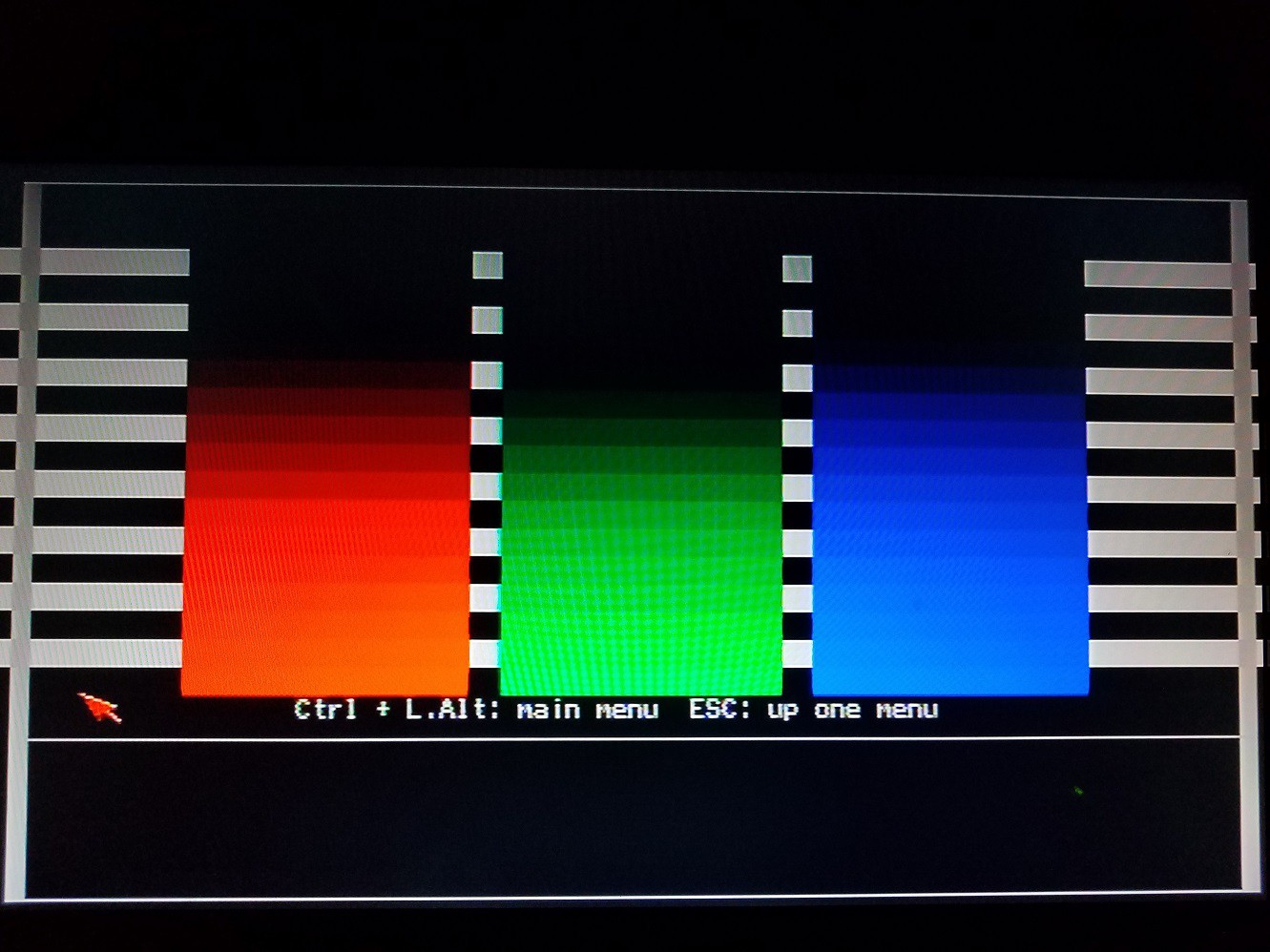

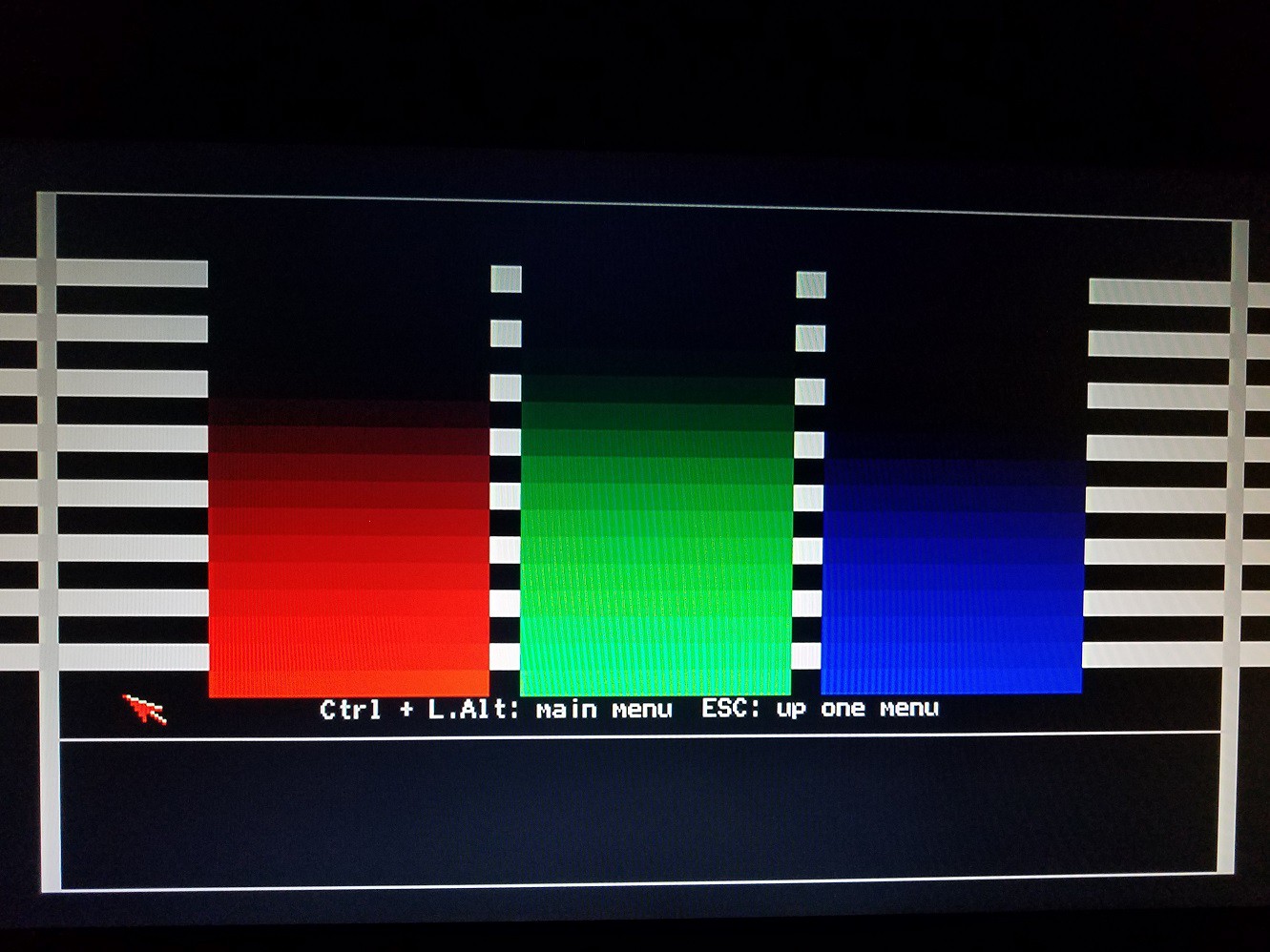

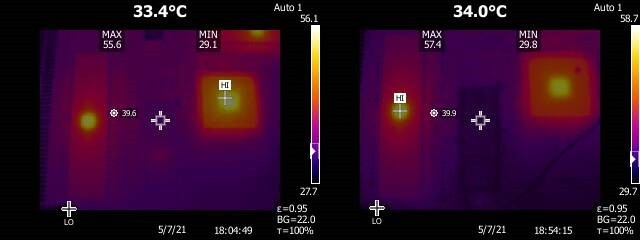

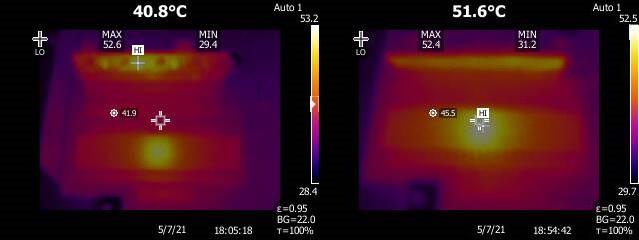

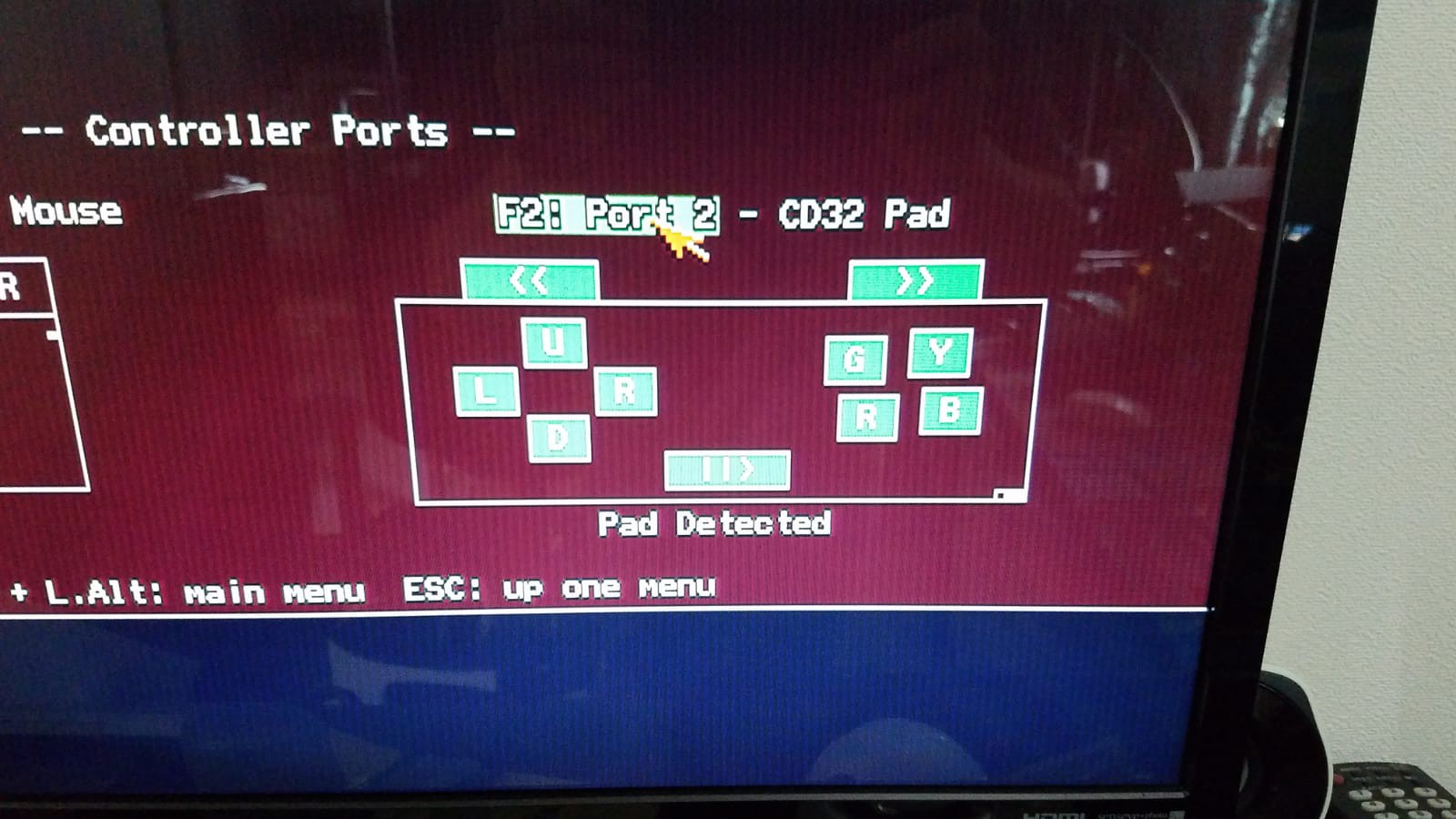

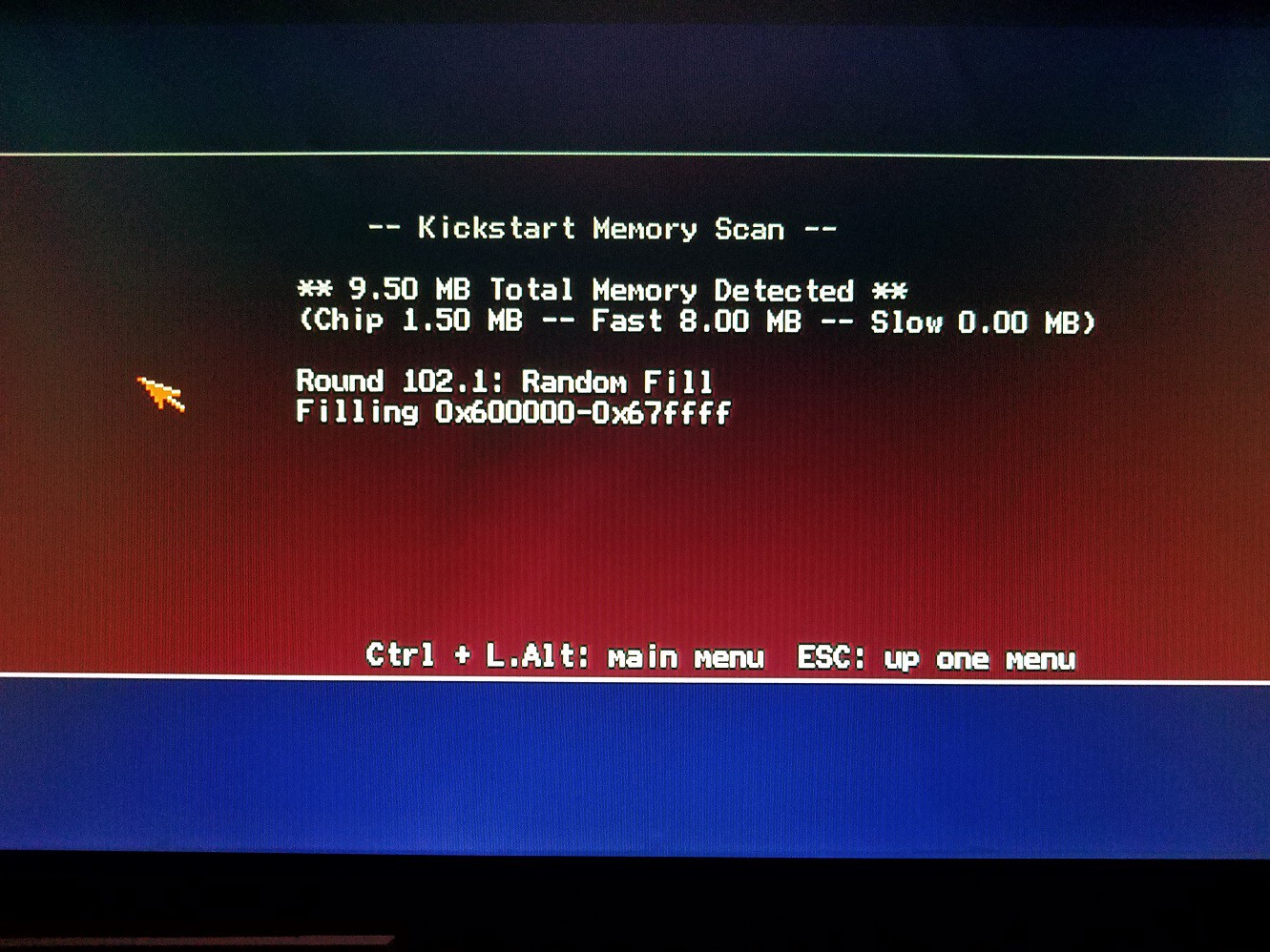

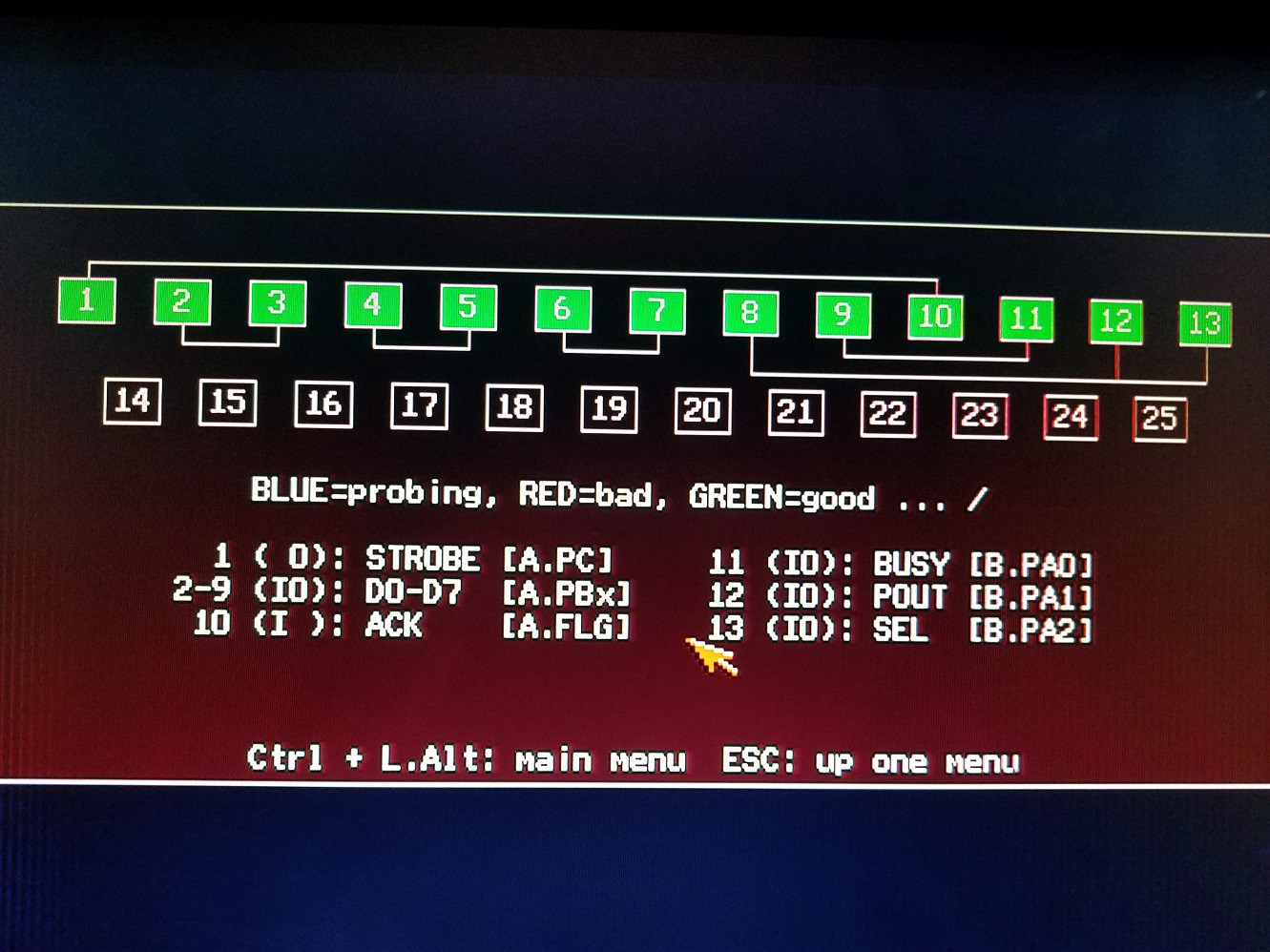

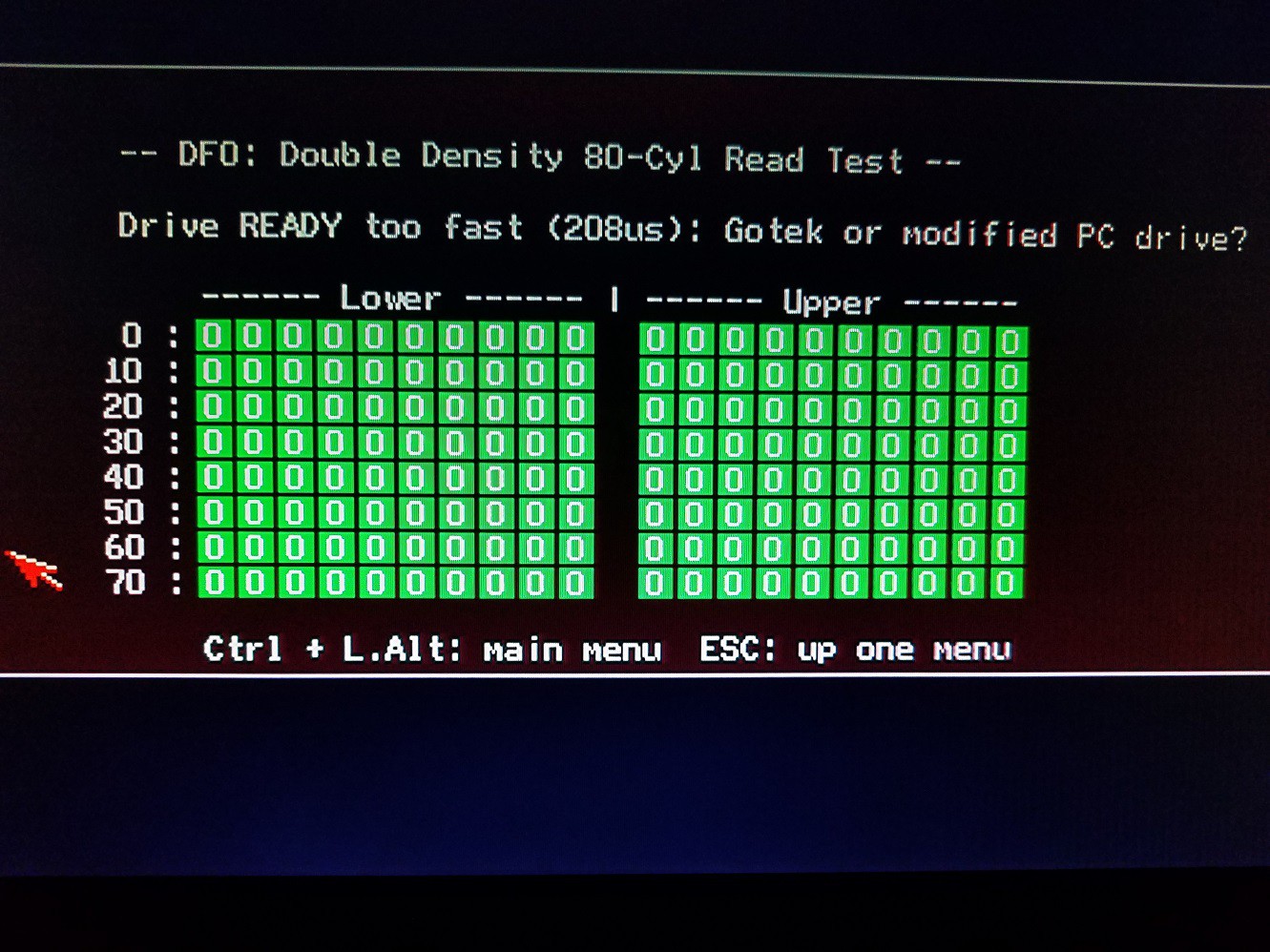

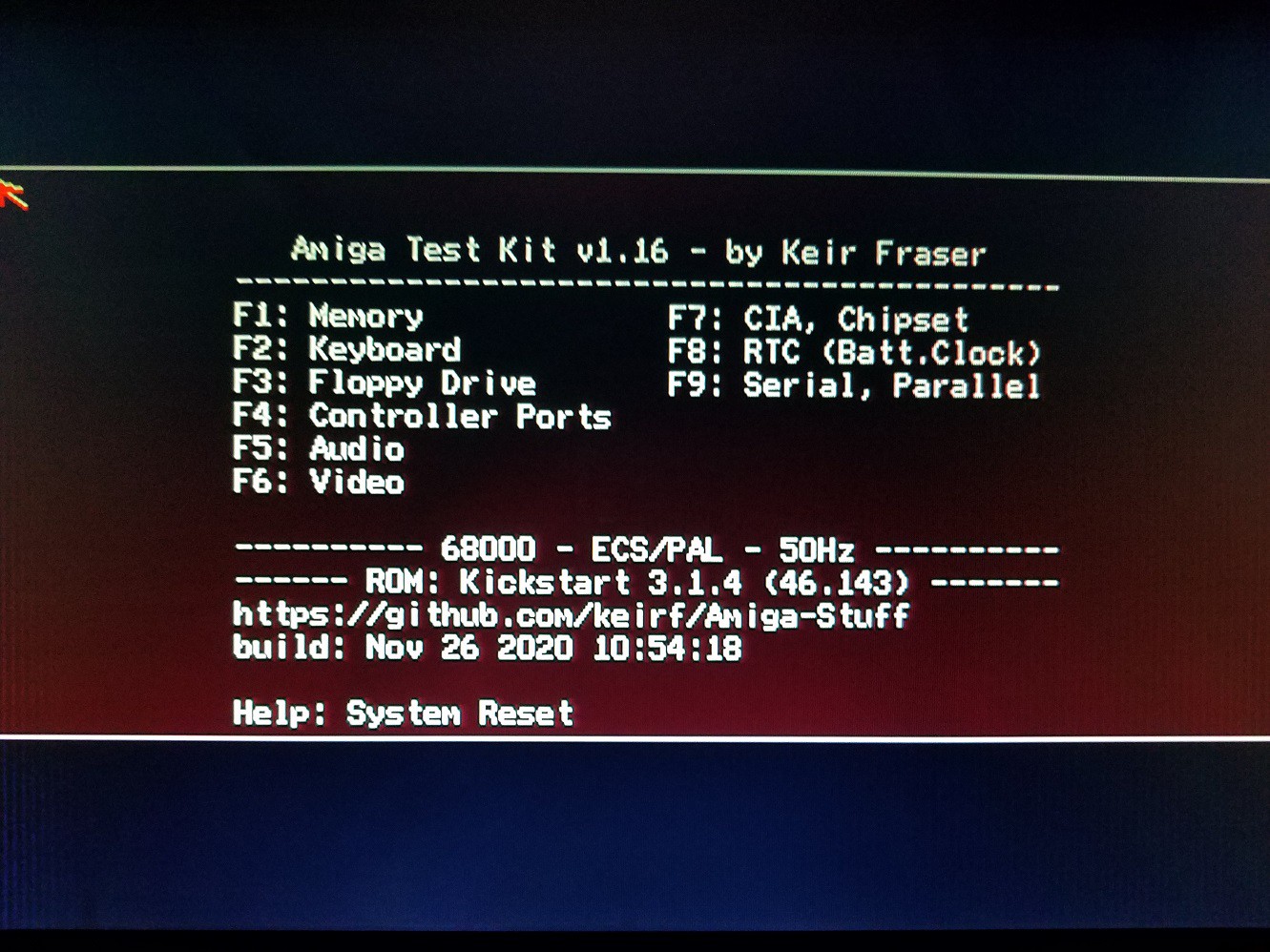

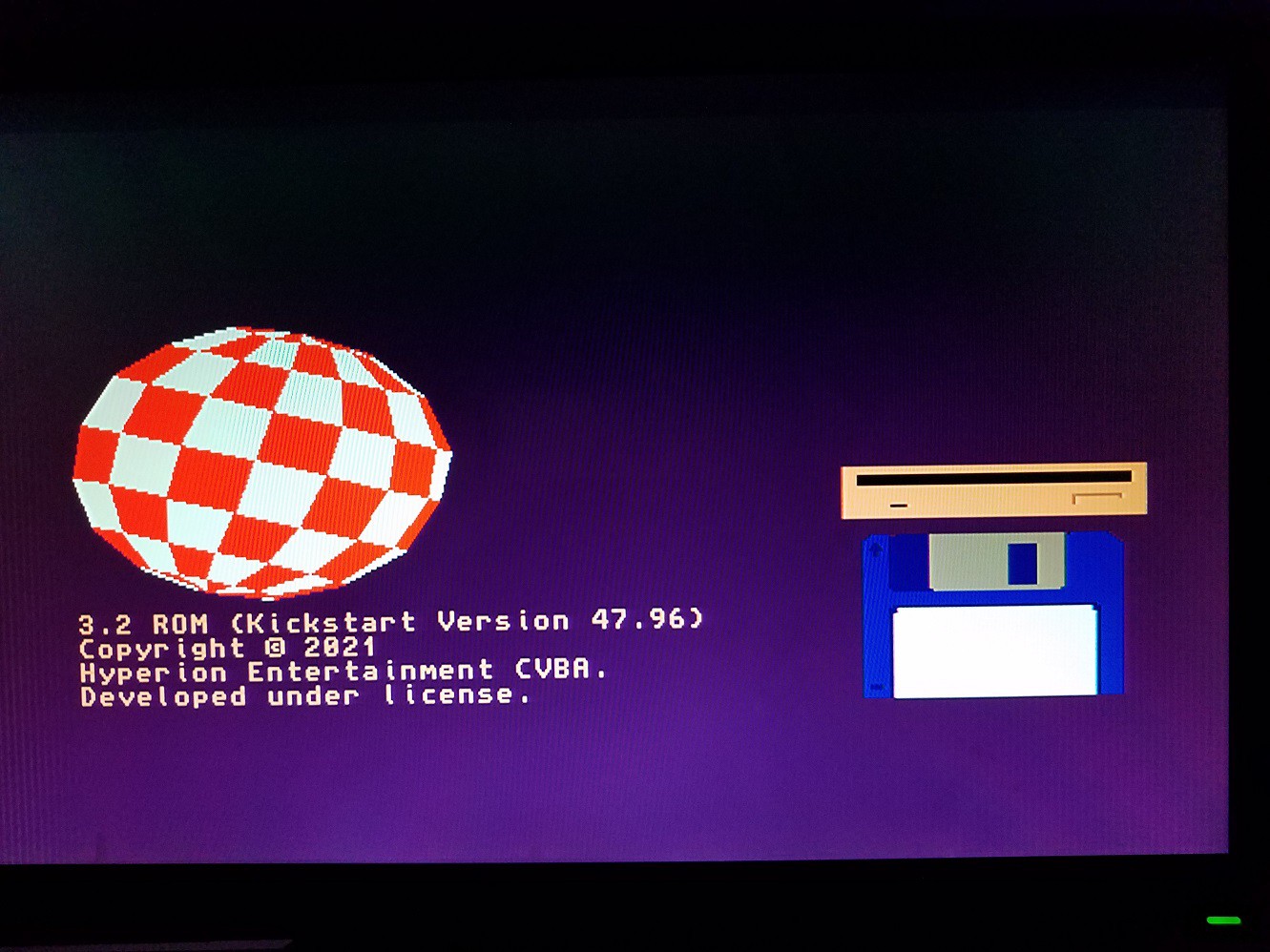

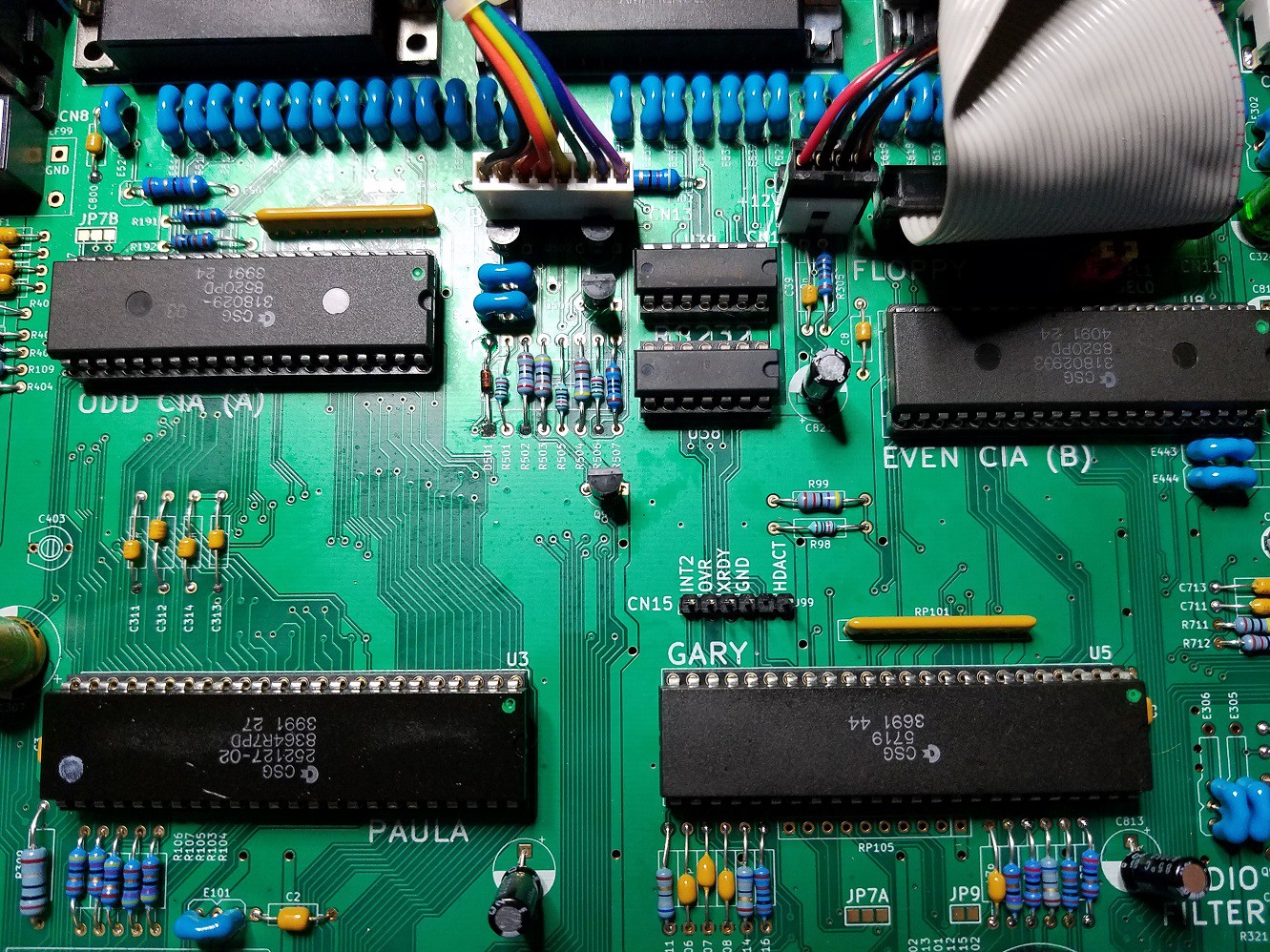

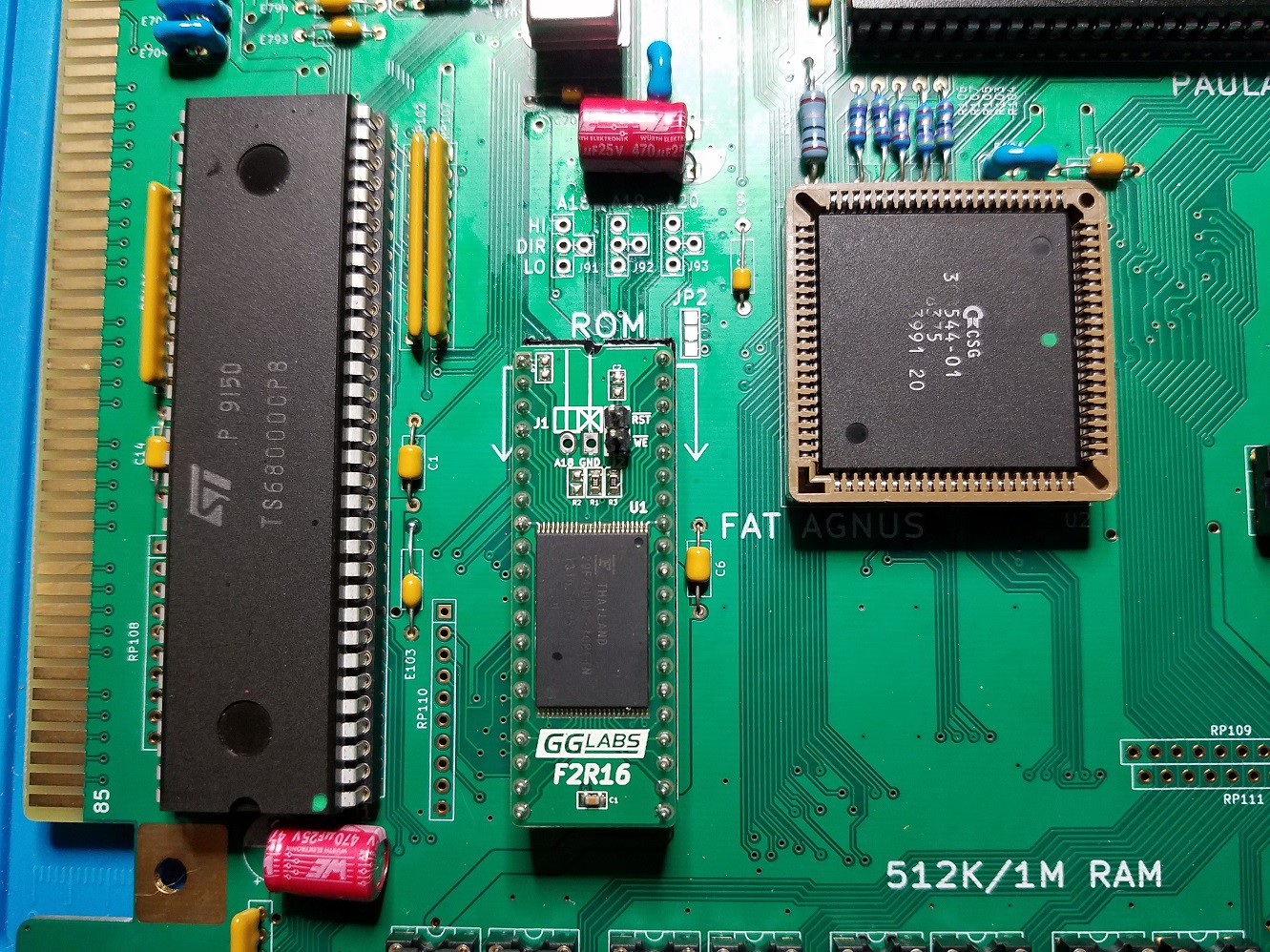

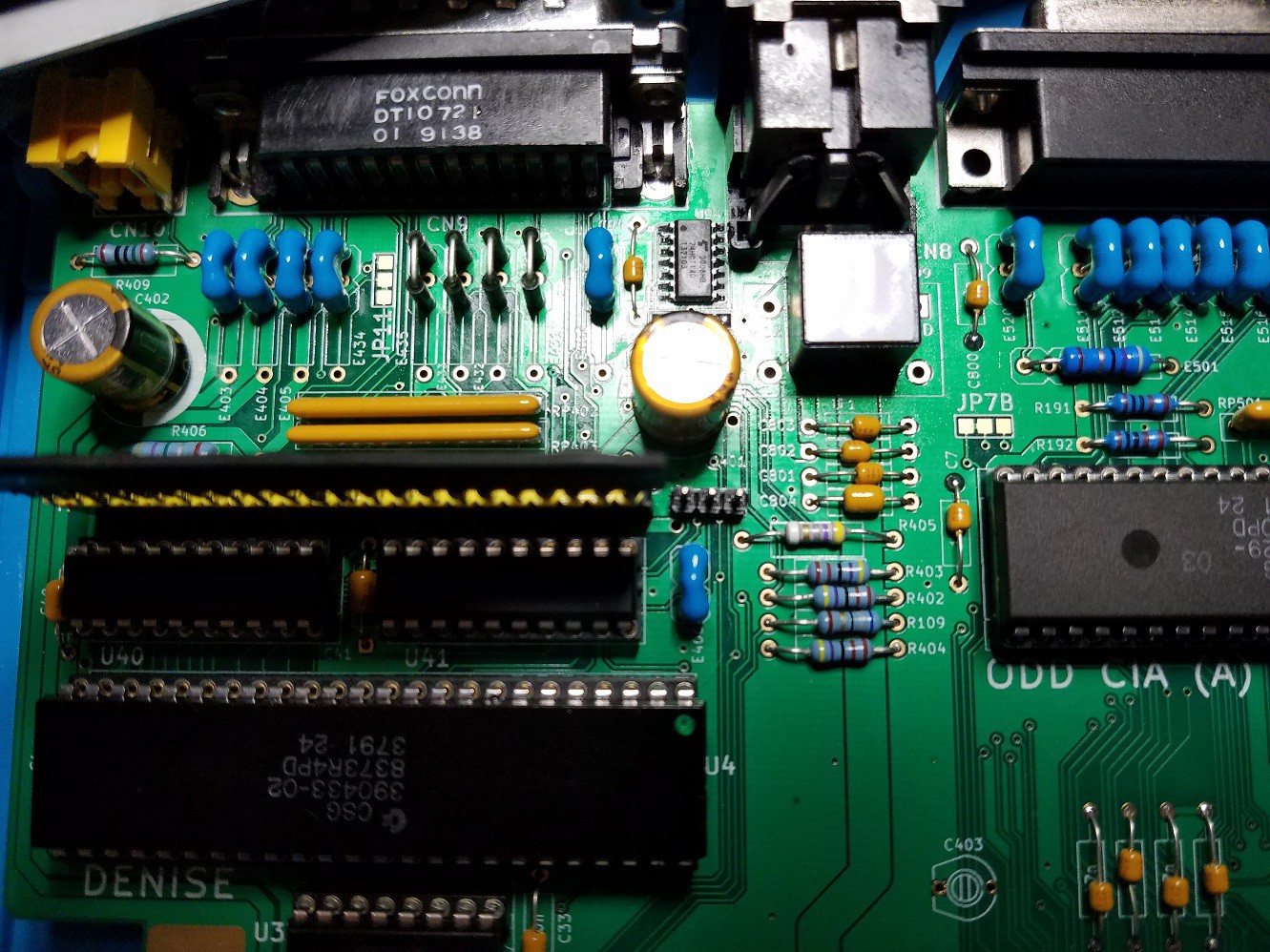

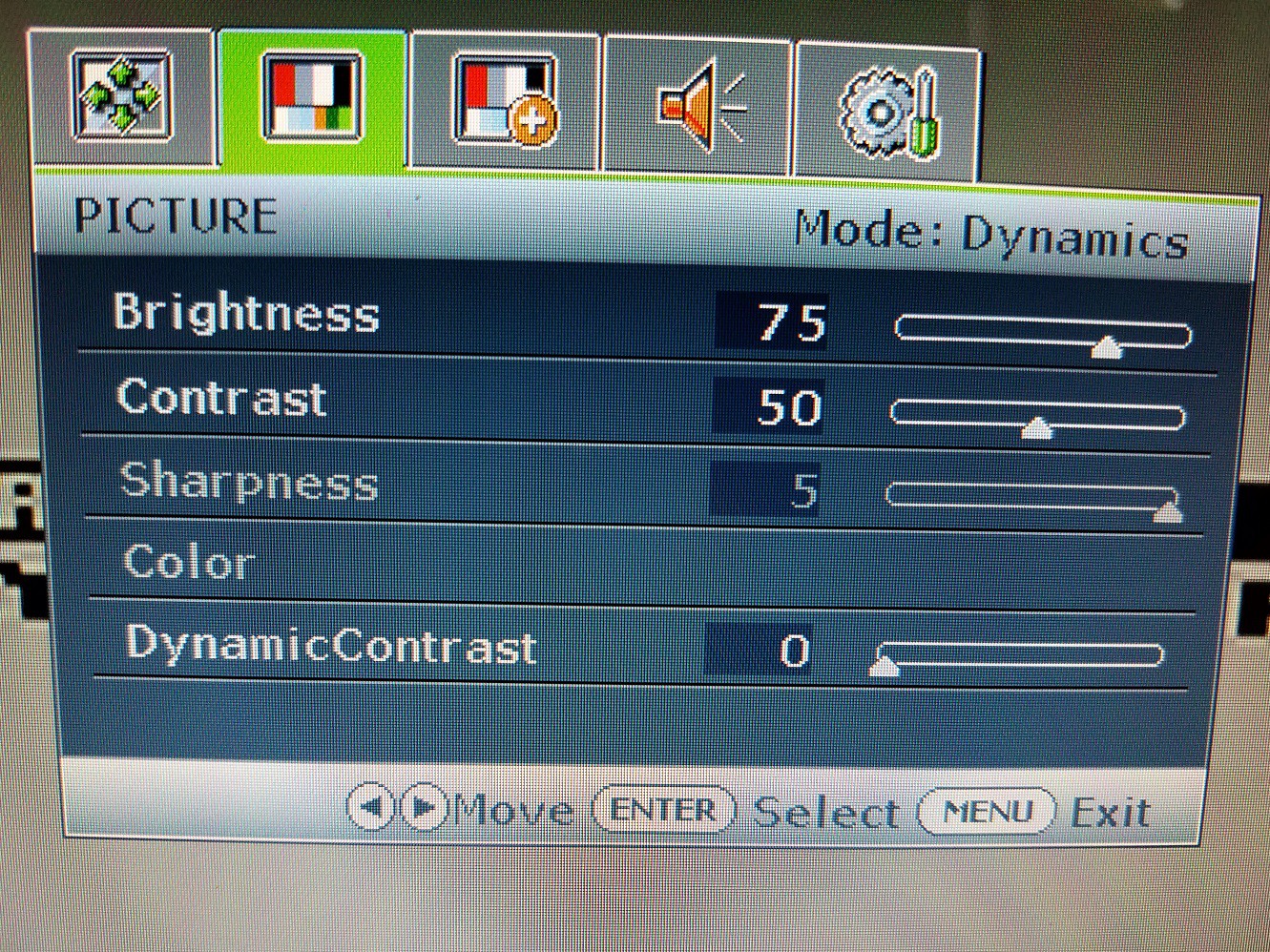

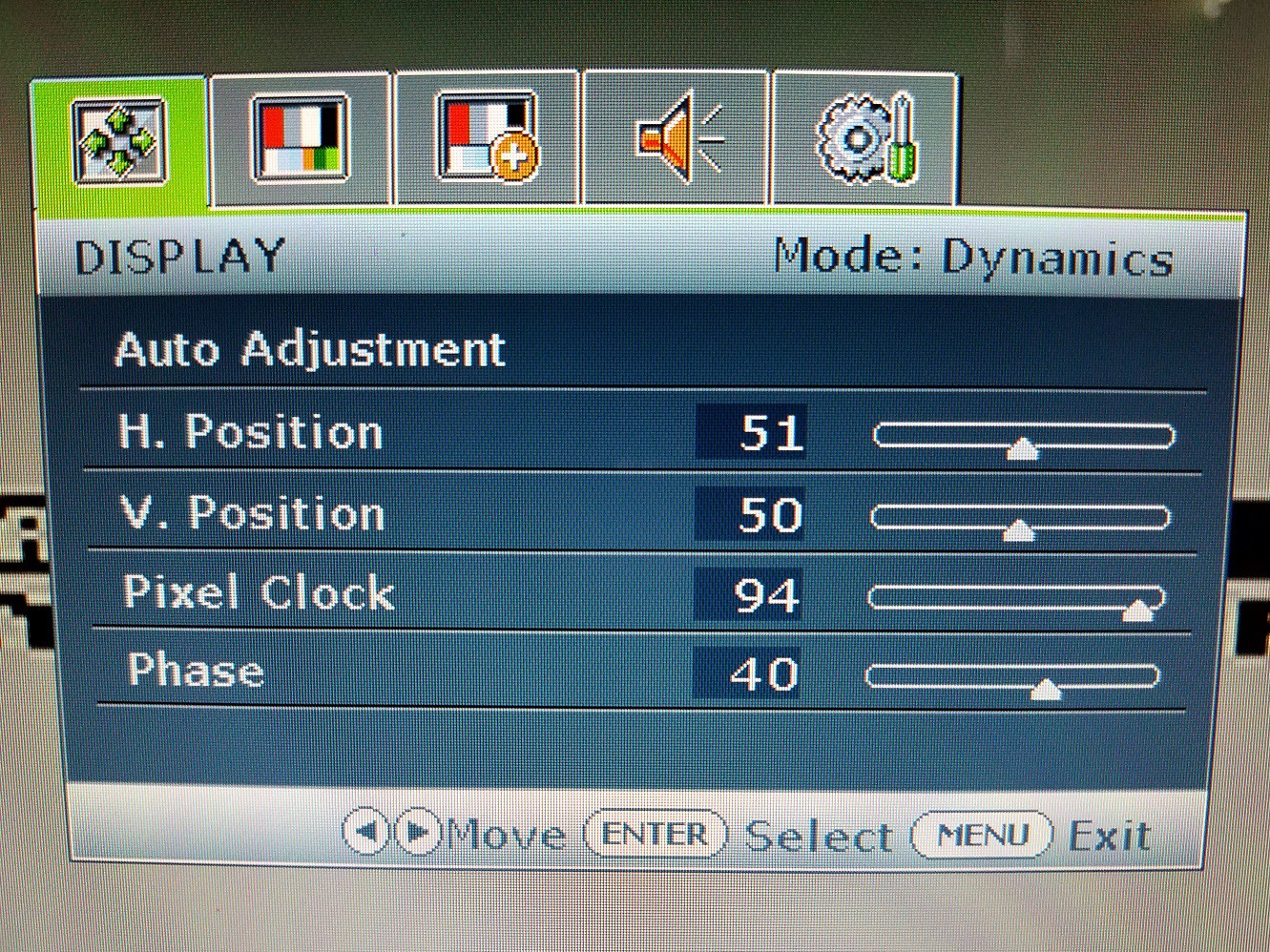

Just been building up a V2 board - finally after waiting months for components. Got a bit of an issue with it though. Anyone had any success or pointers before I get elbow deep in looking for errors