This is the worst part. DDR3 - it took me ages to get it right. So I'll put some notes here to help people.

The Arty DDR requires 2 clocks, a system clock and a reference clock:

.sys_clk_i(clock166), //166 mhz

.clk_ref_i(clock200), //200 mhz

One is 166 and the other is 200mhz.

The next is the DDR reset & enable. It is very picky.

reset_proc : process

begin

sys_resetn <= resetn and mem_ready and clk_locked;

rstn_flag <= '0', '1' after 220us; -- 200 & 750

cke_flag <= '0', '1' after 750us;

ddr3_reset_n <= '0' when rstn_flag = '0' else ddr_rstn;

ddr3_cke <= "0" when cke_flag = '0' else ddr_cke;

wait for 3us;

end process;

At power up the DDR must be held in reset for at least 200 micro seconds. Also the DDR enable flag must be held low for at least 750 micro seconds.

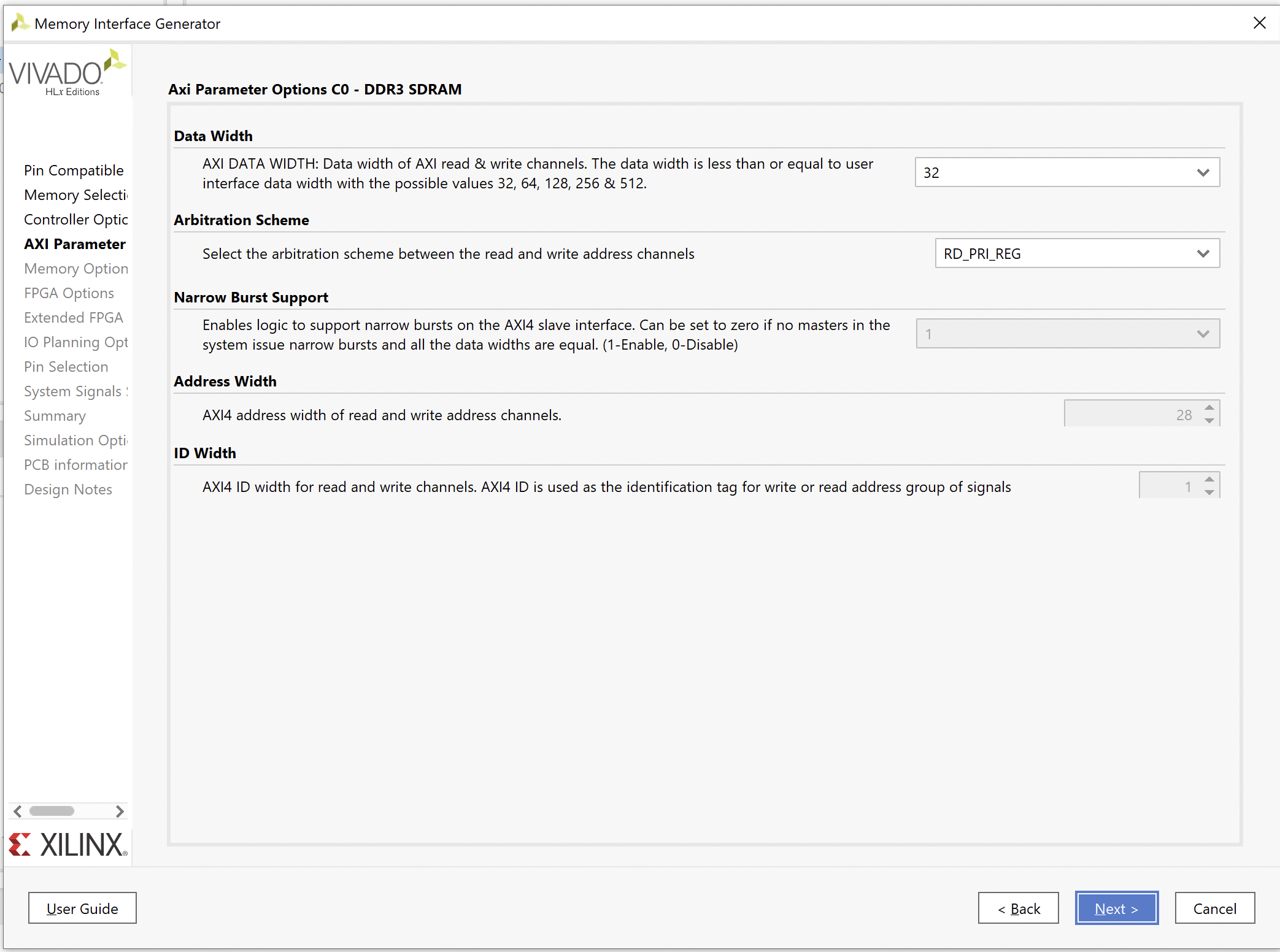

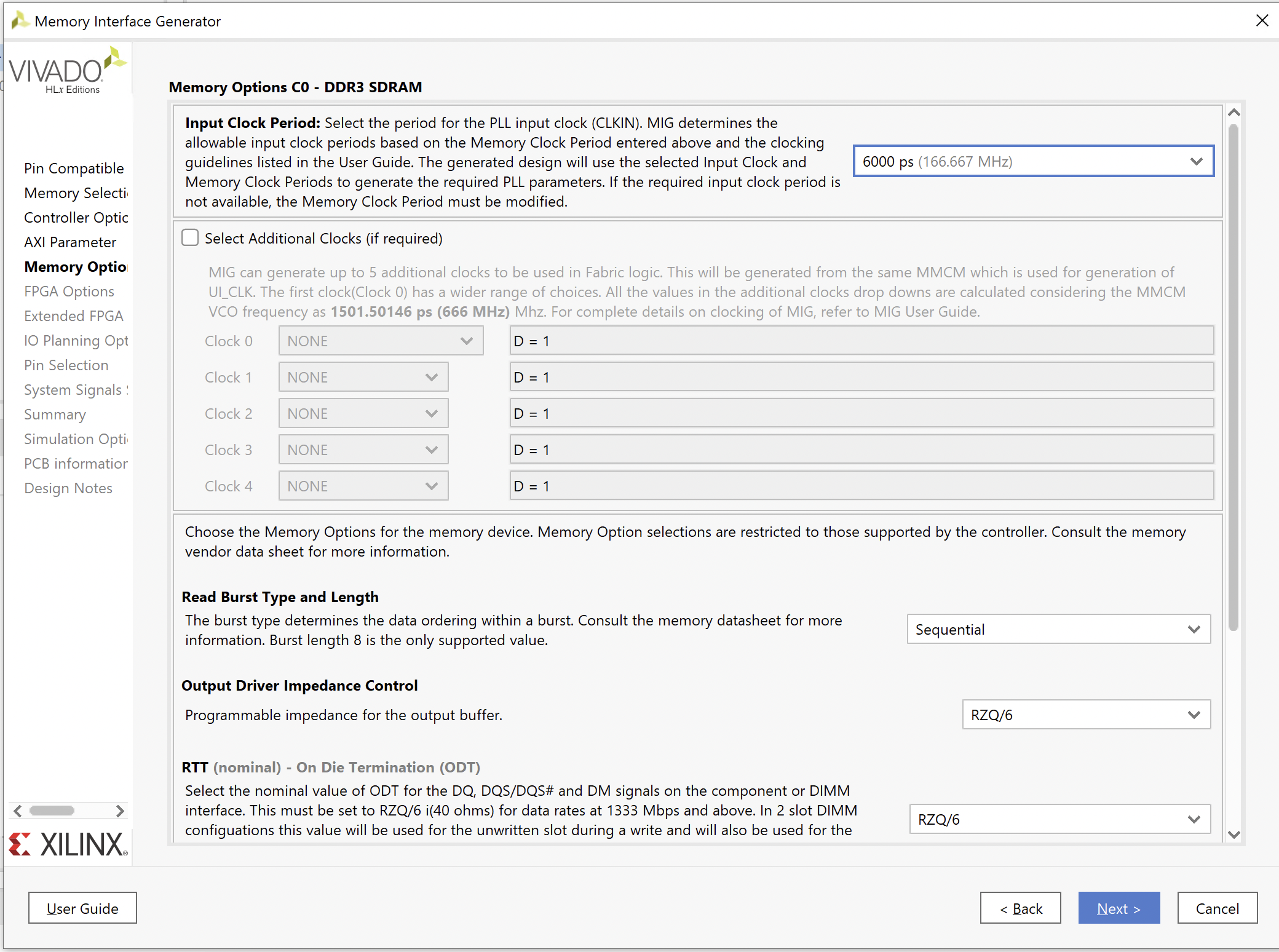

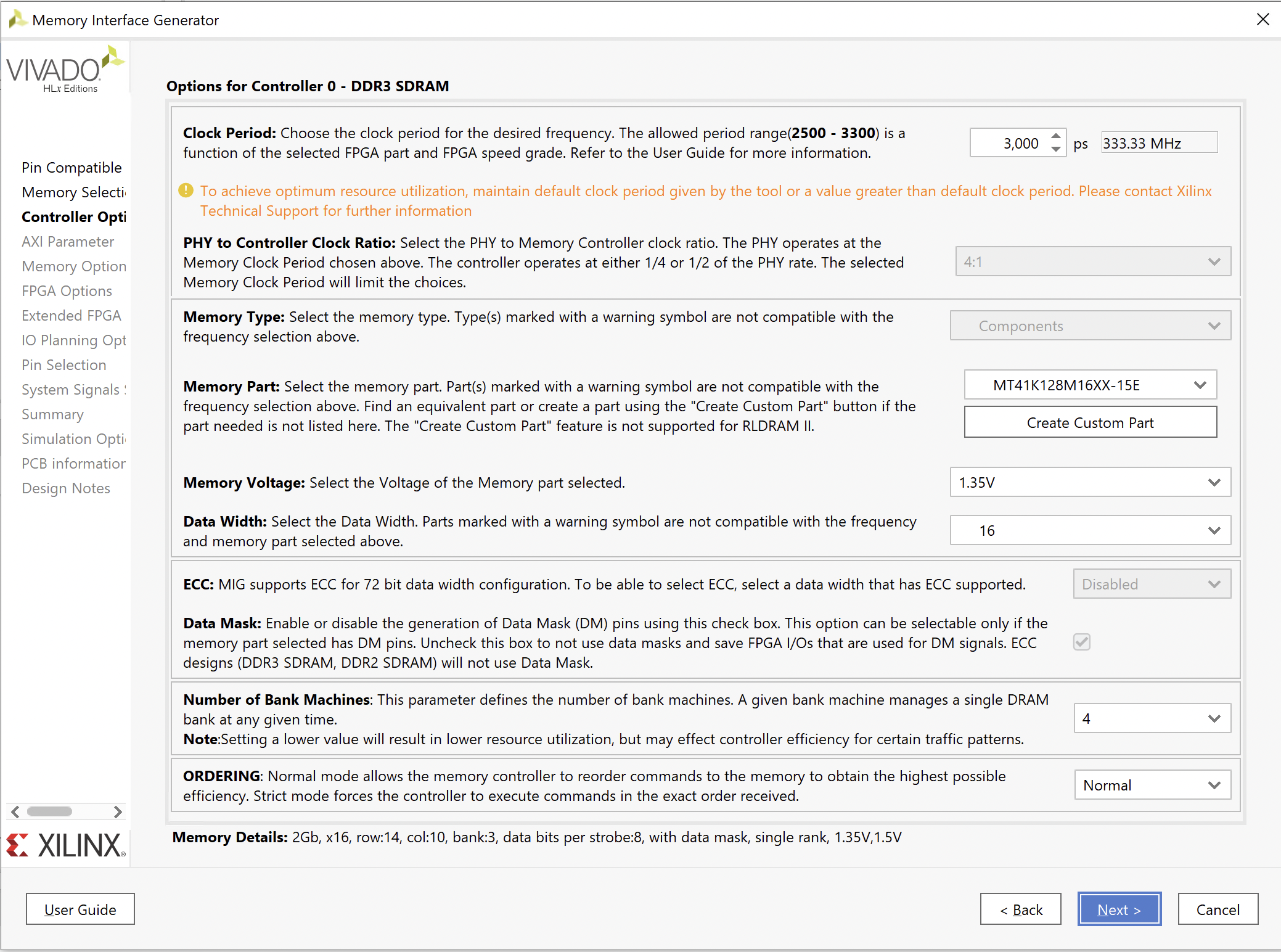

Next is the MIG IP set up. There are lots of fiddly settings here. The clocks must be set as per the images attached to this post. In the Merlin project there is a memory block design which shows all of the correct settings. The input clock period must be 166mhz. This will give you a UI clock of 83mhz, which is the fastest speed the arty ddr will run at. I get round this by using a system cache IP running at the CPU speed at 100mhz and then letting the axi interconnects deal with it from there.

Good Luck!

Matthew Pearce

Matthew Pearce

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.