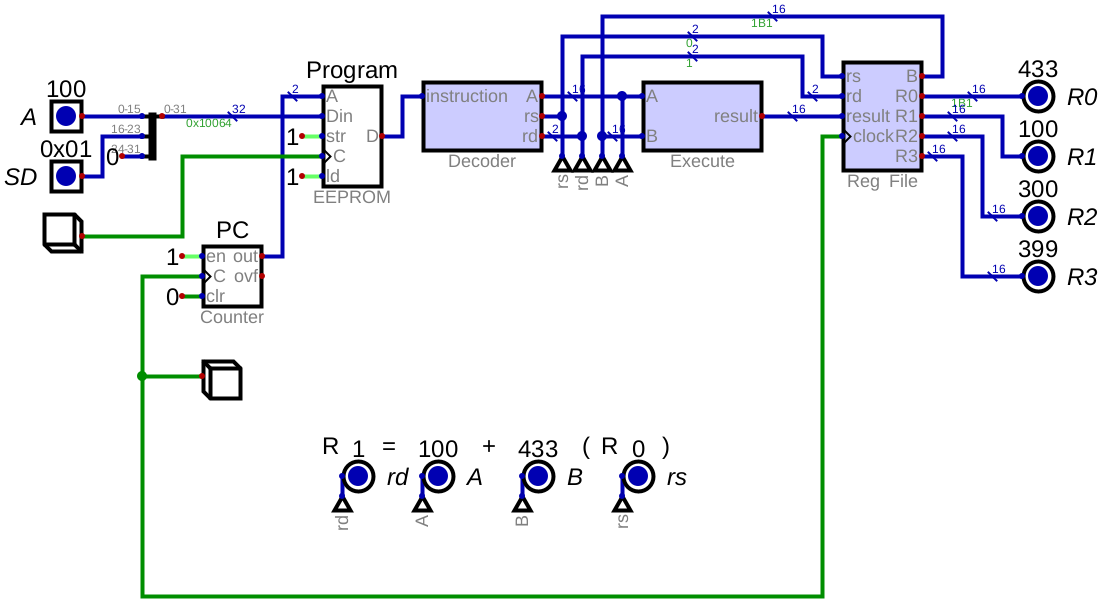

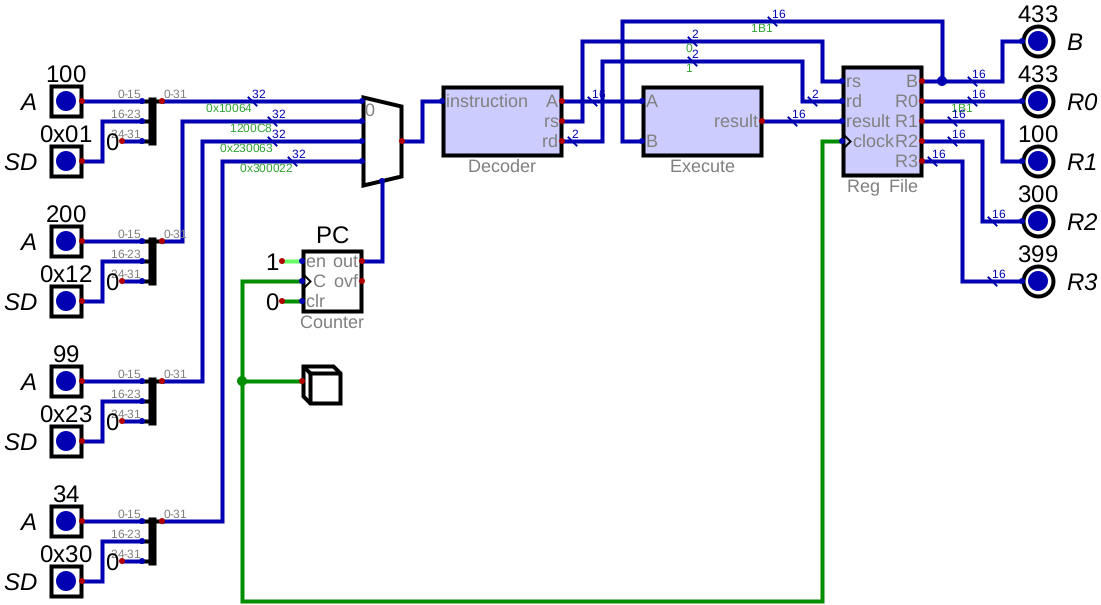

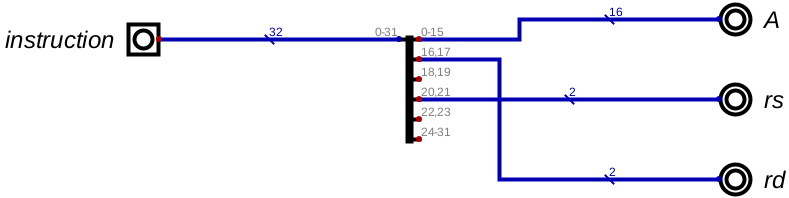

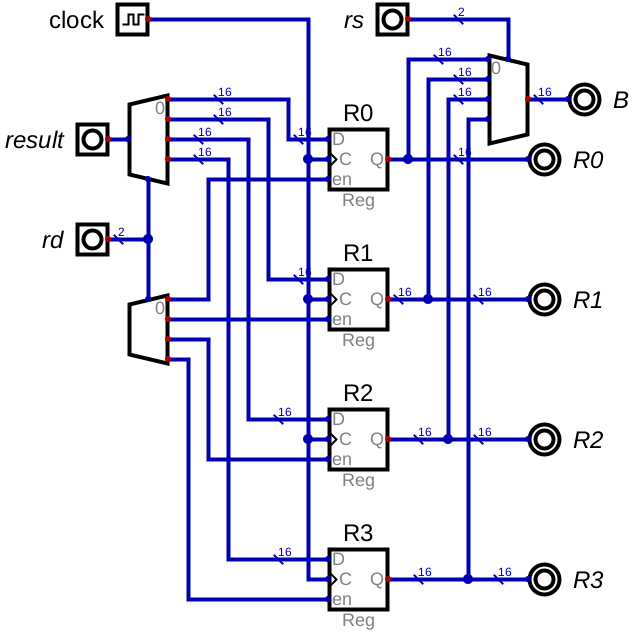

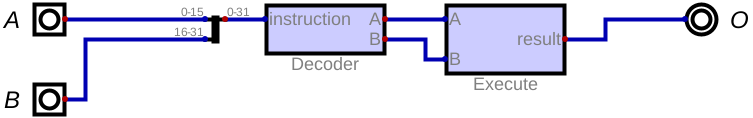

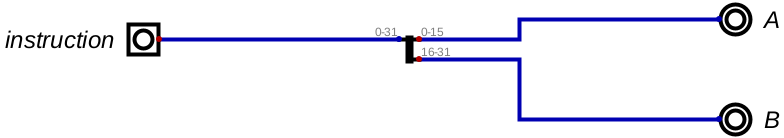

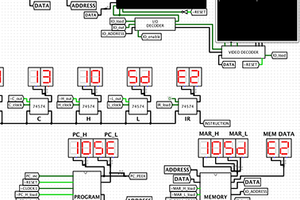

This is a CPU built from scratch in a visual way using a digital circuit simulator called Digital.

This is designed to be a 16-bit RISC Minimal Instruction Set Computer with a limit of 32 instructions (or really, 32 opcodes), and is meant to run in a ICE40 FPGA using open source tools.

All this has been recorded on youtube showing my progress. The first few episodes are pretty amateur, but I get better as the series goes on. I start off trying to teach some concepts, but later on transition into more build videos with commentary.

There is also a video display circuit designed to work with DVI over HDMI with a PMOD.

The circuit is a retro Video Display Processor (VDP), sometimes also known as a Video Display Unit (VDU), or Picture Processing Unit (PPU). It's designed to work similarily to a late 80s graphics system like in the Commodore 64 / Amiga, or the various Nintendo or Sega consoles of that era.

It uses an 8x8 tile based system, with a 40x12 text display of 16x32 pixel characters, of which are made of tiles with 3 shades plus transparent available in 16 colours. The resolution is 640x400 with a 12bpp colour depth.

Currently this is hard-coded to display the frontpanel blinkenlights, but the text is now in a framebuffer so that could allow CPU access to it soon.

Here is a playlist just of the videos showing how this part was built:

rj45

rj45

Fábio Gil

Fábio Gil

Andre Baptista

Andre Baptista

Ruud van Falier

Ruud van Falier

Marcel van Kervinck

Marcel van Kervinck