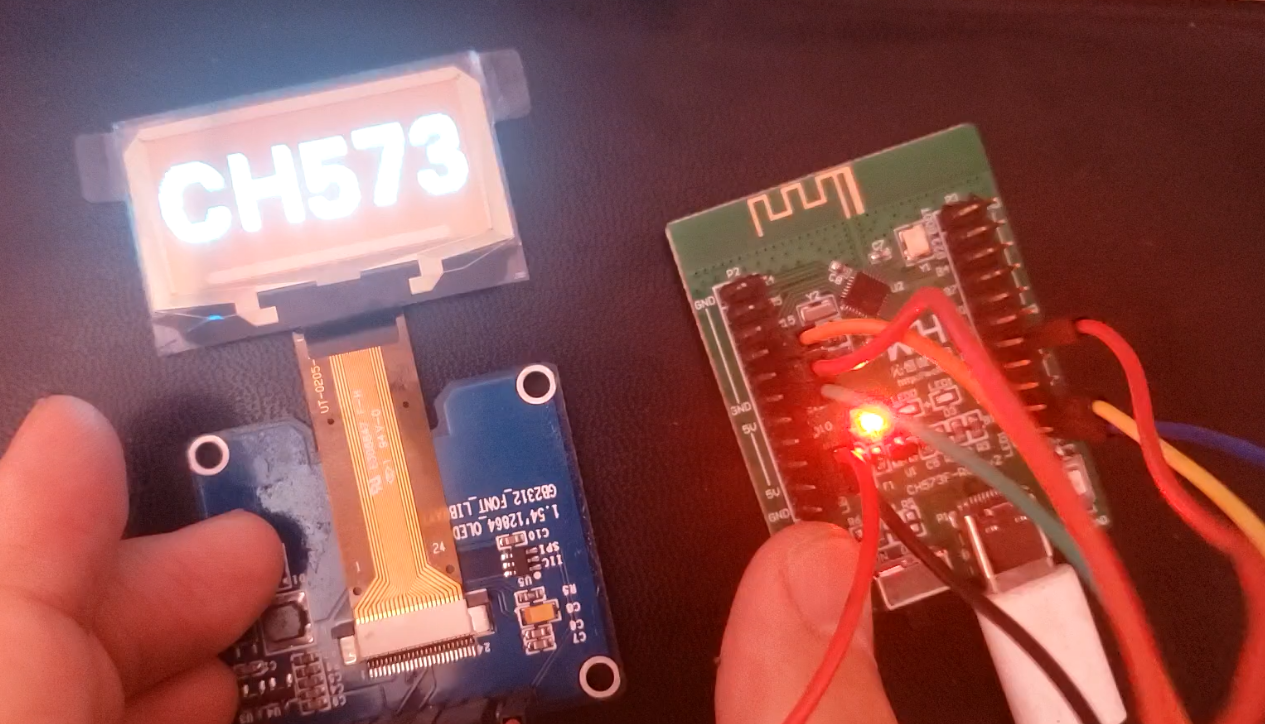

A few days ago, I received the CH573 development board from WCH, so I'd like to try this chip.

and here is some overview of the chip:

- 32-bit RISC processor WCH RISC-V3A

- Supports the RV32 IMAC instruction set, single-cycle multiplication and hardware division

- Built-in 18K SRAM, 512K Flash ROM, ICP, ISP and IAP support for OTA wireless upgrades

- Integrated 2.4GHz RF transceivers and baseband and link control to improve optimized protocol stack and application layer APIs to support networking

- Supports 3.3V and 2.5V power supplies, built-in DC/DC conversion, and 0dBm transmits power with a current of 6mA

- Various low power modes: Idle, Halt, Sleep, Shutdown, built-in battery voltage low voltage monitoring, minimum sleep current 0.3uA

- Built-in USB controller and USB transceiver for USB 2.0 full-speed and low-speed hosts or devices

- Built-in real-time clock RTC supports timing and triggering modes

- An 8-channel 12-bit ADC-to-digital converter is available to support 8-channel touch keys

- Provides 4 sets of 26-bit timers, supports capture/sampling, supports 4 26-bit PWM outputs, and supports 6 8-bit PWM outputs

- Available in 4 sets of stand-alone UART, compatible with 16C550, with a maximum communication port rate of up to 6Mbps

- Available in 1 set of SPIs, built-in FIFO, support for Master and Slave modes

- Built-in temperature sensor

- Available in 20 GPIO, 4 of which support 5V signal input, all GPIO support interrupt and wake-up functions

- Built-in AES-128 plus decryption unit, chip unique ID

- Package: QFN28_4X4

I've ported the u8g2 library to this chip.

Modular

Modular

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.