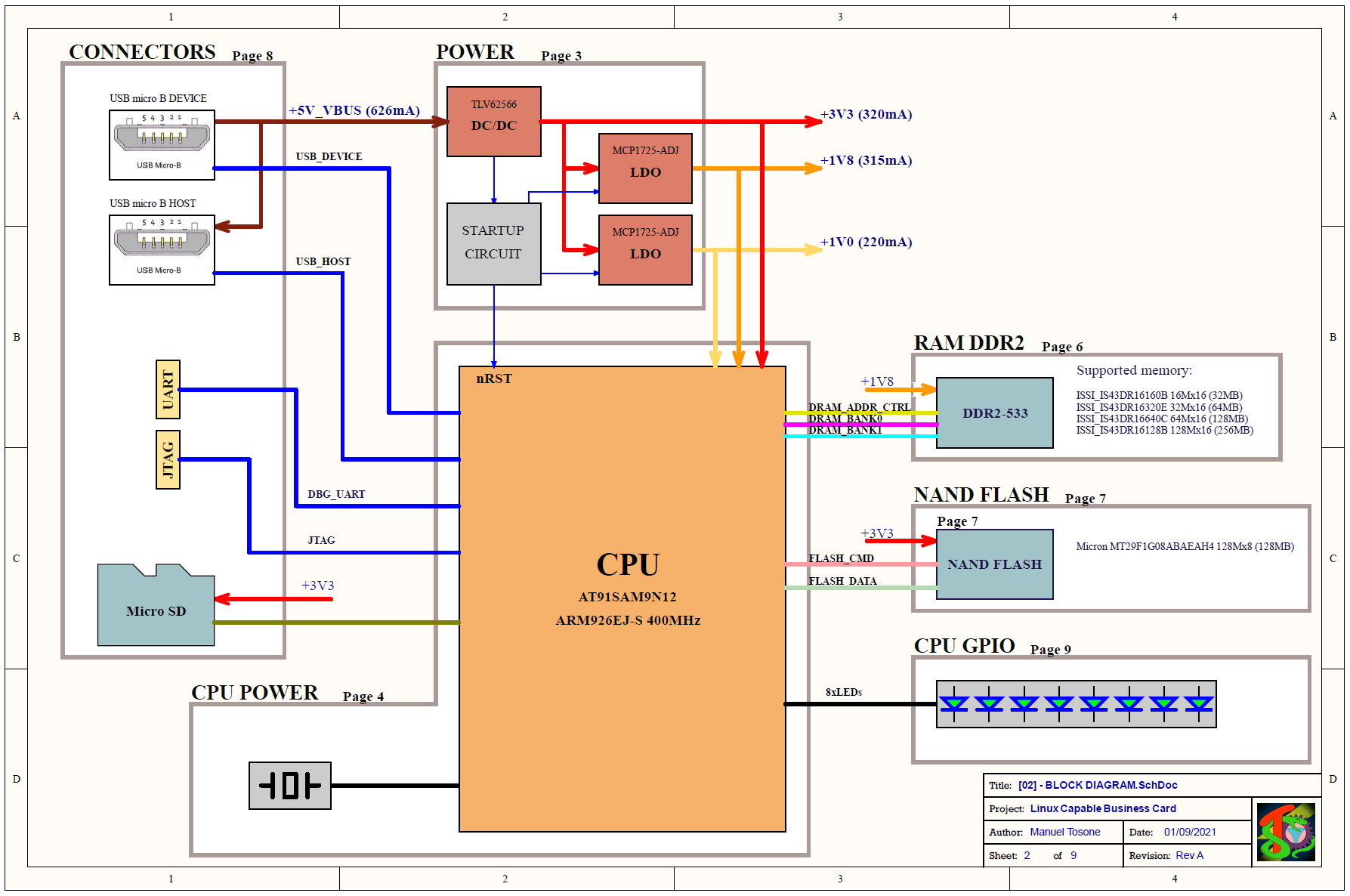

Block Diagram

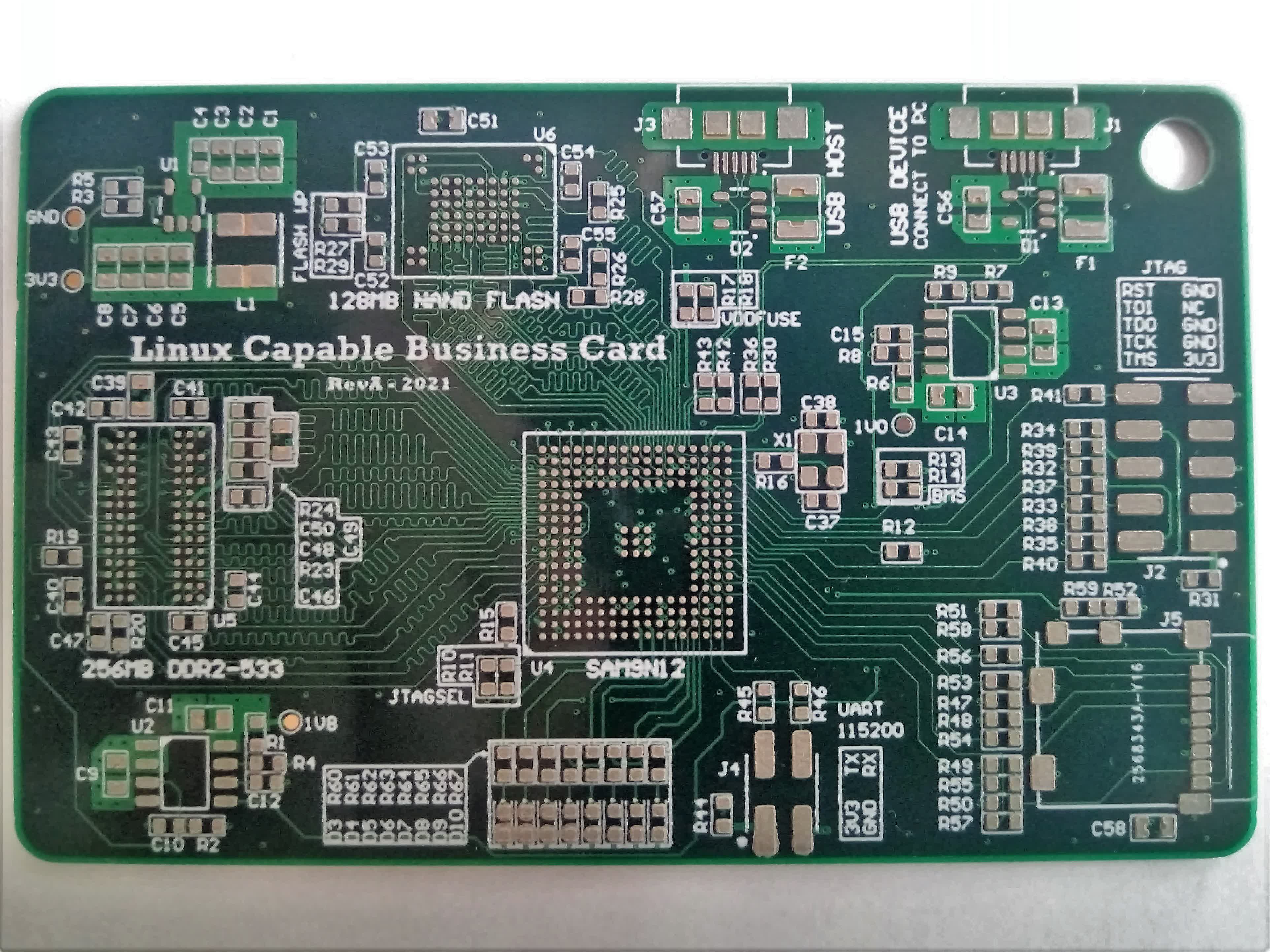

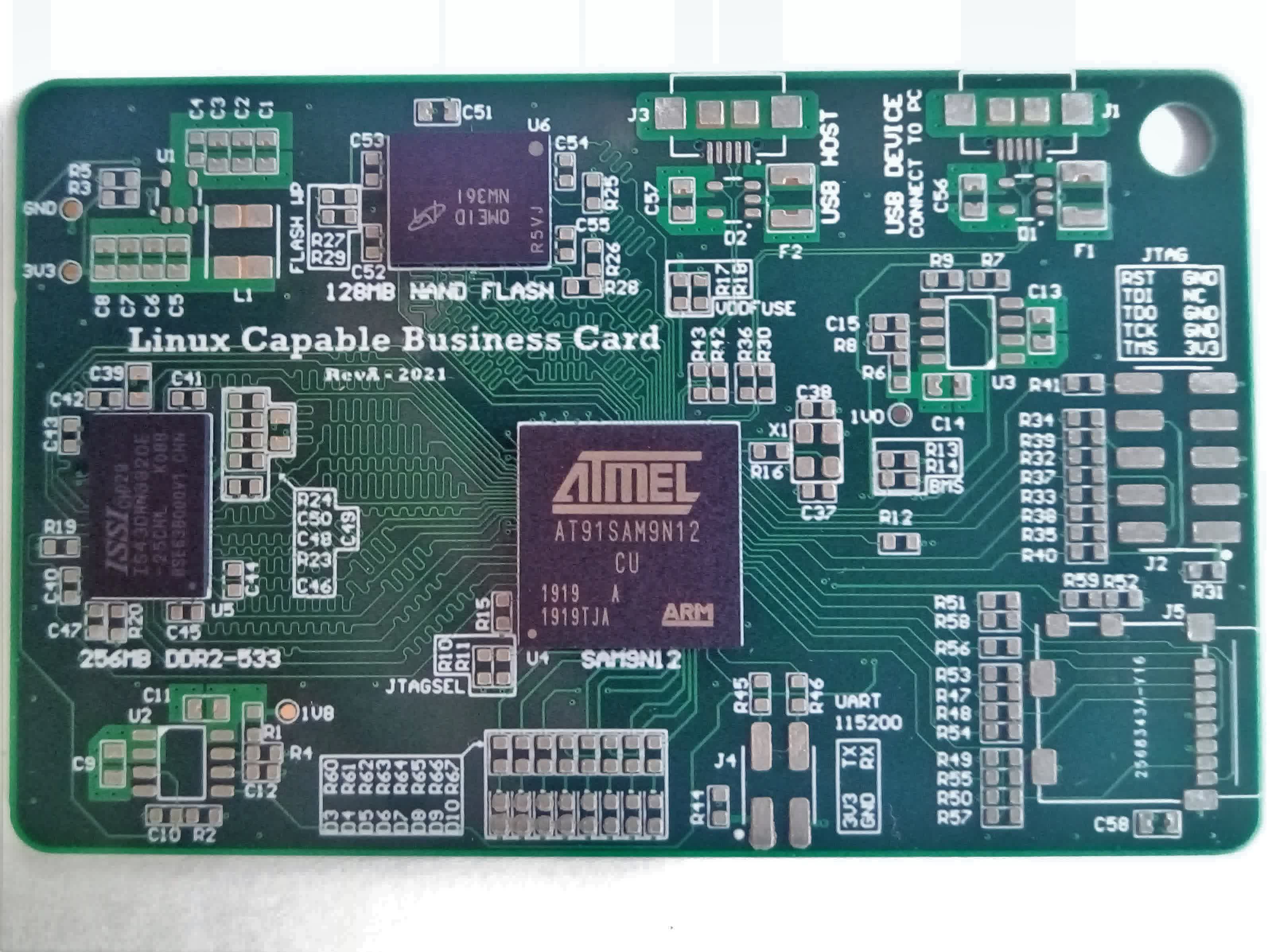

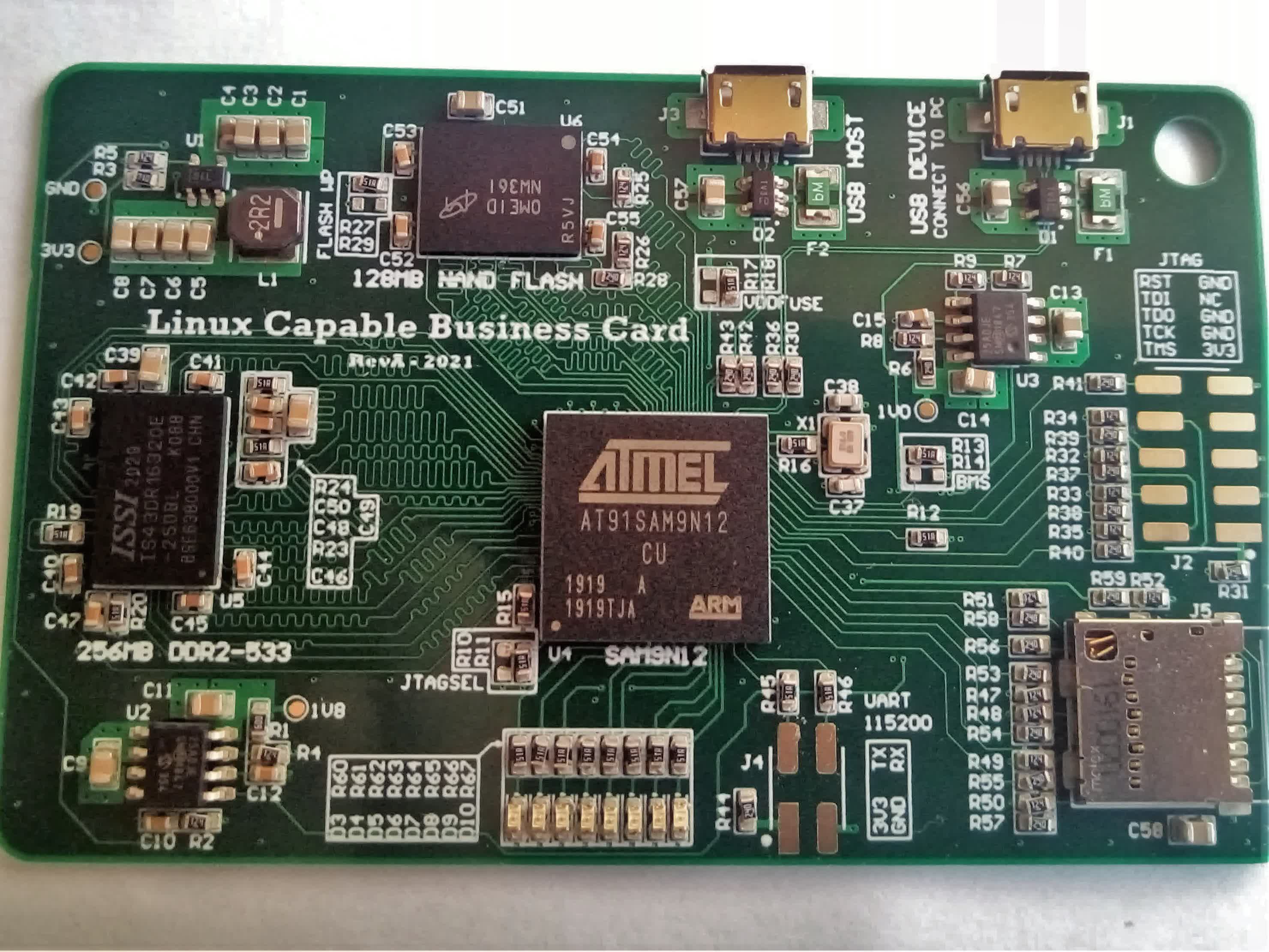

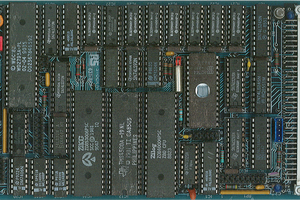

I wanted to design a more complex board, something with DDR memory and a CPU that can run Linux. This board includes a 400MHz ARM processor with DDR2 RAM and NAND FLASH. I don't care about the usefulness of this board, it only serves as practice with high-speed design.

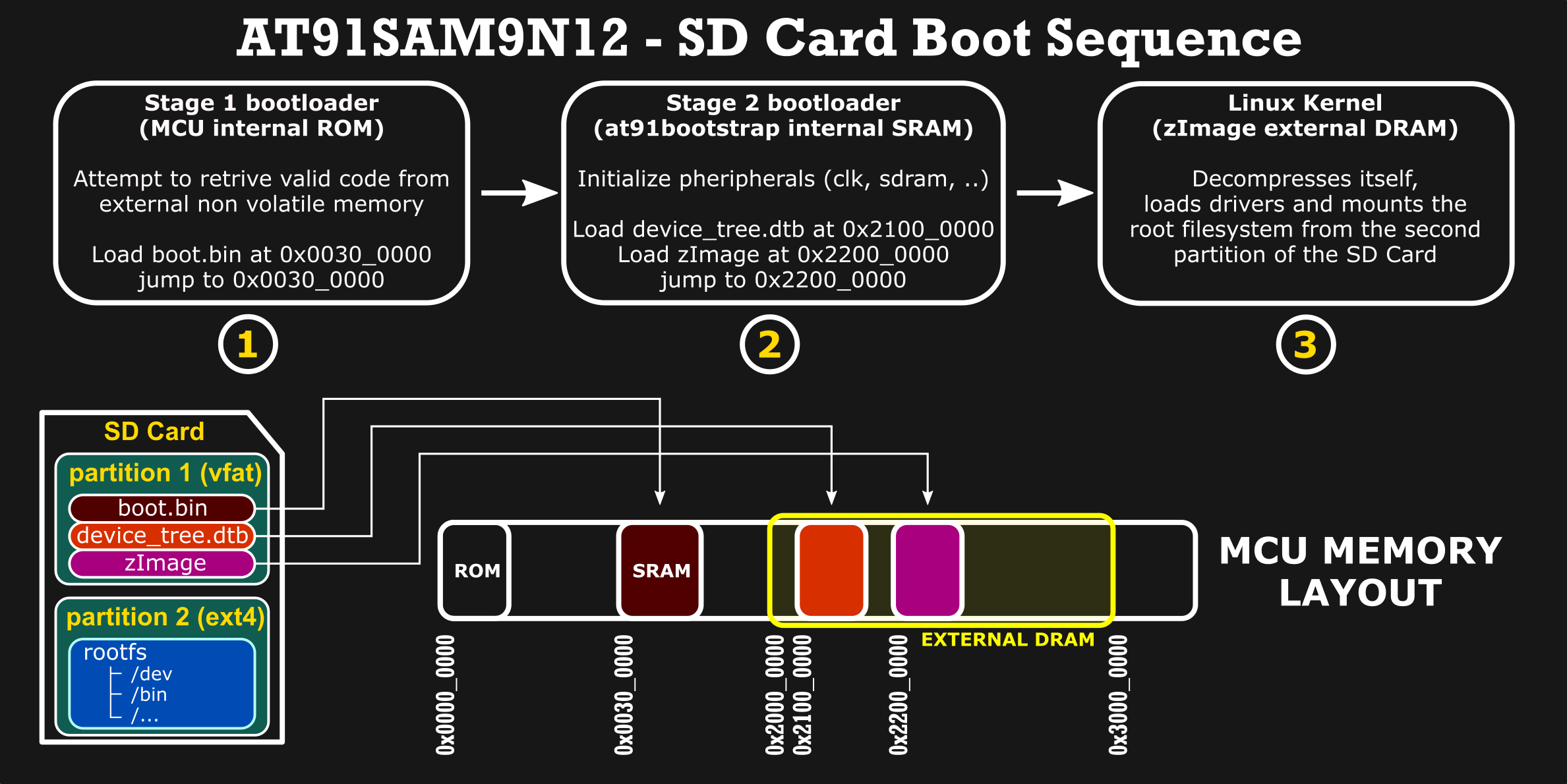

The circuit is very simple, it is built around the AT91SAM9N12 MPU. The board supports up to 256MB of DDR2 RAM and 128MB NAND FLASH. There are two USB ports one HOST and one DEVICE. The DEVICE port is used to load the firmware and connect to a Linux terminal through a virtual com port. The HOST port can be used to connect external peripherals to the board (wifi dongle for example). For debugging there are UART and JTAG connections. The micro SD card can be used as external storage or as a boot device.

The power supply is a little more complicated. The USB 5V is lowered to 3.3V with a buck converter. The 3.3V is then lowered to 1.8V and 1V with linear LDO regulators. To ensure relatable operation the power rails need to come up in a specific order. The enable and power-good signals from the regulators are used to generate the proper sequence (first 3.3V, then 1.8V, last 1V) and to keep the CPU in reset until the power is stable.

The schematic document can be found here.

PCB Considerations

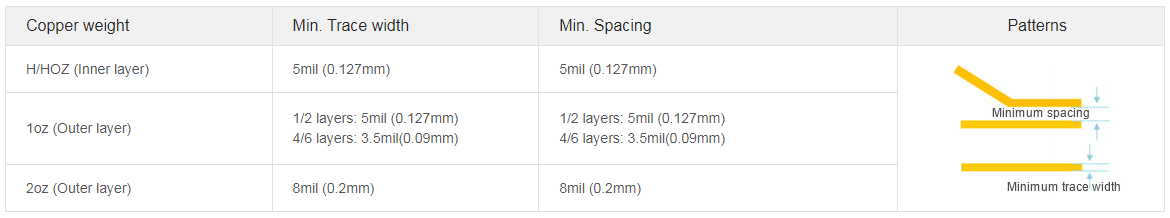

To keep the cost down I want to make a 4 layer board. To manufacture the boards I'll use the JLCPCB service since it is the cheapest that I know of that can manufacture 3.5mil (0.09mm) minimum track width and spacing. To route the DDR interface properly, all the tracks from the two data banks must be routed on the same layer with a solid ground plane underneath. To achieve that on a 4 layer board it is necessary to route two tracks in between BGA pads. BGA packages on this board have a 0.8 mm pin pitch. Making the pads 0.35mm in diameter leaves just enough space for two tracks with the minimum width and spacing.

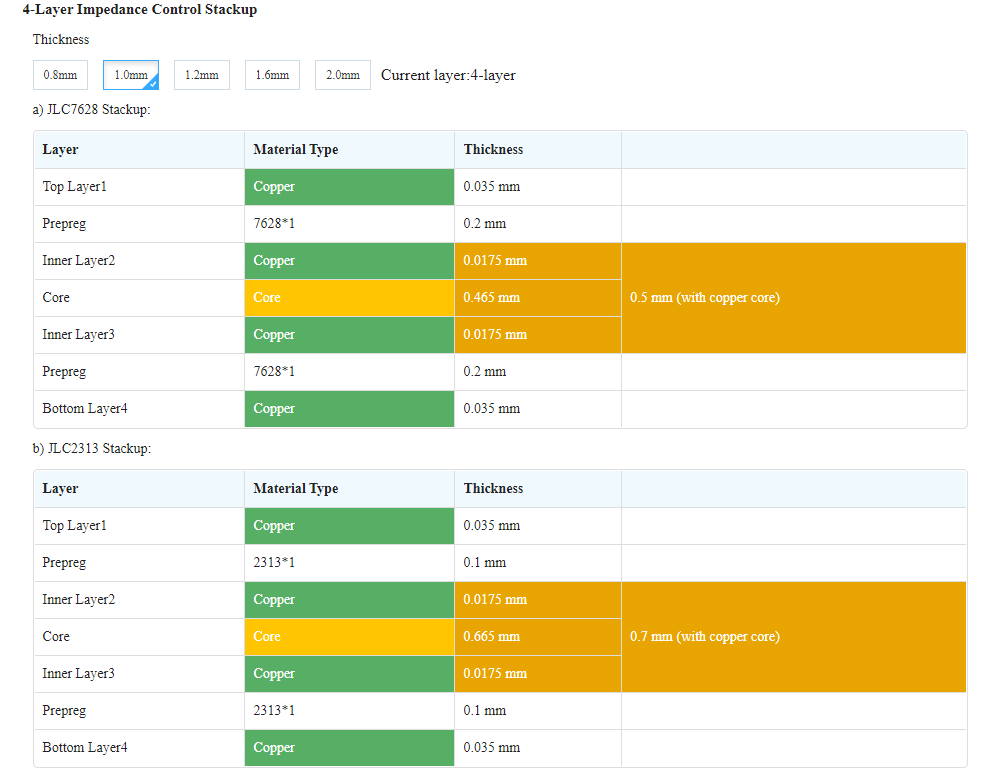

Stackup

For controlled impedance stackups there are two options, they differ in the prepreg and core thickness. For this project, I'll go with the second option (JLC2313 Stackup). Having the reference planes closer to the signal layers reduces crosstalk and, for a given impedance, the traces are smaller.

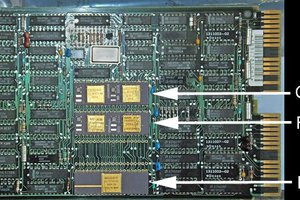

The 4 layers are utilized in the following manner:

- Layer 1: Almost all signals, RAM data banks are routed only on the top layer with a solid ground plane directly below, on layer 2.

- Layer 2: Solid ground plane.

- Layer 3: Power plane. The 1.8V power plane is the reference for the RAM address command and control signals.

- Layer 4: RAM address command and control signals referencing the power plane above. Ground pour to balance construction.

For signal integrity, it is required to control the impedance on high-speed interfaces. In other words, the tracks must be made a specific width that's based upon the stackup. For differential pairs, the distance between traces also depends on the stackup.

The impedances are as follows:

- Most of the tracks are routed as 55 Ohm, including DDR2 data and address signals.

- DDR2 clock differential pair 100 Ohm differential.

- USB differential pair 90 Ohm differential.

Using the JLCPCB impedance calculator, the required trace width and spacing have been calculated.

| Layer | Impedance | trace width | space |

| TOP/BOTTOM | 55 Ohm SE | 4.73 mil (0.120 mm) | - |

| TOP/BOTTOM | 90 Ohm DIFF | 5.55 mil (0.141 mm) | 6 mil (0.152 mm) |

| TOP/BOTTOM | 100 Ohm DIFF | 4.35 mil (0.110 mm) | 6 mil (0.152 mm) |

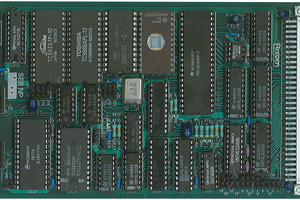

PCB Layout

I made a 15-minute video where I go through the layout of the board. The actual layout took roughly 20 hours.

Manuel Tosone

Manuel Tosone

Keith

Keith

I recently got my hands on a Linux-capable business card, and it's a game-changer! The convenience of having a mini-computer with me all the time is fantastic. It’s perfect for quick tasks on the go. Speaking of efficiency, if you’re looking to streamline your scheduling, check out the https://blog.zumvu.com/calendly-alternatives They can really help optimize your time management!