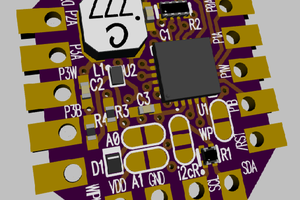

From the Go Configure ForgeFPGA Workshop 6.28 software, these are the details of the initial device offering:

Package:

QFN-24

Supported Development Platforms:

- ForgeFPGA Development Board (SLG7DVKFORGE) + ForgeFPGA Socket Adapter #1 (SLG4SA24-30x30)

Description: The SLG47910V provides a small, low power component for common FPGA applications. The user creates their circuit design by programming the One-Time Programmable (OTP) Non-Volatile Memory (NVM) to configure the interconnect logic, the IO pins, and the Macrocells of the SLG47910V. This highly versatile device allows a wide variety of FPGA applications to be designed within a very small, low power integrated circuit. The macrocells in the device include the following:

- Dense Logic Array:

- Equivalent to 900 4-bit LUTs;

- 1.8 k DFFs;

- 5 kb distributed memory;

- 32 kb BRAM;

- Configurable through NVM and/or SPI interface;

- 50 MHz High-frequency Oscillator:

- 3.41 MHz Low-power mode;

- Phase-locked Loop (PLL):

- Input from external source or internal oscillators;

- Power Supply:

- VDDIO: 1.71 V to 3.6 V;

- VDDCore: 1.1 V ± 10%;

- Power-On-Reset (POR);

MagicWolfi

MagicWolfi

Chris Hamilton

Chris Hamilton

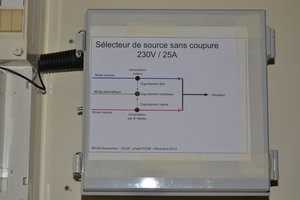

Michel Kuenemann

Michel Kuenemann

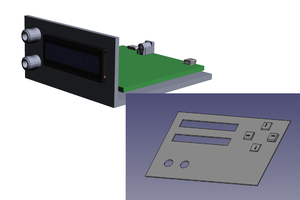

Ashley Robinson

Ashley Robinson

News from Renesas about availability:

https://community.renesas.com/gpak-gfet/f/greenpak-greenfet/29049/forgefpga-availability

Basically, parts shall be available late Q2 2023.