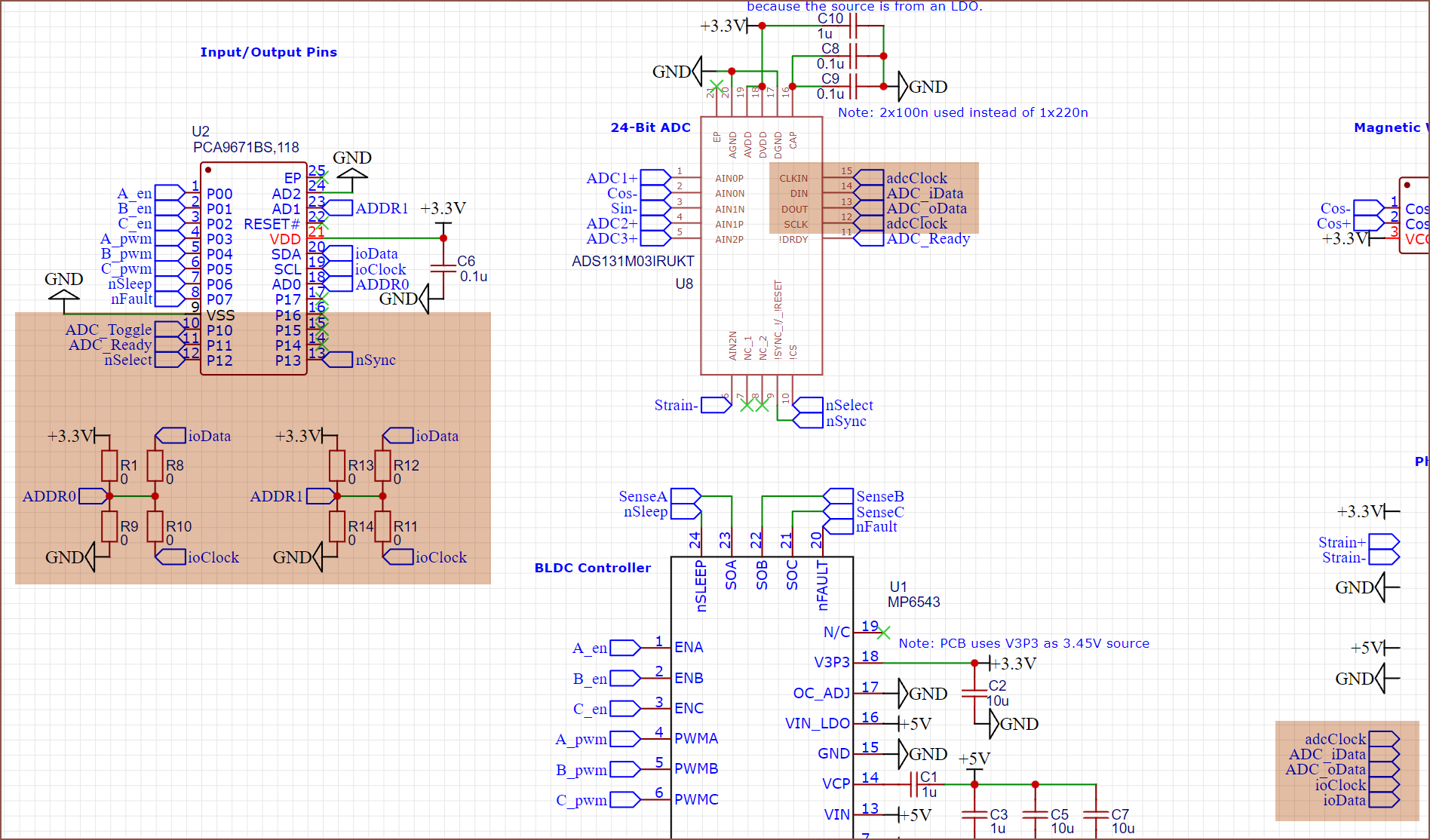

I was still worried that there were going to be ADC SPI issues with the idea I had last log, and realised that SPI shares all but the CS line. This means that I can cut out the Channel0/1 thing, increase the amount of address configurations to 16 and increase the ribbon cable to 5 lines.

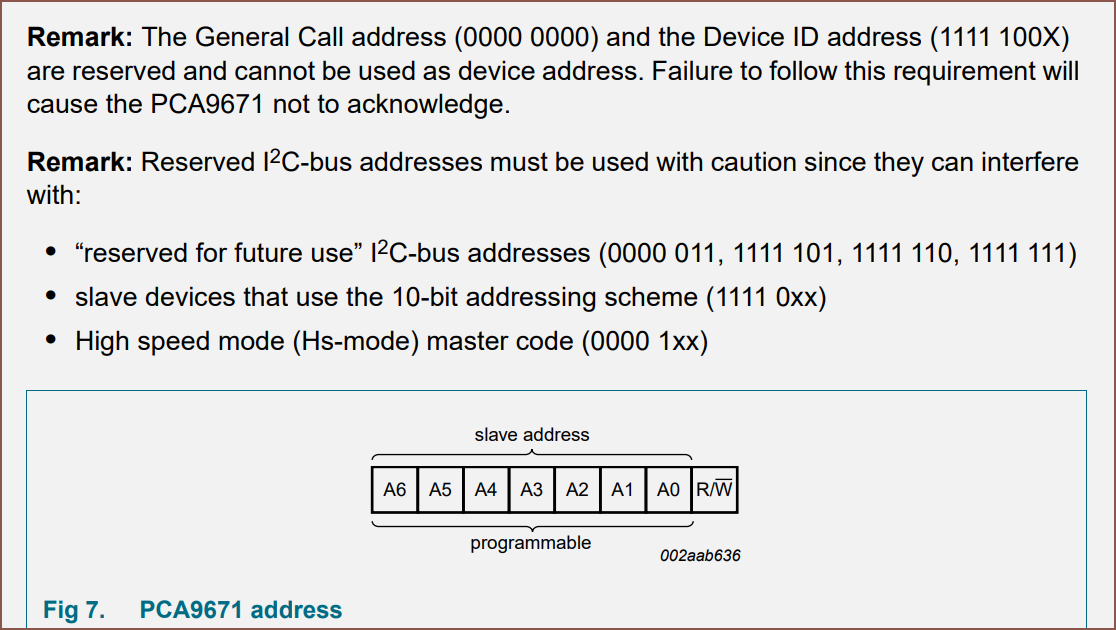

It should mean that the ADC's can use a faster, 8.192MHz channel and hopefully the ioData line isn't as congested. I just haven't checked if any of the 16 device address combinations are device addresses that are recommended against:

kelvinA

kelvinA

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.