[12:30]

I just woke up and realised that the next data in or data out signal for the ADC won't be ready by the next master clock cycle.

I want to make a solution that can take at least 8 daisy chained Tetrinsics. That means I've got 64 bits each way to shift in and out. That's a multiple of 2, so maybe I could install some kind of chip that toggles every 32 clock cycles. Alternatively, I can see if I can swap out a pin for another clock signal. A 3rd idea could be to use oLatch (latch for output pins) as a serial clock.

I'm also thinking that 1k samples in an actuation window may be more than required considering that high-performance gaming mice poll at 1000Hz (80 samples in an actuation window). I don't know how fast I need position data, but I'll assume 1kHz would have me covered there too. At the end of the day, being too fast would be a nice problem to have.

The 8 channel ADC is still a bit pricey, and even more so if I opt for the 24-bit option, so I'll stick with the 24-bit triple ADC already in the design. Going from 32ksps to 2ksps would increase my effective resolution from 14.8 to 16.6 bits at x16 gain, with lower gains approaching 17 bits.

The 8 channel ADC is still a bit pricey, and even more so if I opt for the 24-bit option, so I'll stick with the 24-bit triple ADC already in the design. Going from 32ksps to 2ksps would increase my effective resolution from 14.8 to 16.6 bits at x16 gain, with lower gains approaching 17 bits.I also need to look to see what pins need pull-up resistors.

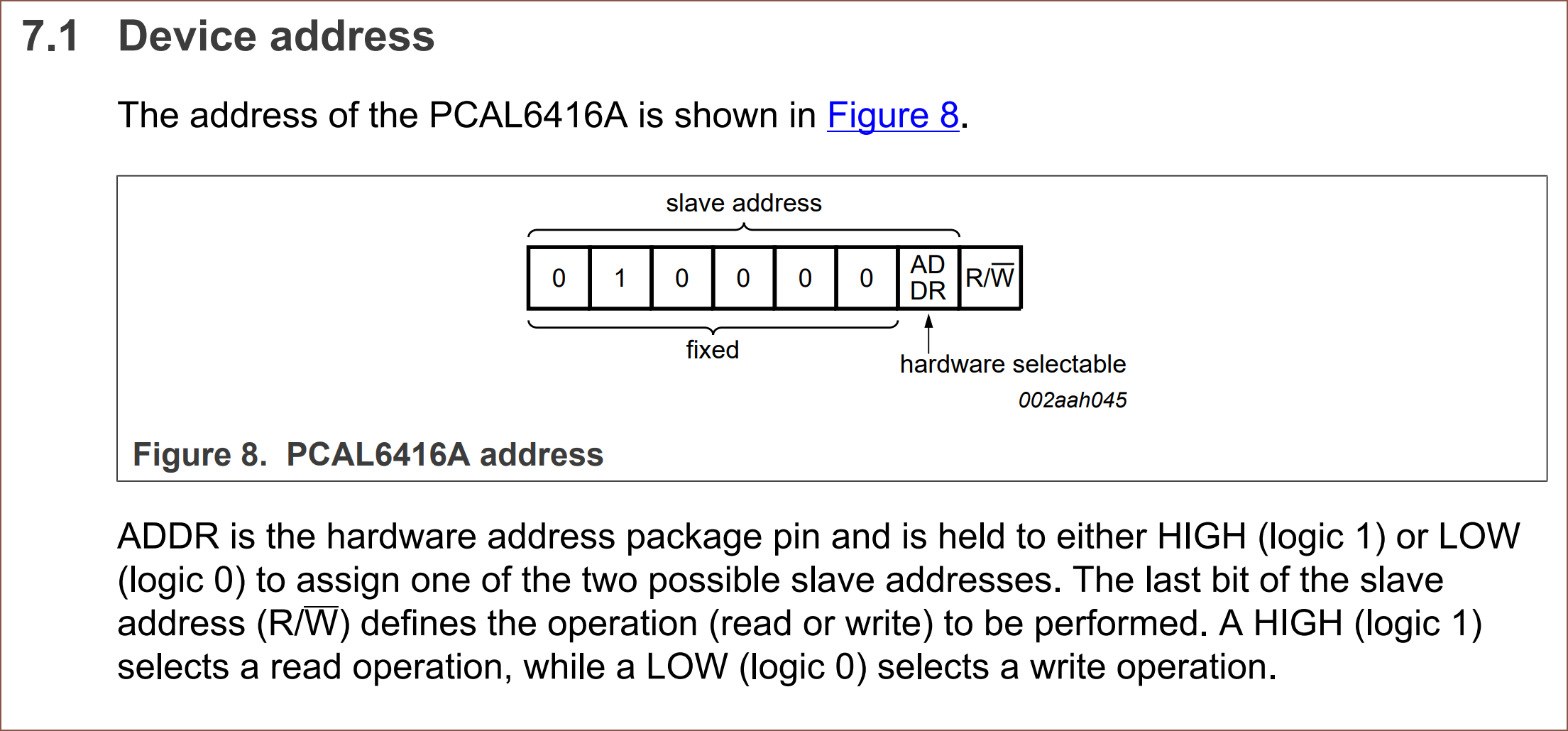

[16:30] The story becomes even more complex now. Apparently, it's somewhat complex to share the 74hc595 and 165 clock pins. I'm going to look into I/O expanders that use I2C. Even with 32.768MHz clock on my initial shift register strategy, the effective signal clock from Tetrinsic's point of view is 512kHz. Thus, I wouldn't need a >1MHz I/O expander for an alternative. Most of the cheap ones are 400kHz by quickly skimming Digikey.

This seems nice. If this is the kind of product I'm looking for, it'll be +55p on the BOM and it's smaller than 1 singular 74HCxxx, though this only assumes that I can route all the connections with 2 PCB layers. There's also a 3x3 BGA package, and I'd probably use that.

This seems nice. If this is the kind of product I'm looking for, it'll be +55p on the BOM and it's smaller than 1 singular 74HCxxx, though this only assumes that I can route all the connections with 2 PCB layers. There's also a 3x3 BGA package, and I'd probably use that.[17:30] It seems that ony 2 of these can be used on a line.

The cheapest one that allows 8 addresses is £1.94 and a 4x4 package. It's a bit of a squeeze but it fits.

The cheapest one that allows 8 addresses is £1.94 and a 4x4 package. It's a bit of a squeeze but it fits. kelvinA

kelvinA

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.