-

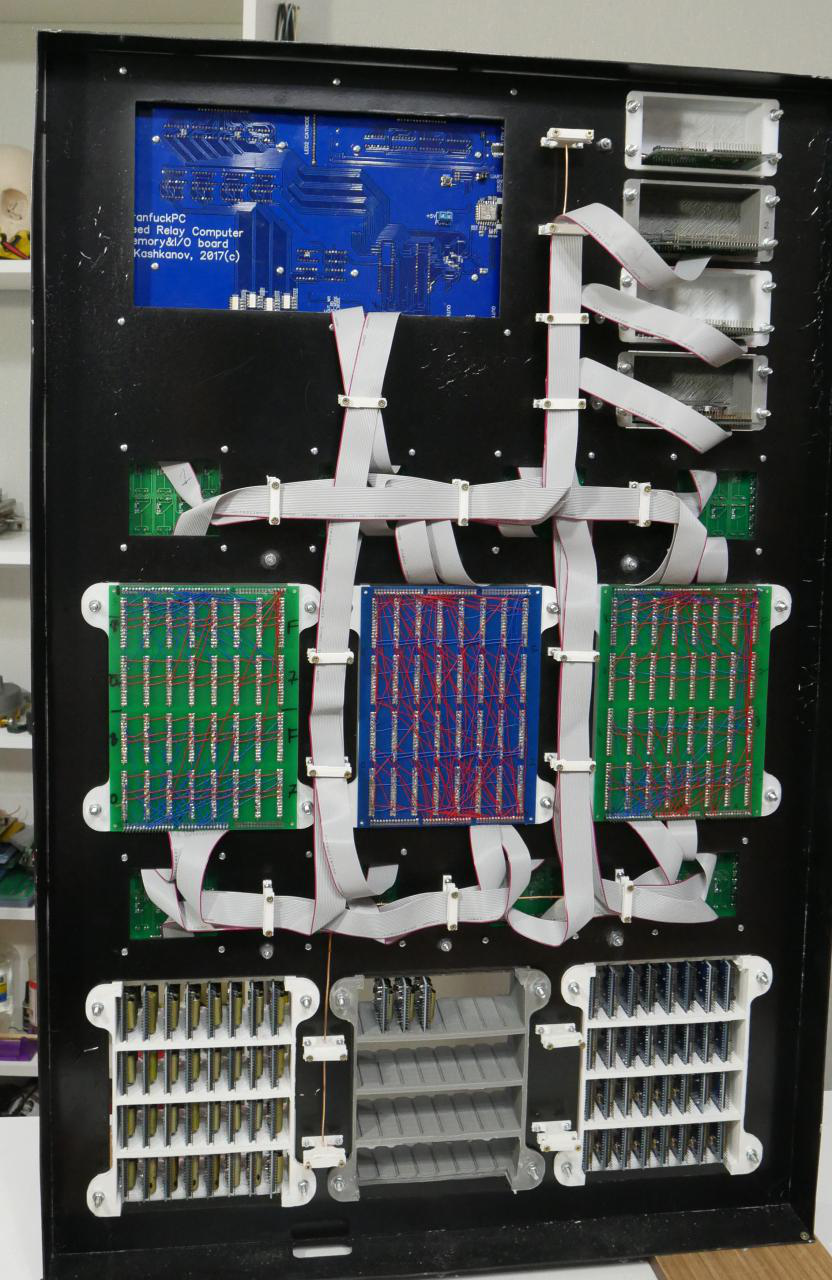

Cables are done

09/12/2018 at 08:00 • 0 commentsI installed connectors to all cables. So I'm ready to interconnect BFPC blocks together

-

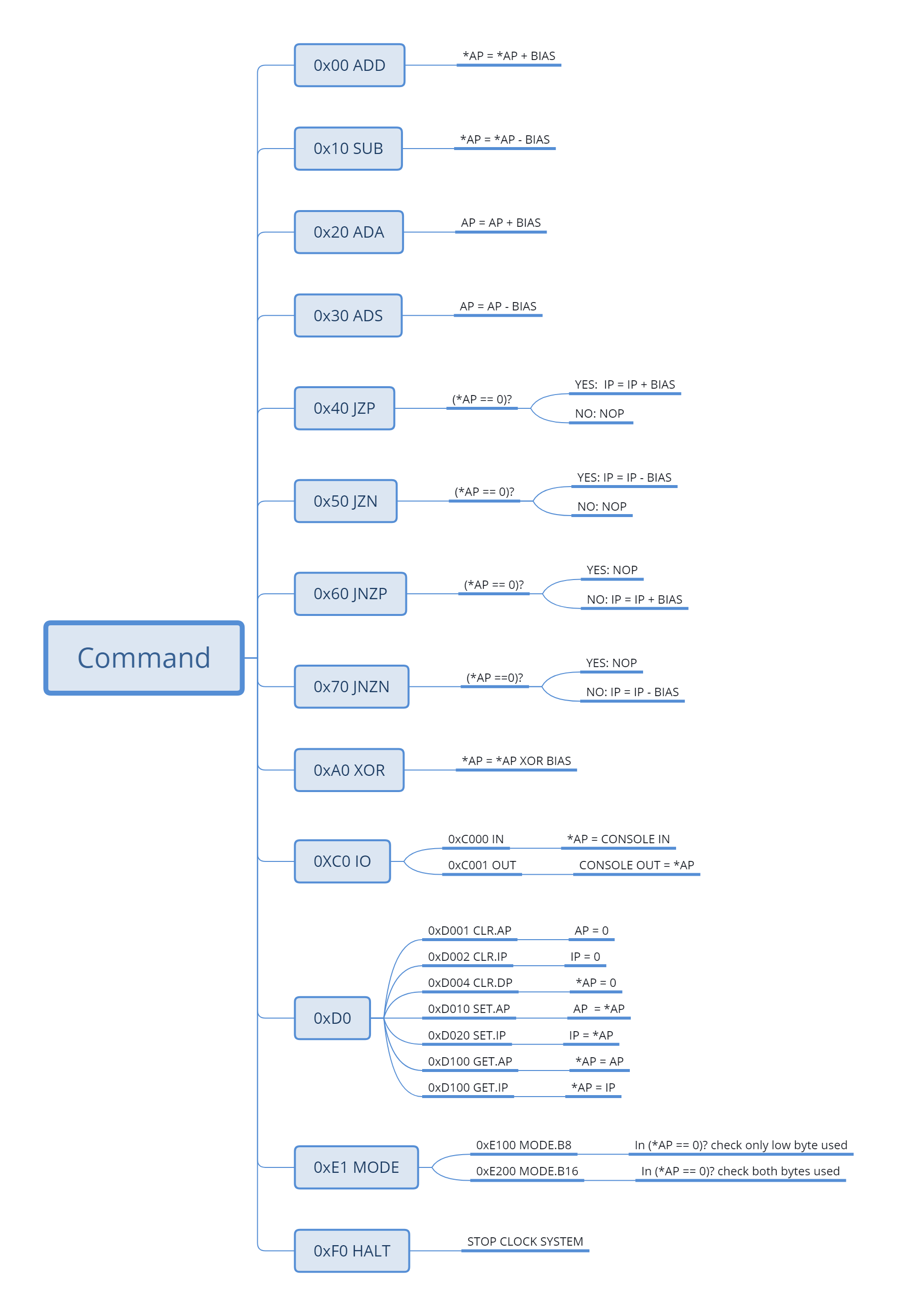

Brainfuck++ Instruction set

09/04/2018 at 08:42 • 0 commentsRC version of instruction set for BrainfuckPC relay computer. It support all +-<>[]., brainfuck instructions and a little bit more. Just because hardware allow me to do it.

Brainfuck mappings:

- ADD = +

- SUB = -

- ADA = >

- ADS = <

- JZP = [

- JNZ = ]

- IO.IN = ,

- IO.OUT = .

All instructions are 16-bit wide.

- Bits 15, 14, 13, 12 - define instruction class

- Bit 12 - Signed bit for Adder commands. Value of this bit extended to 13-15 bits when sending to adder input B;

- Bits 11-0 - contain least 12-bit of signed integer. Master 4 bits generates automatically: 0 for positive and 1 for negative values.

- AP - Address pointer Register

- IP - Instruction pointer register

- *AP - Current Data cell

- CIN - Console input

- COUT - console output

-

Cables. Many cables need to be crimped

09/03/2018 at 08:59 • 0 commentsCables for blocks interconnection are partially done.

25 cables 16-bit width. Using single-line connectors was the greatest fault in device construction planning. Double-line 2x10 connections would be more useful.

-

Started powering up blocks

08/30/2018 at 20:37 • 0 commentsPower line +5V is placed and I started powering up the blocks.

-

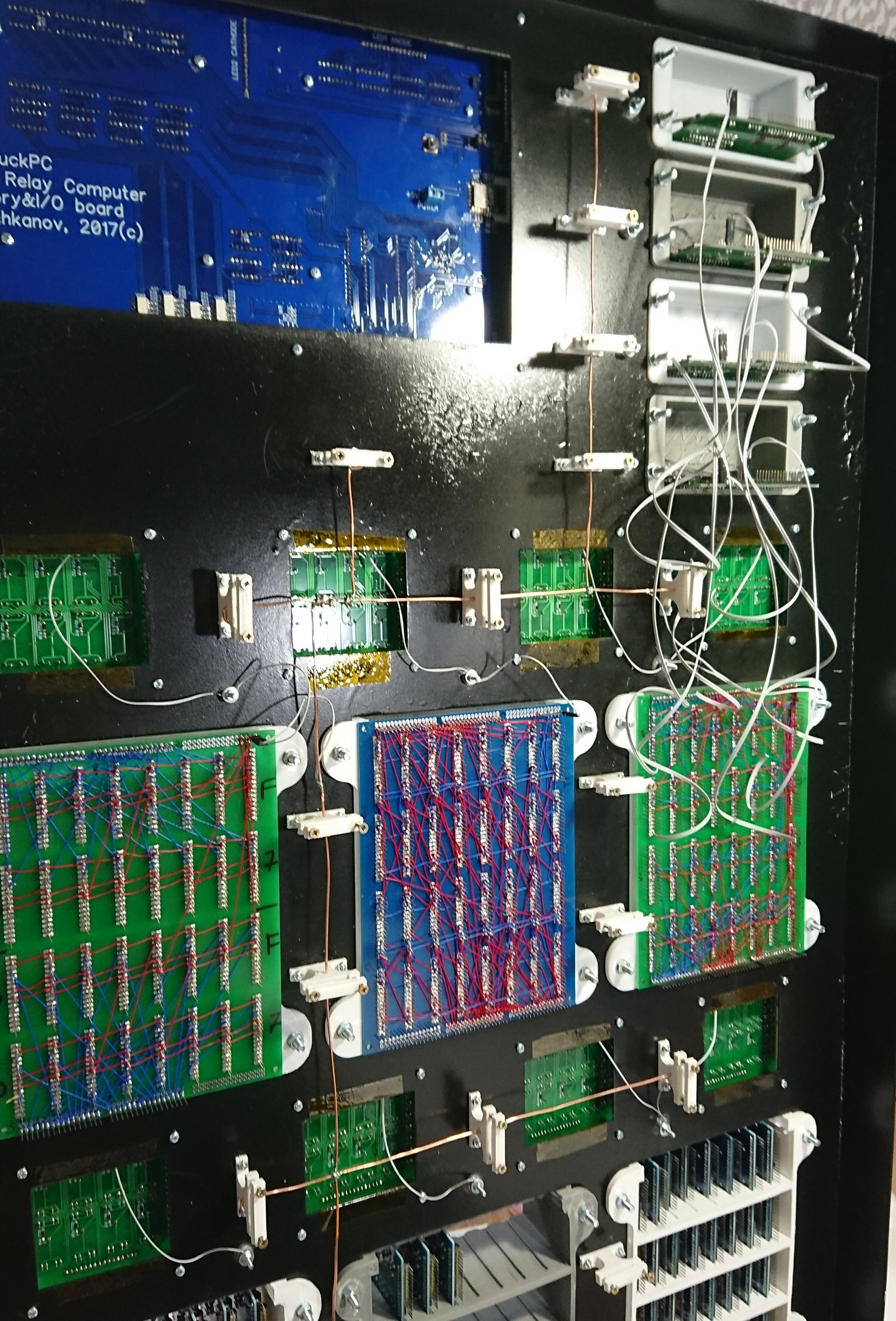

Techno-Shibari.

08/27/2018 at 17:17 • 0 commentsCut cables. Each cable is 20-bit width, bu I need 16-bit only. Need to install connectors on the one side and measured each cable.

-

Power line +5V installed

08/26/2018 at 19:48 • 0 commentsInstalled all cables support (printed them from ABS plastic). As you can see, second register block returned to it's place. It's done.

Next step is to connect VCC and GND to blocks and cut 16-pin cables.

For +5V power delivery 2mm^2 copper wire is used. Second wire (GND) - chassis.

-

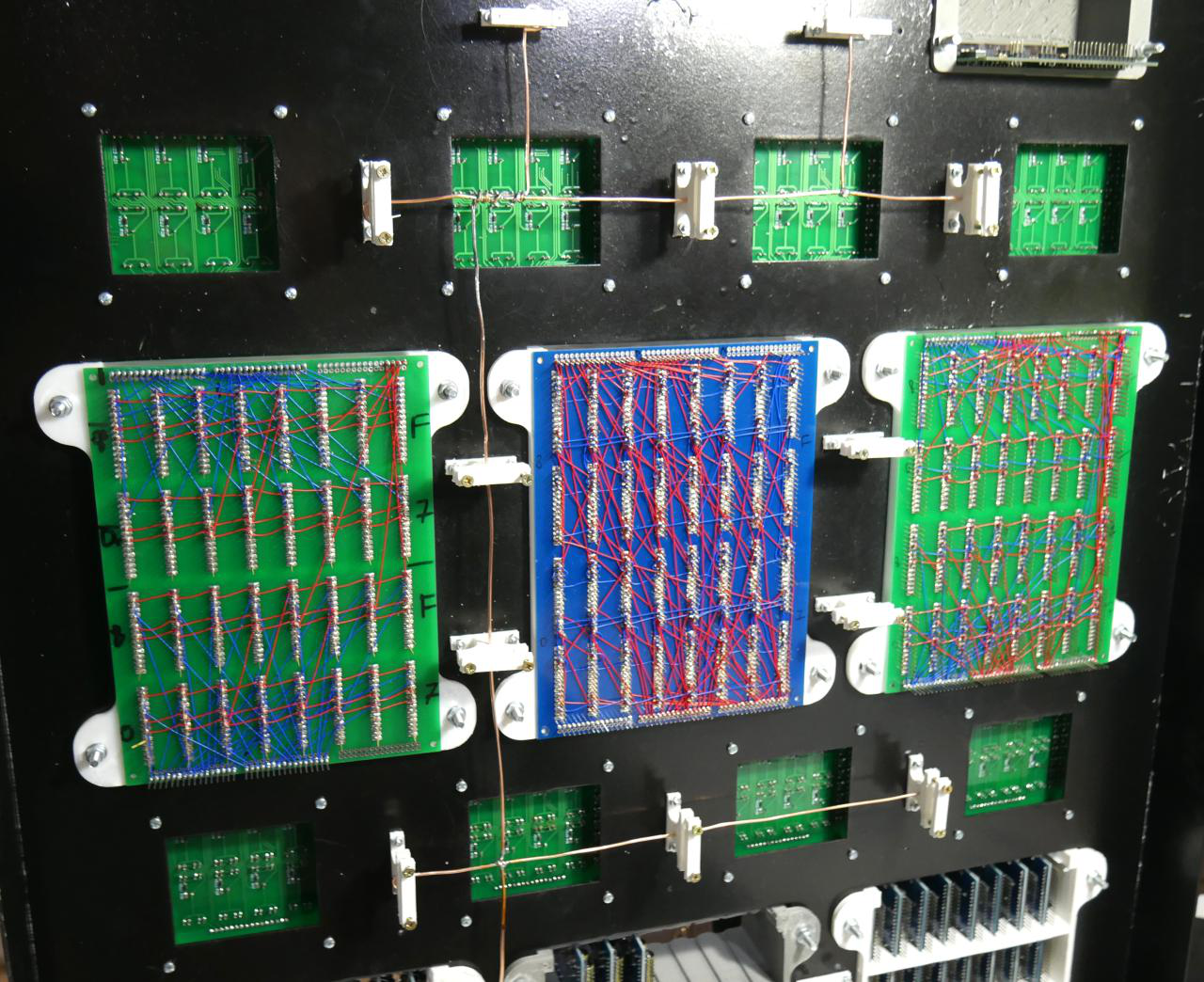

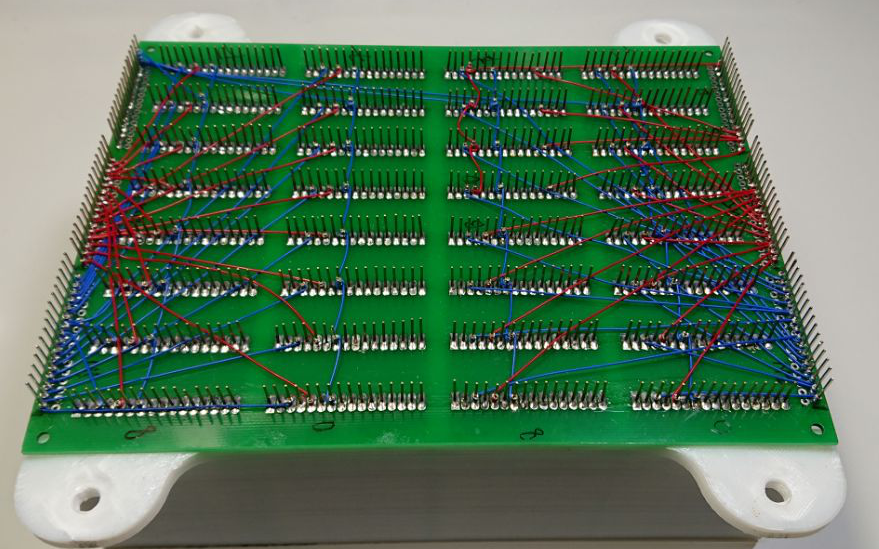

CMD/TMP register wire-wrapping process

08/24/2018 at 19:57 • 0 commentsVacations gone so I have to return to work on the project :)

Current task - to wire-wrap CMD/TMP register block. It's 80% done. Just need to add VCC and WR lines (but want to go to sleep...)

This block contain 3 registers:

16-bit TMP register for Adder A-input

12-bit BIAS register for Adder B-input (4 MSB bit are extended with sign)

4-bit CMD register for Sequencer input.

We load data from Memory to TMP register and load 16-bit width code instructions to BIAS+CMD register.

-

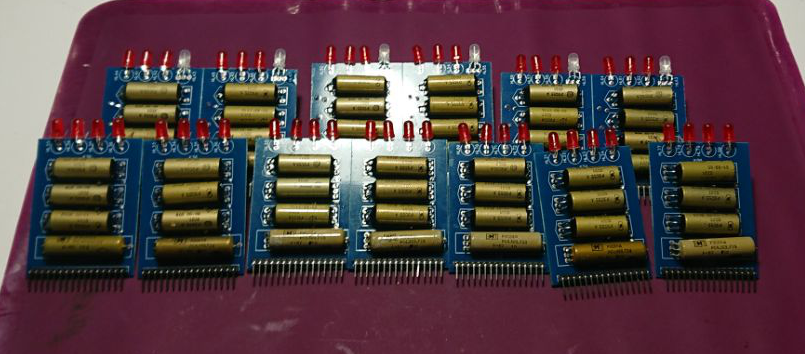

All modules are done

07/20/2018 at 19:09 • 4 commentsLast modules for BrainfuckPC are Done!

Overall modules count: 157pcs.

Relays:

RES55 - 439pcs

RES64 - 75pcs

RES43 - 64pcs

Current number of relays - 578pcs

-

WW29: BrainfuckPC assembly. Stage `I`

07/16/2018 at 19:30 • 7 commentsI'm started with placing all equipment to BrainfuckPC chassis. And it's beautiful.

-

WW28: Less that 24 hour before assembly

07/15/2018 at 19:43 • 0 commentsChassis painting Done and I'm ready to start assembly.

BrainfuckPC Relay Computer

Von-Neumann 16-bit relay computer with Brainfuck++ instruction set

Artem Kashkanov

Artem Kashkanov