I started wiring up the Memory sub-system board and realized quickly that I needed the display board to show the state of the various registers. I first had to create a backplane to connect the boards into. The backplane carries all the signals the display board requires. The display functionality was not part of the original AGC. This functionality is based on my simulator and what I needed to control the simulation. The actual computer required data and control signals are routed via ribbon cables on top of the boards.

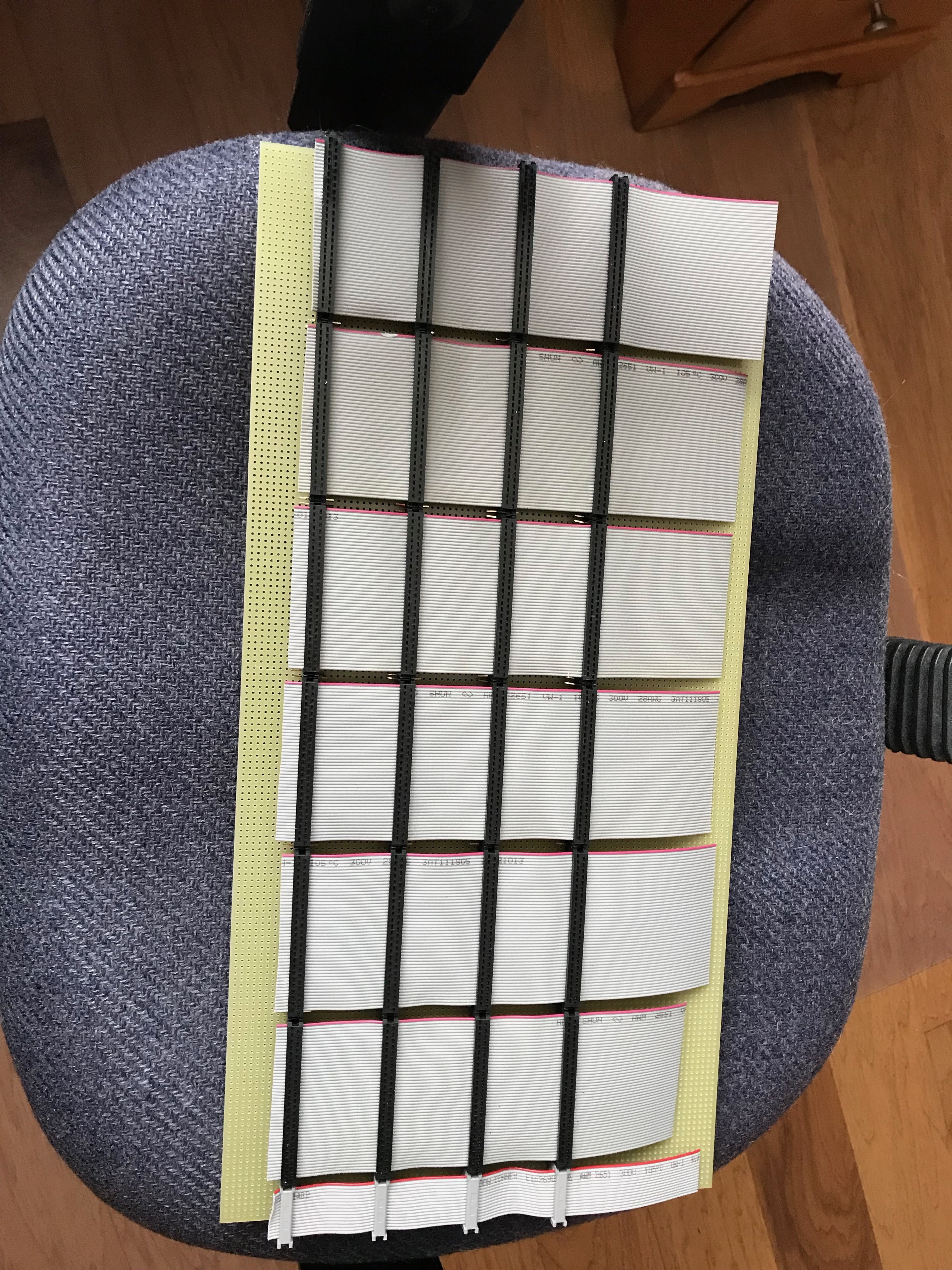

Here is the backplane. Notice that I left room for an additional board, just in case. I had to make all the connector cables and slots universal so I could move the board under test to the back of the stack to have access to the wire wrap pins for debugging purposes.

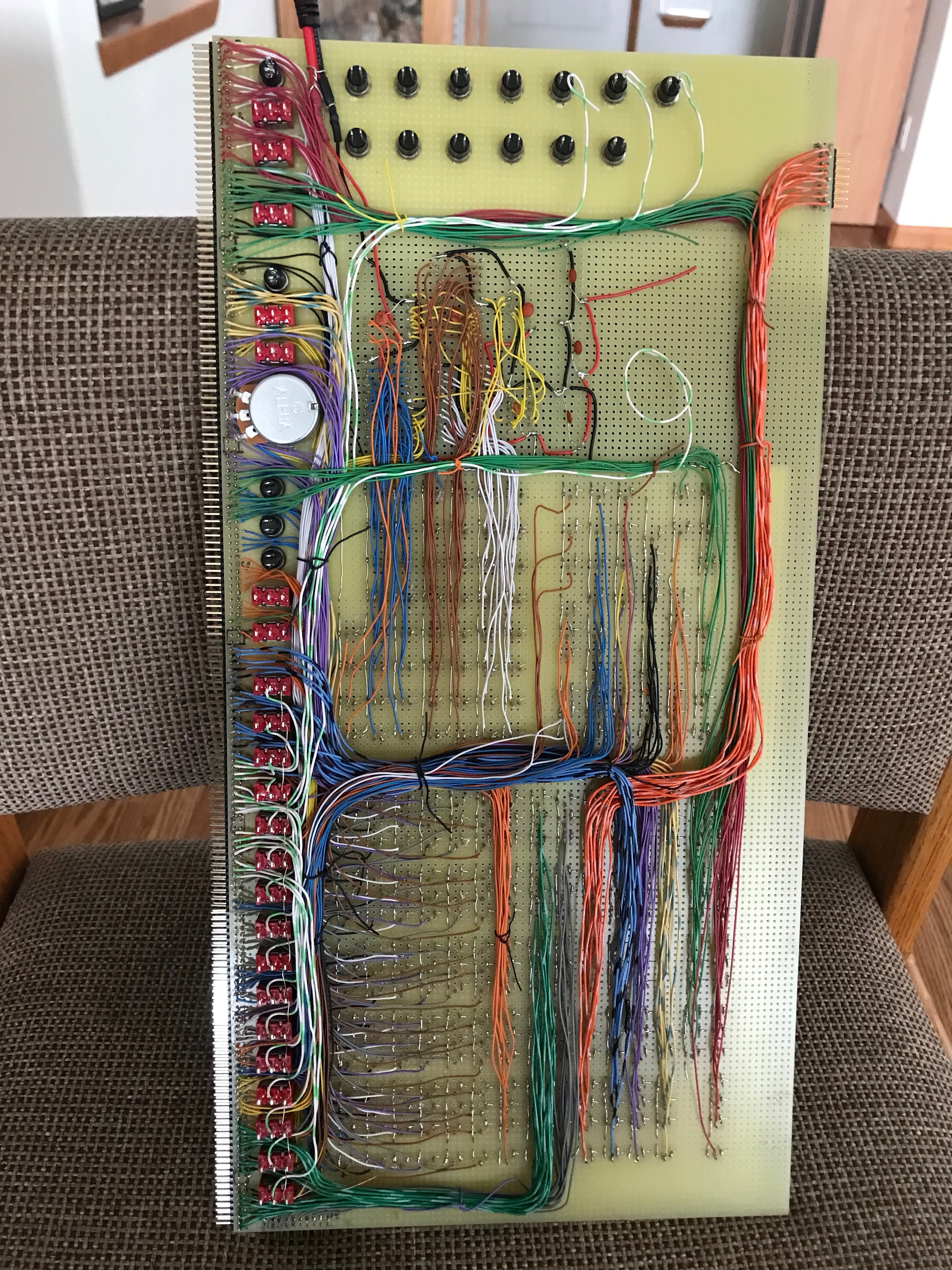

The display panel has LEDs grouped by register. In the middle of the board is an array of sub-sequences showing which sub-sequence is being executed. All of the controls that are available on the simulator are available here, including a row of 16 data/address input switches. I chose to solder this board and the front board of the DSKY. All remaining boards are wire wrap for easy modification when I make that inevitable mistake.

All the LEDs are wired up and tested. I am working on the switch logic.

Here are some of design notes that help understand the schematics.

The backplane is used to route all LED and switch lines between the logic boards and the display board. There are 338 connectors (169 * 2). If a NOT gate is required for the LED to show positive logic, then that is placed on the logic board.

The lines are laid out so that each of the three logic boards (CTL, MEM, PROC) do not have doubled up or overlapping pins. This way only one row of wire wrap terminals are required. It also strengthens the connection as more pins are anchoring the boards. The schematics use global labels to identify connections to the backplane due to the limitations of drawing real estate. The backplane connectors are shown on the interface drawings as single row connectors. The largest connector is 40 pins so multiple 40 pin connectors are required. The global labels on the hardware diagrams are numbered as per the list below.

The pin layouts identify two rows; A & B. The purpose column identifies the subsystem-module purpose with the number of connections in parenthesis. Note: The register and memory switch LSBs are the lower number, the higher number is the MSB. There are two unused pins every 25 pins due to the space required for the backplane ribbon cable connectors. The following tables shows the pin assignments.

Row A:

| Pin # | Purpose |

|---|---|

| 1-16 | MEM-EFM: Memory Bus (1-16) |

| 17-25 | MEM-ADR: S Monitor Bus (1-9) |

| 26-27 | Unusable |

| 28-30 | MEM-ADR: S Monitor Bus (10-12) |

| 31-39 | MEM-ADR: Bank Monitor (9) |

| 40-52 | MEM-ADR: Address Bus (1-13) |

| 53-54 | Unusable |

| 55-57 | MEM-ADR: Address Bus (14-16) |

| 58 | MEM-MBF: EQU3 |

| 59 | MEM-MBF: EQU4 |

| 60 | MEM-MBF: EQU6 |

| 61 | MEM-ADR: EQU17 |

| 62 | MEM-ADR: GTR7 |

| 63 | MEM-ADR: GTR1777 |

| 64 | MEM-MBF: GMZ |

| 65 | MEM-CTR: INC TIME1 (1) |

| 66 | MEM-CTR: INC TIME2 (1) |

| 67 | MEM-CTR: INC TIME3 (1) |

| 68 | MEM-CTR: INC TIME4 (1) |

| 69 | MEM-ADR: Examine Memory Pushbutton (1) |

| 70 | MEM-ADR: Examine Next Pushbutton (1) |

| 71 | MEM-EFM: Read/Write Switch (1) |

| 72 | MEM-ADR: AGC/Manual Switch (1) |

| 73 | MEM-ADR: Clear Parity Pushbutton (1) |

| 74 | MEM-EFM: Load Memory Pushbutton (1) |

| 75 | MEM-INT: RUPT3 Switch (1) |

| 76 | MEM-INT: RUPT4 Switch (1) |

| 77 | MEM-INT: RUPT5 Switch (1) |

| 78 | MEM-PAR: PR_1-15 (1) |

| 79 | CTL-MON: SA (1) |

| 80-81 | Unusable |

| 82-97 | MEM-MBF: G Monitor Bus (1-16) |

| 98-106 | MEM-ADR: Memory Switches (1-9) |

| 107-108 | Unusable |

| 109-115 | MEM-ADR: Memory Switches (10-16) |

| 116 | CTL-MON: BPEN (1) |

| 117 | CTL-CLK: Clock Control: 1 MHz / Slow (1) |

| 118 | CTL-TPG: IBPEN (1) |

| 119 | CTL-CLK: CLK1 (1) |

| 120 | CTL-TPG: CBPEN (1) |

| 121 | CTL-MON: RUN – Exec. Mode (Run/Step) (1) |

| 122 | CTL-MON: INST – Exec. Control (Instruction/Sequence) (1) |

| 123 | CTL-MON: FLCK – Clock Mode (Run/Step) (1) |

| 124 | CTL-MON: Master Reset Switch (1) |

| 125 | CTL-MON: STEP – Exec. Step (1) |

| 126 | CTL-MON: MCLK – Clock Step (1) |

| 127 | CTL-MON: GENRST - Master Reset (1) |

| 128 | CTL-MON: Scalar Enable (1) |

| 129-133 | CTL-SEQ-SEQB: SQ(0-5) (1-5) |

| 134-135 | Unusable |

| 136 | CTL-SEQ-SEQB: SQ(0-5) (6) |

| 137 | CTL-SEQ-SEQB: SNI (1) |

| 138-140 | CTL-SEQ-SEQA: PRE-STG(1-3) (3) |

| 141-143 | CTL-SEQ-SEQA: STG(1-3) (3) |

| 144 | CTL-SEQ-SEQA: BR1 (1) |

| 145 | CTL-SEQ-SEQA: BR2 (1) |

| 146-151 | CTL-SEQ_DCD: Sub-Sequence Bus (6) |

| 152-160 | CTL-TPG: TPG Decoded State (1-9) |

| 161-162 | Unusable |

| 163-169 | CTL-TPG: TPG Decoded State (10-16) |

Row B:

| Pin # | Purpose |

|---|---|

| 1-16 | PROC-ALU: X Monitor Bus (16) |

| 17-25 | PROC-ALU: Y Monitor Bus (1-9) |

| 26-27 | Unusable |

| 28-34 | PROC-ALU: Y Monitor Bus (10-16) |

| 35-50 | PROC-ALU: B Monitor Bus (16) |

| 51-52 | PROC-ALU: U Monitor Bus (1-2) |

| 53-54 | Unusable |

| 55-68 | PROC-ALU: U Monitor Bus (3-16) |

| 69-79 | PROC-CRG: A Monitor Bus (1-11) |

| 80-81 | Unusable |

| 82-86 | PROC-CRG: A Monitor Bus (12-16) |

| 87-102 | PROC-CRG: L Monitor Bus (16) |

| 103 | PROC-ALU: CI (1) |

| 104 | CTL-SCL: F10x Switch (1) |

| 105 | CTL-SCL: F13x Switch (1) |

| 106 | CTL-SCL: F17x Switch (1) |

| 107-108 | Unusable |

| 109 | CTL-CPMC: PINC (1) |

| 110 | CTL-CLK: Clock Rate (1) |

| 111 | CTL-SCL: F10x (1) |

| 112 | CTL-SCL: F13x (1) |

| 113 | CTL-SCL: F17x (1) |

| 114-129 | PROC-CRG: Q Mon Bus (1-16) |

| 130-133 | PROC-CRG: Z Mon Bus (1-4) – Used by MEM-ADR-ATS |

| 134-135 | Unusable |

| 136-147 | PROC-CRG: Z Mon Bus (5-16) – Used by MEM-ADR-ATS |

| 148 | MEM-PAR: PARALM (1) |

| 149-151 | MEM-INT: Selected RUPT (3) |

| 152-154 | MEM-INT: RUPT Latch (3) |

| 155 | MEM-INT: IRQ (1) |

| 156-159 | MEM-CNT: Plus In (4) |

| 160 | MEM-CNT: Plus In Sync (1) |

| 161-162 | Unusable |

| 163-165 | MEM-CNT: Plus In Sync (2-4) |

| 166-168 | MEM-CNT: Selected Counter (3) |

| 169 | MEM-INT: INH (1) |

The backplane has enough room in case another chip board is required. No reason to "cut" myself or the ribbon cables short. Here are pictures of the front and back of the board.

CPU Connectors: The J connectors contain the computer connections related to bus data and control pulses. They are designed in such a way that the three rear sub-system boards are interchangeable. This is due to the fact that the “board under test” is in the rear and is easily accessible. This is accomplished by having a connector for each of the slot's ribbon cables on the backplane even though they may not be used by that specific logic board. These connectors are located on the top of the boards. Only two of the ribbon cables extend to the DISP board. These are located on the side of the boards.

The top connections are positioned to the left of the boards. The order is J107, J101, J106, J105, J102 and J100. J107 starts one pin to the right of the edge and there are two unused pins between connectors so the connector cables can fit.

The following table is as summary of the connectors, how many pins, the purpose, the boards requiring the connection and the spares. The pin assignments are left to right for top pins and bottom to top for side assignments.

| Label | Pins | Purpose | Boards | Spare Pins |

|---|---|---|---|---|

| J100 | 40 | Control Pulses | CTL, PROC, MEM | 0 |

| J101 | 16 | Write Bus | CTL, PROC, MEM, DISP | 0 |

| J102 | 20 | Control Pulses | CTL, PROC | 0 |

| J103 | 16 | Control Pulses | DSKY, CTL | 7 |

| J104 | 20 | Channel Bus, Control Pulses | DSKY, PROC, MEM, DISP, CTL | 2 |

| J105 | 20 | LG Bus, Control Pulses | PROC, MEM | 2 |

| J106 | 40 | Control Pulses | CTL, MEM | 1 |

| J107 | 16 | Address, Control Pulses | CTL, MEM | 5 |

The following lists each ribbon cable and its pin assignments.

J100: (40 pins) CTL, PROC, MEM

| Pin | Signal | Full Name |

|---|---|---|

| 1 | WCH | Write Channel bus |

| 2 | RCH | Read Channel bus |

| 3 | F10X | F10 Scaler Oneshot timeout (1 = active) |

| 4 | L2GD | Direct write L to G |

| 5 | G2LS | Direct write G to L |

| 6 | WQC | Write Q to Channel bus |

| 7 | RQC | Read Channel bus to Q |

| 8 | A2X | Direct write A to X |

| 9 | WZ | Write to Z Reg. |

| 10 | WYD | Write Y Reg to Write Bus shifted right 1 bit |

| 11 | WY | Write to Y Reg. |

| 12 | WY12 | Write 12 bits to Y Reg. |

| 13 | WQ | Write to Q Reg. |

| 14 | CLXC | Clear X reg if BR1 = 0 |

| 15 | WLC | Write L to Channel bus |

| 16 | RLC | Read L to Channel bus |

| 17 | WL | Write to L Reg. |

| 18 | WB | Write to B Reg. |

| 19 | WALS | Write to A & L Reg. |

| 20 | WA | Write to A Reg. |

| 21 | L16 | Write Octal 100000 to L |

| 22 | B15X | Set bit 15 of X reg to 1 |

| 23 | R15 | Octal 15 to Write Bus |

| 24 | RB1 | Octal 1 to Write Bus |

| 25 | R6 | Octal 6 to Write Bus |

| 26 | R1C | Octal 1 (1's Comp) to Write Bus |

| 27 | RB2 | Octal 2 to Write Bus |

| 28 | RZ | Read Z Reg. |

| 29 | RU | Read U Reg. |

| 30 | Z16 | Set bit 16 of Z register |

| 31 | NEACON | Inhibit end-around carry |

| 32 | Z15 | Set bit 15 of Z register |

| 33 | RQ | Read Q Reg. |

| 34 | RL | Read L Reg. |

| 35 | RC | Read C Reg. |

| 36 | GENRST | Reset the system |

| 37 | RB | Read B Reg. |

| 38 | RA | Read A Reg. |

| 39 | RSTRT | Octal 4000 to Write Bus |

| 40 | CI | Set Carry In |

J101: (16 pins) Write Bus

| Pin | Signal | Full Name |

|---|---|---|

| 1 | W1 | Write Bus bit 1 |

| 2 | W2 | Write Bus bit 2 |

| 3 | W3 | Write Bus bit 3 |

| 4 | W4 | Write Bus bit 4 |

| 5 | W5 | Write Bus bit 5 |

| 6 | W6 | Write Bus bit 6 |

| 7 | W7 | Write Bus bit 7 |

| 8 | W8 | Write Bus bit 8 |

| 9 | W9 | Write Bus bit 9 |

| 10 | W10 | Write Bus bit 10 |

| 11 | W11 | Write Bus bit 11 |

| 12 | W12 | Write Bus bit 12 |

| 13 | W13 | Write Bus bit 13 |

| 14 | W14 | Write Bus bit 14 |

| 15 | W15 | Write Bus bit 15 |

| 16 | W16 | Write Bus bit 16 |

J102: (20 pins) CTL, PROC

| Pin | Signal | Full Name |

|---|---|---|

| 1 | RUS | Read U reg with sign bit |

| 2 | PONEX | Clear X reg and set bit 0 to one |

| 3 | PTWOX | Clear X reg and set bit 1 to two |

| 4 | MONEX | Set X reg to minus 1 |

| 5 | PIFL | Prevent end-around carry on X reg if L bit 1 is set |

| 6 | NEACOF | Clear prohibit end-around carry |

| 7 | READ0 | Read channel bus |

| 8 | RAND0 | Read channel bus, AND with A reg |

| 9 | ROR0 | Read channel bus, OR with A reg |

| 10 | RXOR0 | Read channel bus, XOR with A reg |

| 11 | WRITE0 | Write to channel bus |

| 12 | WAND0 | Write to channel bus, AND with A reg |

| 13 | WOR0 | Write to channel bus, OR with A reg |

| 14 | RL10BB | Read ten bits of L |

| 15 | U16 | U reg bit 16 value |

| 16 | L15 | L reg bit 15 value |

| 17 | CLK1 | Clock 1 (normally low) |

| 18 | CLK2 | Clock 2 (normally low) |

| 19 | L1 | L reg bit 1 value |

| 20 | runPINC |

J103: (16 pins) CTL, DSKY

>th >Pin

| Signal | Full Name | |

|---|---|---|

| 1 | CLK1 | Clock 1 Pulse |

| 2 | CLK2 | Clock 2 Pulse |

| 3 | GENRST | General Reset |

| 4 | STBY | Standby (0 = AGC in STBY state) |

| 5 | KBD1 | Read from Channel 15 (Keyboard) |

| 6 | DISP | Write to Channel 10 (Display) |

| 7 | INDC | Write to Channel 11 (Indicators) |

| 8 | Spare | |

| 9 | RPRO | Read PRO Key |

| 10 | CLK3 | Clock 3 Pulse |

| 11-16 | Spare |

J104: (20 pins) PROC, DSKY, MEM, DISP, CTL

| Pin | Signal | Full Name |

|---|---|---|

| 1 | CH1 | Channel Bus bit 1 |

| 2 | CH2 | Channel Bus bit 2 |

| 3 | CH3 | Channel Bus bit 3 |

| 4 | CH4 | Channel Bus bit 4 |

| 5 | CH5 | Channel Bus bit 5 |

| 6 | CH6 | Channel Bus bit 6 |

| 7 | CH7 | Channel Bus bit 7 |

| 8 | CH8 | Channel Bus bit 8 |

| 9 | CH9 | Channel Bus bit 9 |

| 10 | CH10 | Channel Bus bit 10 |

| 11 | CH11 | Channel Bus bit 11 |

| 12 | CH12 | Channel Bus bit 12 |

| 13 | CH13 | Channel Bus bit 13 |

| 14 | CH14 | Channel Bus bit 14 |

| 15 | CH15 | Channel Bus bit 15 |

| 16 | KB_STR | Keyboard Strobe (Key pressed) (to KEYRUPT) |

| 17 | PARALM | Parity Alarm Routed from MEM via J105 |

| 18 | L2 | L reg bit 2 value |

| 19-20 | Spare |

J105: (20 pins) MEM, PROC

| Pin | Signal | Full Name |

|---|---|---|

| 1 | LG1 | L to G Bus bit 1 |

| 2 | LG2 | L to G Bus bit 2 |

| 3 | LG3 | L to G Bus bit 3 |

| 4 | LG4 | L to G Bus bit 4 |

| 5 | LG5 | L to G Bus bit 5 |

| 6 | LG6 | L to G Bus bit 6 |

| 7 | LG7 | L to G Bus bit 7 |

| 8 | LG8 | L to G Bus bit 8 |

| 9 | LG9 | L to G Bus bit 9 |

| 10 | LG10 | L to G Bus bit 10 |

| 11 | LG11 | L to G Bus bit 11 |

| 12 | LG12 | L to G Bus bit 12 |

| 13 | LG13 | L to G Bus bit 13 |

| 14 | LG14 | L to G Bus bit 14 |

| 15 | LG15 | L to G Bus bit 15 |

| 16 | LG16 | L to G Bus bit 16 |

| 17 | G1 | G Reg bit 1 |

| 18 | G16 | G Reg bit 16 |

| 19-20 | Spare |

J106: (40 pins) CTL, MEM

| Pin | Signal | Full Name |

|---|---|---|

| 1 | WE | Write to Memory |

| 2 | SBWG | Write Memory to G Reg. |

| 3 | GENRST | General Reset |

| 4 | W23 | Write to SL |

| 5 | W22 | Write to CYL |

| 6 | W21 | Write to SR |

| 7 | W20 | Write to CYR |

| 8 | RSB | Read Super-bit |

| 9 | RRPA | Read RUPT Address |

| 10 | WS | Write to S Reg. |

| 11 | REB | Read Erasable Bank |

| 12 | RFB | Read Fixed Bank |

| 13 | WG | Write to G Reg, no reset |

| 14 | RG | Read G Reg. |

| 15 | CLK1 | Clock 1 Pulse |

| 16 | MCRO | Special Multiply pulse |

| 17 | Spare | |

| 18 | RPT | Read RUPT Opcode |

| 19 | KRPT | Knockdown RUPT Priority |

| 20 | CLK2 | Clock 2 Pulse |

| 21 | RBBK | Read Both Banks |

| 22 | WEB | Write to Erasable Bank |

| 23 | WFB | Write to Fixed Bank |

| 24 | WBB | Write to Both Banks |

| 25 | WTS | Move data from pre-S to S registers. |

| 26 | WSB | Write the Super-bank bit |

| 27 | CLRP | Clear RPCell |

| 28 | IRQ | Interrupt Request |

| 29 | INHINT | Set INHINT |

| 30 | RELINT | Clear INHINT |

| 31 | WPCTR | Write Priority Counter Sequence |

| 32 | RSCT | Read Counter Address |

| 33 | WOVR | Write Overflow |

| 34 | EQU3 | Address is Octal 3 |

| 35 | EQU4 | Address is Octal 4 |

| 36 | EQU6 | Address is Octal 6 |

| 37 | GMZ | G Reg is all zeros25-31 Spare |

| 38 | GTR1777 | Address > 01777M |

| 39 | GTR7 | Address > 07 |

| 40 | EQU17 | Address = 017 |

J107: (16 pins) MEM, CTL

>td >14

| Pin | Signal | Full Name |

|---|---|---|

| 1 | AD1 | Address bit 1 |

| 2 | AD2 | Address bit 2 |

| 3 | AD3 | Address bit 3 |

| 4 | AD4 | Address bit 4 |

| 5 | AD5 | Address bit 5 |

| 6 | AD6 | Address bit 6 |

| 7 | AD7 | Address bit 7 |

| 8-12 | Spare (5) | |

| 13 | ISBP | |

| GETBP | Determine if breakpoint has been reached | |

| 15 | ISRUPT | Is an interrupt pending? |

| 16 | runPINC | Run the PINC sub-sequence |

DSKY Connectors: The three DSKY boards require interconnections. Given the number of pins required, this board set requires two 40-pin connectors, two 16-pin connectors and one 10-pin connector. The board rows are 47 pins wide so there is plenty of room for the two 40-pin connectors edge mounted across the top. The first connector (J300) contains pins 1-40. The second connector (J301) contains pins 41-80. The third connector (J302) contains pins 81-96. The fourth connector (J303) contains pins 100-115. The fifth connector (J304) contains pins 116-125. There is also a need for power connectors between the boards so they can be separated.

The boards are numbered to ease the decoding. Board #1 is the front board with the keys and display. Board #2 is the middle board with all the display transistors. Board #3 is the main chip board. To better understand this, the first table is a summary of what connectors go between which boards. This is followed by the detailed pin assignments.

| Connector | From | To | Pins | Spares | Pin Range | Purpose |

|---|---|---|---|---|---|---|

| J300 | Board #1 | Board #3 | 40 | 2 | 0-40 | Keyboard/Indicators/Sign Drivers |

| J301 | Board #1 | Board #2 | 40 | 0 | 41-80 | LED Bank Digits/LED Digit Enable |

| J302 | Board #1 | Board #2 | 10 | 1 | 81-90 | LED Digit Enable |

| J303 | Board #2 | Board #3 | 16 | 0 | 100-115 | Data, Activates, Control |

| J304 | Board #2 | Board #3 | 10 | 4 | 116-125 | Activates |

| Pin | Group | Signal |

|---|---|---|

| 1 | Keyboard | 0 Key |

| 2 | Keyboard | 1 Key |

| 3 | Keyboard | 2 Key |

| 4 | Keyboard | 3 Key |

| 5 | Keyboard | 4 Key |

| 6 | Keyboard | 5 Key |

| 7 | Keyboard | 6 Key |

| 8 | Keyboard | 7 Key |

| 9 | Keyboard | 8 Key |

| 10 | Keyboard | 9 Key |

| 11 | Keyboard | VERB Key |

| 12 | Keyboard | ERR RST Key |

| 13 | Keyboard | KEY RLSE Key |

| 14 | Keyboard | PLUS Key |

| 15 | Keyboard | MINUS Key |

| 16 | Keyboard | ENTER Key |

| 17 | Keyboard | CLEAR Key |

| 18 | Keyboard | NOUN Key |

| 19 | Keyboard | PROC Key |

| 20 | Spare | |

| 21 | Indicators | Restart |

| 22 | Indicators | Computer Activity |

| 23 | Indicators | KEY REL |

| 24 | Indicators | OPR ERR |

| 25 | Indicators | STBY |

| 26 | Indicators | Uplink Activity |

| 27 | Indicators | TEMP |

| 28 | Spare | |

| 29 | Indicators | VEL |

| 30 | Indicators | NO ATT |

| 31 | Indicators | ALT |

| 32 | Indicators | Gimbal Lock |

| 33 | Indicators | Tracker |

| 34 | Indicators | Prog |

| 35 | Sign Signals | +R3S |

| 36 | Sign Signals | -R3S |

| 37 | Sign Signals | +R2S |

| 38 | Sign Signals | -R2S |

| 39 | Sign Signals | +R1S |

| 40 | Sign Signals | -R1S |

| 41 | LED Bank Digits | S46 |

| 42 | LED Bank Digits | S47 |

| 43 | LED Bank Digits | S41 |

| 44 | LED Bank Digits | S42 |

| 45 | LED Bank Digits | S45 |

| 46 | LED Bank Digits | S44 |

| 47 | LED Bank Digits | S43 |

| 48 | LED Bank Digits | S32 |

| 49 | LED Bank Digits | S31 |

| 50 | LED Bank Digits | S36 |

| 51 | LED Bank Digits | S33 |

| 52 | LED Bank Digits | S37 |

| 53 | LED Bank Digits | S34 |

| 54 | LED Bank Digits | S35 |

| 55 | LED Bank Digits | S26 |

| 56 | LED Bank Digits | S27 |

| 57 | LED Bank Digits | S21 |

| 58 | LED Bank Digits | S22 |

| 59 | LED Bank Digits | S25 |

| 60 | LED Bank Digits | S24 |

| 61 | LED Bank Digits | S23 |

| 62 | LED Bank Digits | S12 |

| 63 | LED Bank Digits | S11 |

| 64 | LED Bank Digits | S16 |

| 65 | LED Bank Digits | S13 |

| 66 | LED Bank Digits | S17 |

| 67 | LED Bank Digits | S14 |

| 68 | LED Bank Digits | S15 |

| 69 | LED Digit Enable | EN45 |

| 70 | LED Digit Enable | EN35 |

| 71 | LED Digit Enable | EN46 |

| 72 | LED Digit Enable | EN36 |

| 73 | LED Digit Enable | EN47 |

| 74 | LED Digit Enable | EN37 |

| 75 | LED Digit Enable | EN48 |

| 76 | LED Digit Enable | EN11 |

| 77 | LED Digit Enable | EN21 |

| 78 | LED Digit Enable | EN12 |

| 79 | LED Digit Enable | EN22 |

| 80 | LED Digit Enable | EN13 |

| 81 | LED Digit Enable | EN23 |

| 82 | LED Digit Enable | EN14 |

| 83 | LED Digit Enable | EN24 |

| 84 | LED Digit Enable | EN15 |

| 85 | LED Digit Enable | EN25 |

| 86 | LED Digit Enable | ENN16 |

| 87 | LED Digit Enable | EN26 |

| 88 | LED Digit Enable | EN17 |

| 89 | LED Digit Enable | EN27 |

| 90 | Spare | |

| 100 | Driver Data | OUT0 |

| 101 | Driver Data | OUT1 |

| 102 | Driver Data | OUT2 |

| 103 | Driver Data | OUT3 |

| 104 | Driver Data | OUT4 |

| 105 | Driver Data | OUT5 |

| 106 | Driver Data | OUT6 |

| 107 | Driver Data | OUT7 |

| 108 | Driver Control | STBY |

| 109 | Driver Control | OUTDAT |

| 110 | Activate | DE0 |

| 111 | Activate | DE1 |

| 112 | Activate | DE2 |

| 113 | Activate | DE3 |

| 114 | Activate | DE4 |

| 115 | Activate | DE5 |

| 116 | Activate | DE6 |

| 117 | Activate | DE12 |

| 118 | Activate | DE13 |

| 119 | Activate | DE14 |

| 120 | Activate | DE15 |

| 121 | Activate | IND6 |

| 122-125 | Spare |

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.