This solution would work (with a faster CPU) but the Zynq7010 Cortex A9 CPU isn't able to send a new word (32 bits phase shift) every 1 or 2 milliseconds with enough timing precision. I'm now trrying to implement an all PL solution. See next log.

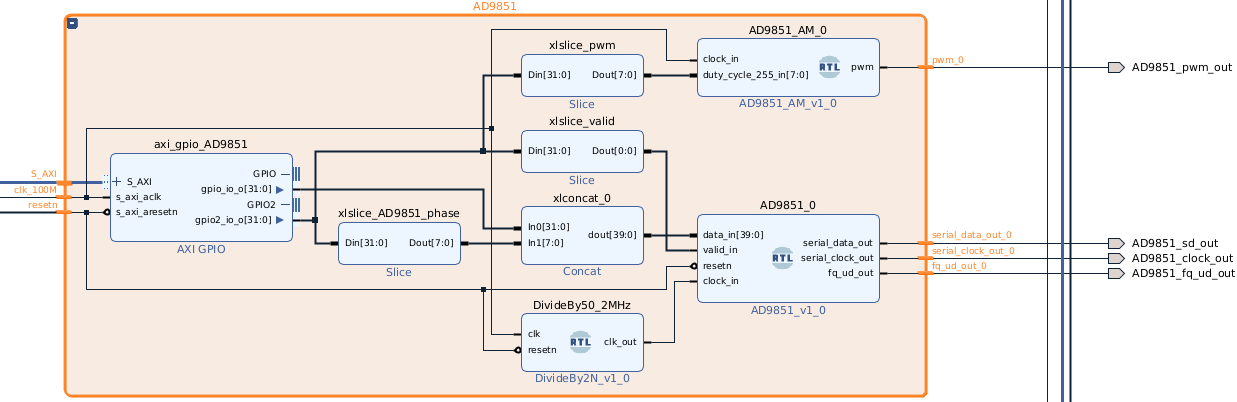

The AD9851_0 VHDL IP is controlled by a GPIO IP (axi_gpio_AD9851) where the two 32 bits output ports act as:

- Port 0: 32 bits DDS phase increment to the AD9851 according to the formula:

Out frequency = phase_increment * 180 MHz / 2^32

- Port 1:

- bits 31 ... 17 : not used

- bit 16 : valid_in signal to the AD9851_0 IP

- bits 15 ... 8 : pwm duty cycle (0 - 255) to AM modulate the output

- bits 7 ... 3 : output phase (always 0)

- bits 2 : power down (0=power out 1=power down)

- bit 1 : always 0

- bit 0 : AD9851 6x (ask the AD9851 to multiply by 6 the 30MHz reference to obtain a 180 MHz clock reference)

Guido

Guido

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.