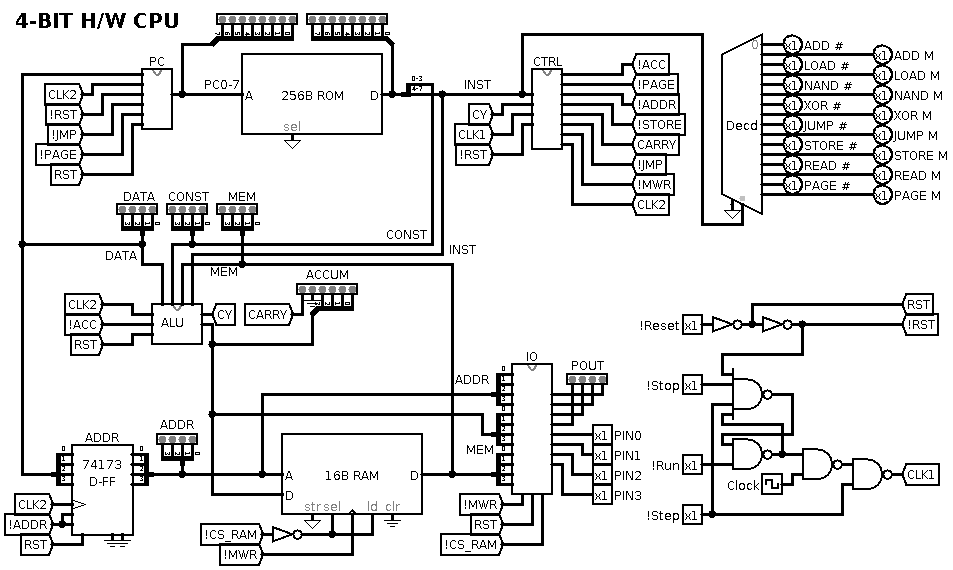

Reverting Back to H/W CPU V1

H/W CPU V1 has the paged Program Counter (PC) and most of the control hardware of H/W CPU V2/V3, I just have to delete the ALU tristate buffer, and edit the memory model.

I will call this version V4:

If you want to see meaningless "computer lights" flashing, here is the LogiSim animation:

The code been run is slightly more complicated than the minimum just to check some other instructions:

20 LOAD 0 ; Clear ACC AF Store MEM[F] ; Output ACC 01 ADD 1 ; ACC<=ACC+1 A0 STORE MEM[0] ; MEM[0]<=ACC C0 READ 0 ; ADDR<=0, preset memory fetch address 3X LOAD MEM[ADDR] ; ACC<=MEM[ADDR] AF STORE MEM[F] ; Output ACC 82 JNC X2 ; Jump if no carry 00 ADD 0 ; Clear carry 81 JNC X1 ; Unconditional jump

The op codes are:

Missing Op Codes?

You may think I am missing op codes such as SHR etc. But no, ADD and NAND are all you need. The rest can be synthesized from ADD and NAND. XOR is included because it needs 14 instructions to read from memory two operands, and to write to memory the resultant. XOR needs 5 instructions to do the same task.

Still, XOR could be swapped out for another instruction.

AlanX

agp.cooper

agp.cooper

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.