Instruction Set Shuffle

Having ADD and SUB in different op code pages seems wrong, as SUB (ACC = Value - 1) can be coded as:

- LOAD Value

- XOR F

- ADD 1

- XOR F

Yes, the carry flag works.

The current op code set would be:

- LOAD Value

- PAGE 8

- SUB 1

- PAGE 0

No saving!

To test for a value you could use:

- LOAD Value

- XOR F

- ADD Test

- XOR F

- ADD F

- JNC [Value == Test]

- [Value != Test]

Or:

- LOAD Value

- SUB Test

- ADD F

- JNC [Value == Test]

- [Value != Test]

A better set of op codes would be:

- 0-1 LOAD/LOAD

- 2-3 ADD/SHR using Carry

- 4-5 SUB/XOR

- 6-7 AND/OR

- 8-9 JNC

- A-B STORE

- C-D READ

- E-F PAGE

AND has been promoted over NAND as it can test for bit states:

- LOAD Value

- AND Bit Mask

- ADD F

- JNC [False == 0]

- [True != 0]

Also:

- ADD 0 clear the Carry flag

- SUB 0 sets the Carry flag.

This will be version 5.

Here is the simulation of up counting followed by down counting, then repeat:

The code for the animation is:

E0 PAGE 0 ; Select Op Code Set 0 20 ADD 0 ; Clear Carry Repeat: 00 LOAD 0 ; Clear ACC Loop1: AF SAVE F ; Output ACC A0 SAVE MEM[0] ; Save to RAM 21 ADD 1 ; Increment 83 JNC 3 ; Loop1 20 ADD 0 ; Clear Carry 0F LOAD F ; Set F Loop2: AF SAVE F ; Output ACC A0 SAVE MEM[0] ; Save to RAM 41 SUB 1 ; Decrement 89 JNC 9 ; Loop2 20 ADD 0 ; Clear Carry 82 JNC 2 ; Repeat

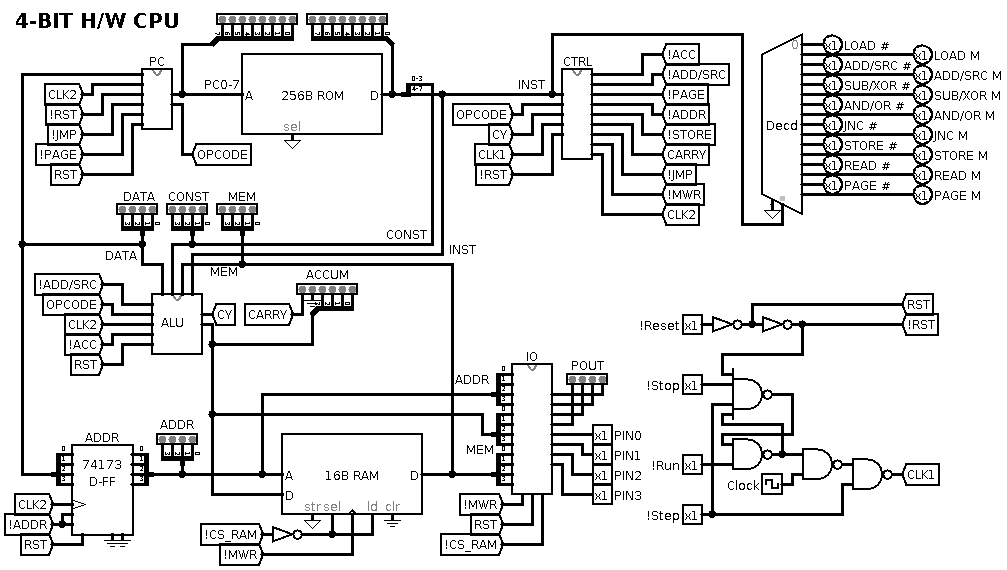

The top level:

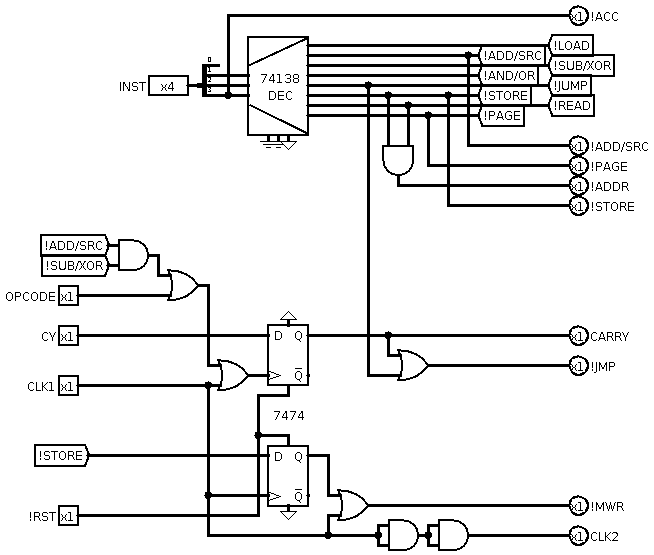

The ALU:

And control:

AlanX

agp.cooper

agp.cooper

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.