A Virtual PCB

At least that is how I explained it to my partner!

It seems as if FPGA boards are pretty rare, almost all the main suppliers are out of stock, but I did find a Tang Nano 9k on ebay in Australia. So that is what I will use.

Gowin (the FPGA manufacture) has a free and no licence educational version of the IDE for the Tang Nano (only 382 Mb) which works except for the bit stream uploader. Checking the Internet, for Linux there is no solution except for the third party programmer: openFGPALoader. Found instructions to compile openFPGALoader and it works fine. Of note, openFPGALoader's command line arguments are human readable.

So next is to learn Verilog, but I will cheat and download a 74xxx library. But one thing I noted is that the list of implemented logic gates avoids those with tri-state outputs?

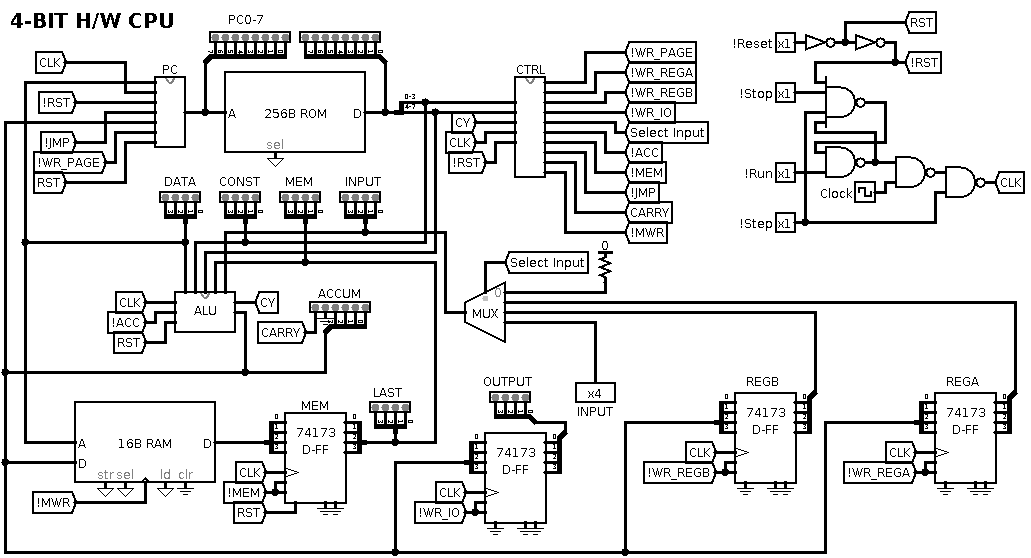

Checking the Internet, it is strongly recommended not to use tri-state outputs as FPGA capacity to model them is quite limited. So okay I will redesign the 4 Bit CPU to use multiplexers:

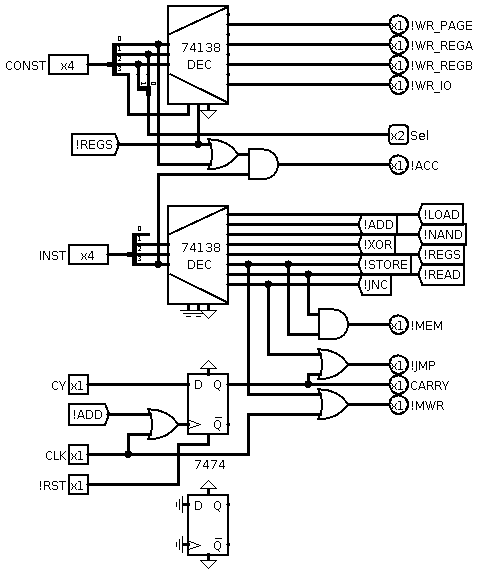

I changed the opcodes to suit the multiplexer, here is the control unit:

I will have to swap the 74173 with a 74377 reduced to 4 bits.

I will have to study the Gowin IP with regard to BROM and BRAM.

74xxx Verilog Code

Although I am not familiar with the syntax of Verilog, the 74xxx code is very easy to understand.

There appears to be option with regard to ROM/RAM, you can roll your own or use the specialised RAM on chip. I have to review:

- Shadow SRAM (17280 bits)

- Block SRAM (468k/26)

- PSRAM (64M bits)

- Flip-Flops (6480, roll your own RAM)

- and set up ROM

TBC ...

AlanX

agp.cooper

agp.cooper

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.