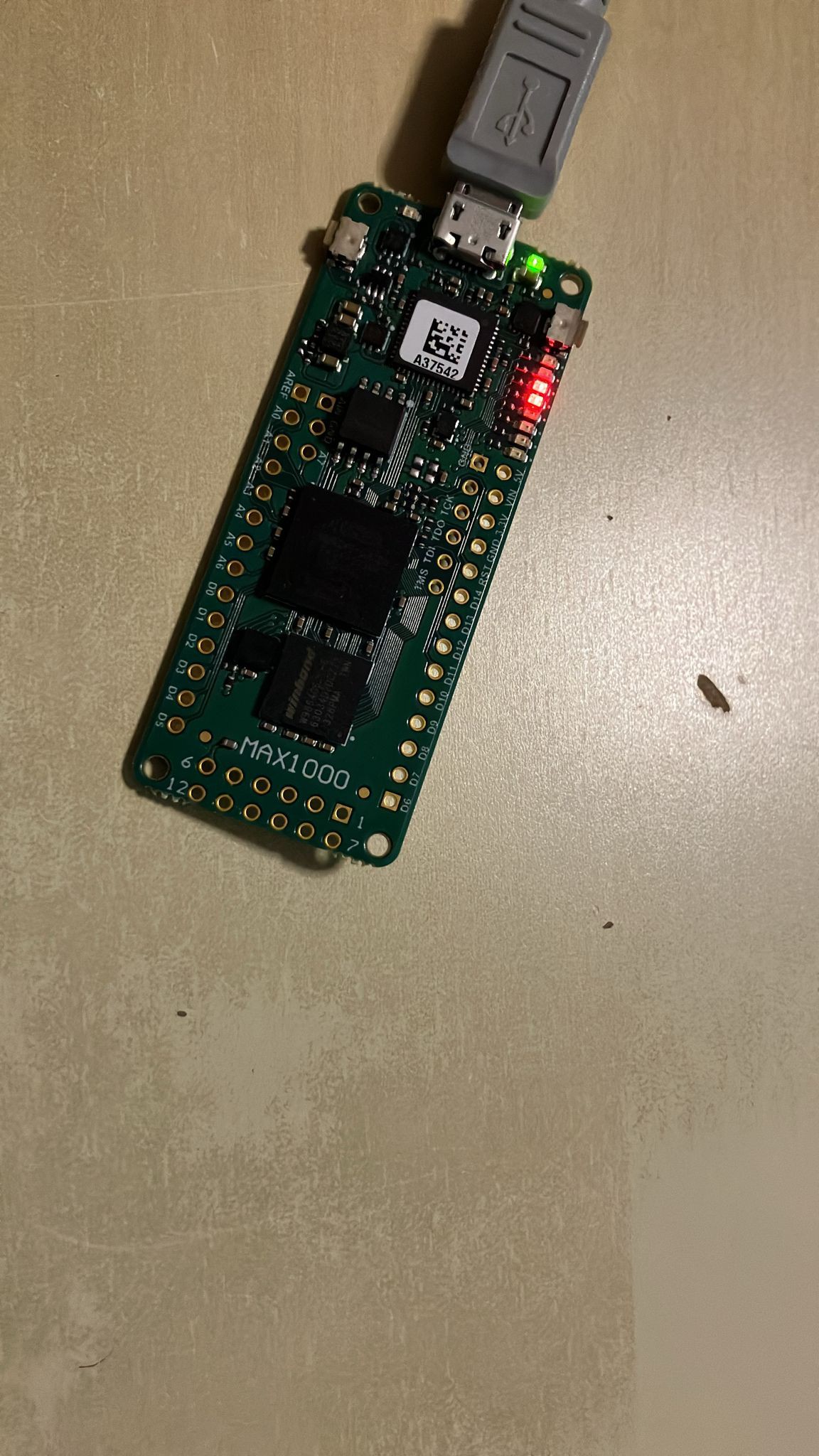

So, the following picture shows the result of my tests with the FPGA...you see a result of 12 shown by the LEDs. This is now a 12 core (yes, a 12 core) "relay CPU", each core is adding 1 to the endresult and is sending the actual value to its neighbor. Core0 is sending the result to the LEDs. Each Core has its own 1024 word memory.

And in the download area you find the VHDL code of the project...

Peter

Peter

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.