-

Started implementing the calculation of PI

5 days ago • 0 commentsIn the following video, I would like to tell you about an embarrassing mistake related to the planned calculation of pi on the relay system.

-

Release of a new video

02/07/2026 at 14:47 • 0 commentsIn this video, I’ll explain the design of the adder in my relay CPU. Even though relays are generally very slow, this adder is much faster than you might think. There is one key advantage I describe in the video.

-

Relay CPU using an FPGA as mathematical coprocessor

12/25/2025 at 10:39 • 0 commentsIn the following video, the relay system calculates the square root of 60,000 with an FPGA acting as a mathematical coprocessor. The VHDL code running on the FPGA emulates the relay system’s design, so the square-root routine is identical to the one shown in the video from a few months ago.

-

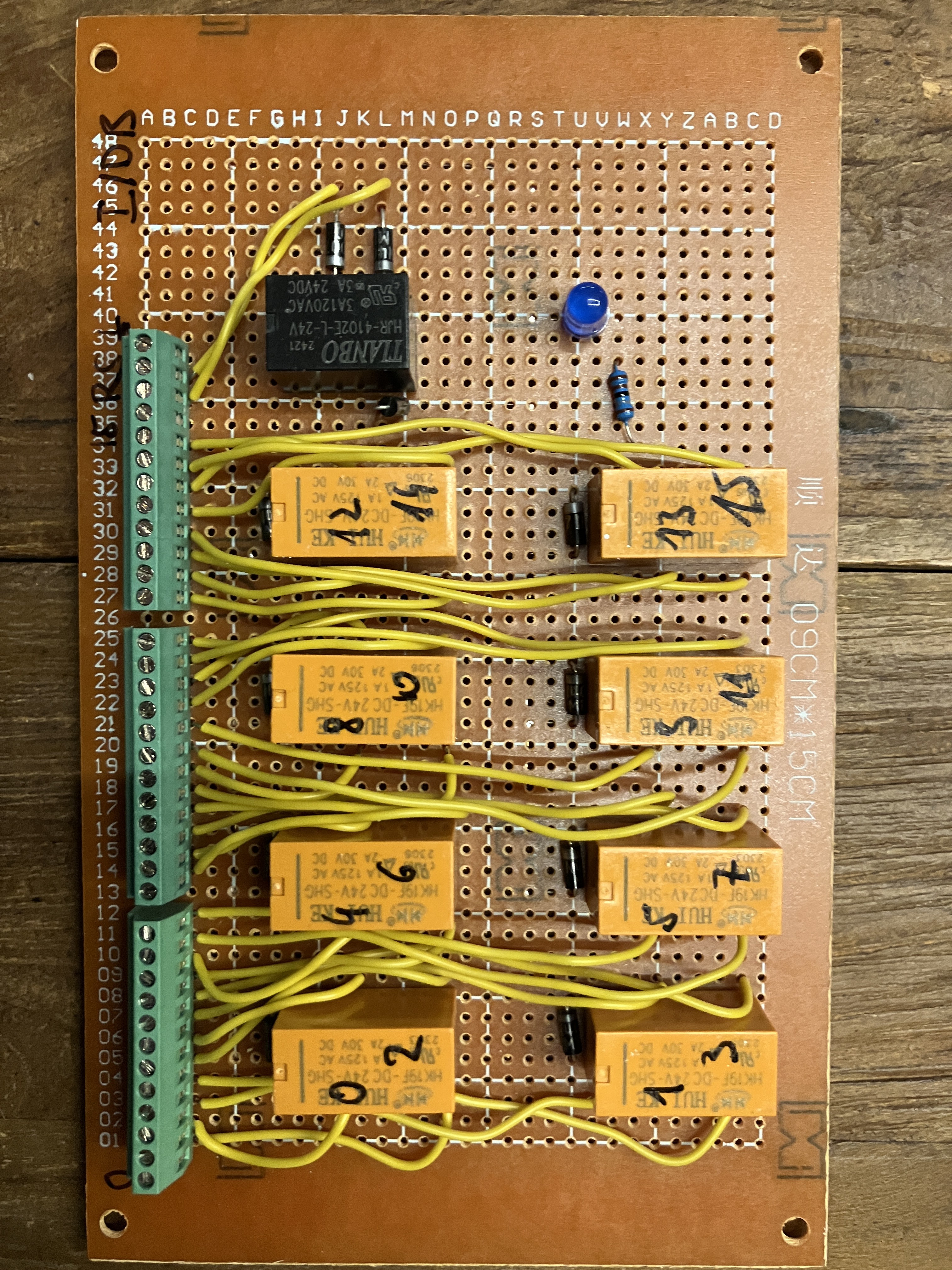

Finished 16 input ports

12/19/2025 at 05:44 • 0 commentsBecause I had to realize that using the output ports as inputs works at first glance, but causes problems on closer inspection (clearing the output register is no longer possible, because an active input may keep the holding voltage at “1”), I built a 16-port input register instead—essentially just relay-implemented switched inputs onto the data bus.

-

New FPGA board

12/02/2025 at 21:05 • 0 commentsThe new FPGA board is finished and now simulates a VHDL-based variant of the relay CPU. The large PCB serves as the interface to the 24 V relay system, and communication takes place via the system’s 16-bit I/O register.

In a first communication test, we sent an integer to the FPGA and successfully received the value multiplied by two

-

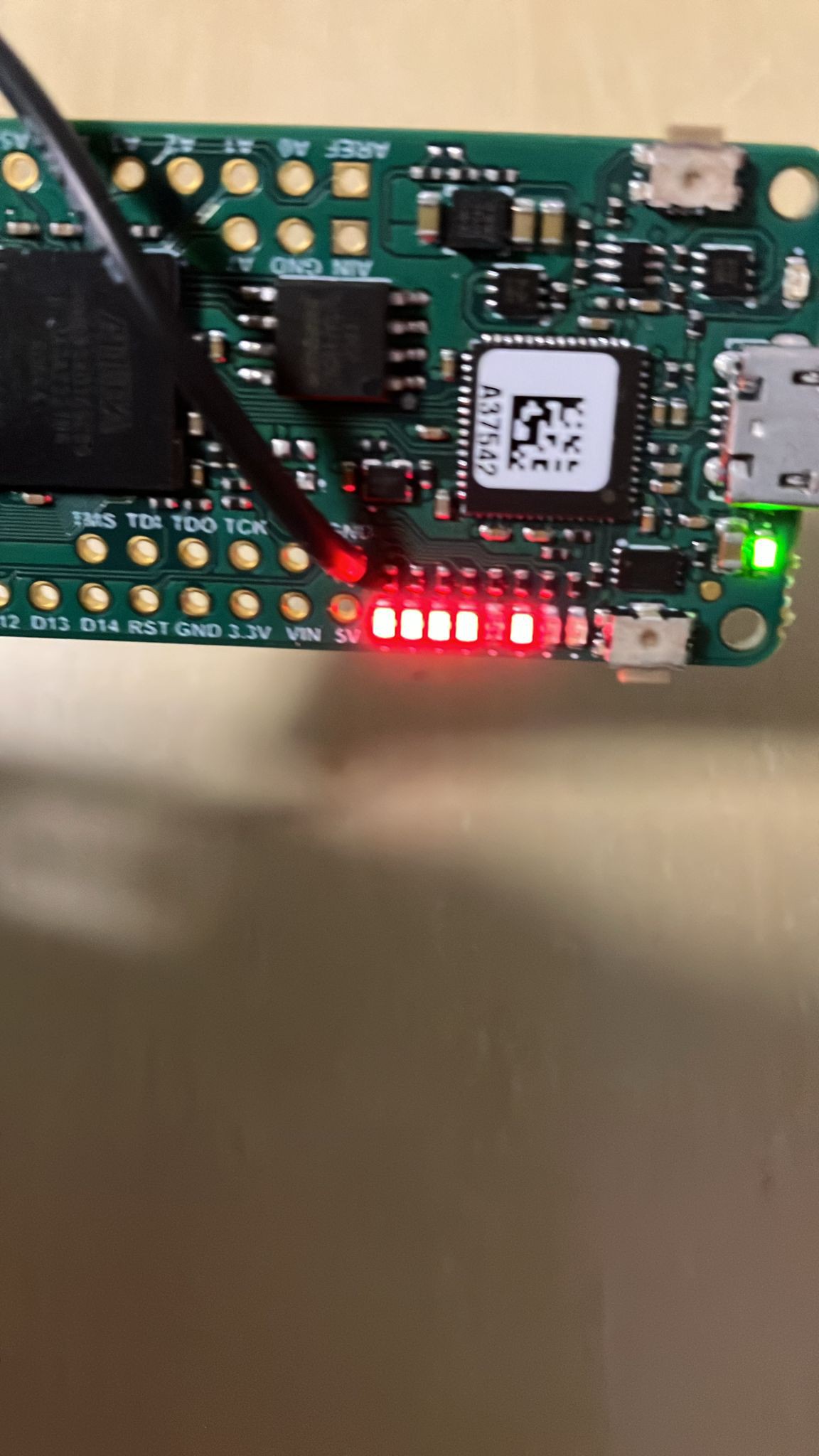

FPGA Core calculates square root

11/17/2025 at 07:01 • 2 commentsThe following picture shows the result of calculating the integer square root of 60,000: 244 (1111 0100 in binary), computed by a relay CPU core implemented in an FPGA. The program running on the FPGA is the same as the one used on the relay CPU.

The FPGA will now be connected to the I/O register of the relay system and used as a mathematical coprocessor.

![]()

-

Relay CPU writes calculation result to display

11/09/2025 at 15:00 • 0 commentsThe relay CPU calculates 156 * 67 and writes the result (=0x28D4) to the display:

-

Relay CPU reacts on user input

11/02/2025 at 10:03 • 0 commentsThe 16 bit output register is also able to act as an input register:

-

Found a second defect relay

10/27/2025 at 08:57 • 0 commentsThe following video shows how I found a second defect relay in the relay CPU:

-

Bugfixing a defect relay

10/05/2025 at 15:00 • 0 commentsThe following video shows how I found, analyzed and repaired a defect relay in the system

Homebrew 16 bit relay computer

Goal of the project is to develop and build a homebrew 16 bit relay computer

Peter

Peter